|

Projects

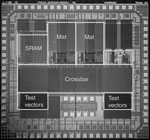

Robust Memory Design using Digital Communications Techniques

We are exploring microarchitectural and circuit-level techniques for increasting the resilience, performance, area, and power of semiconductor memories using techniques from digital communications. These techniques primarily consist of strong multi-bit error correcting codes which we can use to tolerate a number of bit-errors in a memory word without using redundant elements. We are particularly interested in how to implement strong ECC without incurring large area, power, and performance overheads. We are exploring microarchitectural and circuit-level techniques for increasting the resilience, performance, area, and power of semiconductor memories using techniques from digital communications. These techniques primarily consist of strong multi-bit error correcting codes which we can use to tolerate a number of bit-errors in a memory word without using redundant elements. We are particularly interested in how to implement strong ECC without incurring large area, power, and performance overheads.

Secure IC Design

We are developing new, low-cost, low-overhead countermeasures against invasive and non-invasive attacks for embedded systems and field-programmable gate-arrays

(FPGAs.) These include: new logic families that have constant power dissipation yet incur low area and power costs; novel memory circuits to avoid leaving remnants of past stored data; and techniques to use reconfigurability to enhance the security beyond even that dedicated custom secure ICs.

100GHz Digitial Logic using Cryogenically Cooled CMOS

In this project, we are seeking to design radically high performance digital logic using cryogenic cooling of chips built in commercial CMOS technologies. By using custom circuits and architectures tailored to low temperature operation, we can reach clock frequencies beyond 100GHz. Using such high-speed logic, applications like direct digital synthesis of RF waveforms are possible. This technology will open up a number of new application areas. In this project, we are seeking to design radically high performance digital logic using cryogenic cooling of chips built in commercial CMOS technologies. By using custom circuits and architectures tailored to low temperature operation, we can reach clock frequencies beyond 100GHz. Using such high-speed logic, applications like direct digital synthesis of RF waveforms are possible. This technology will open up a number of new application areas.

Bio-Implantable Computing Platforms

In this project, we are involved in a large multi-disciplinary research team whose goal is to design brain-implantable computing elements that can be used for disease diagnosis and treatment as well as human augmentation. The main challenge is to create computational elements that are extremely low volume and low power, yet still capable of significant computational density. We are exploring a number of implementation techniques including 3D chip stacking, computational sloppiness, and trans-threshold circuits. We are collaborating with a number of faculty at CMU and also neurosurgeons at the University of Pittsburgh.

|