Areas

Project Overview

-

RTL Design of In-order Microprocessor

RTL Design of In-order Microprocessor

In this project, I implemented a MIPS processor with an ISA covering 52 basic instructions, five-stages pipeline and employed data forwarding to handle data dependence. To deal with the control dependence, I implemented global branch predictors with 1024-entry history table and BTB.

-

RT level design of stack calculator

RT level design of stack calculator

It is a mini project on which I spent no more than one week. In the project, I designed an calculator with stack operation in systemverilog. Then I verified the design with self-made testbench.

-

Implementation of Serial Communication on FPGA

Implementation of Serial Communication on FPGA

It was a mini project. In this project, I implement serial communication between FPGAs, obtaining encrypted data from other FPGA, and implemented decryption algorithm on top ofcommunication level.

-

RT level design of Network-On-Chip(NoC)

RT level design of Network-On-Chip(NoC)

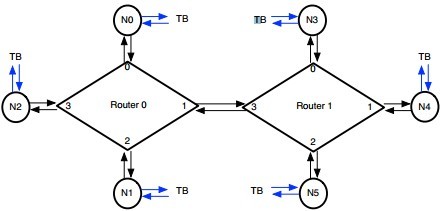

In this project, I implement a simple NoC with 2 routers and 6 network adapters. I designed the router with both input and output buffer with depth of 4 and make use of round robin to hold routing fairness. The project is done in systemVerilog

-

SystemVerilog Assertion Based Indirect Validation for Calculator

SystemVerilog Assertion Based Indirect Validation for Calculator

In this project, I carried on a black-box verification on a encrypted calculator model and found out 10 errors.

-

USB Host Design

USB Host Design

I implemented the interface of USB Host with partial USB 2.0 standard, including basic packet type of IN, OUT, DATA, ACK, NACK. I implemented CRC check, NRZI, bit stuffing, and then warp the hardware thread of reading and writing data to USB device's memory space.

-

8 bits Adder Design

8 bits Adder Design

I designed the schematics for a 8 bits ripple-carry adder in and draw layout within delay limit of 13FO4 and layout area limit of 400 µm2

-

SRAM Register File Design

SRAM Register File Design

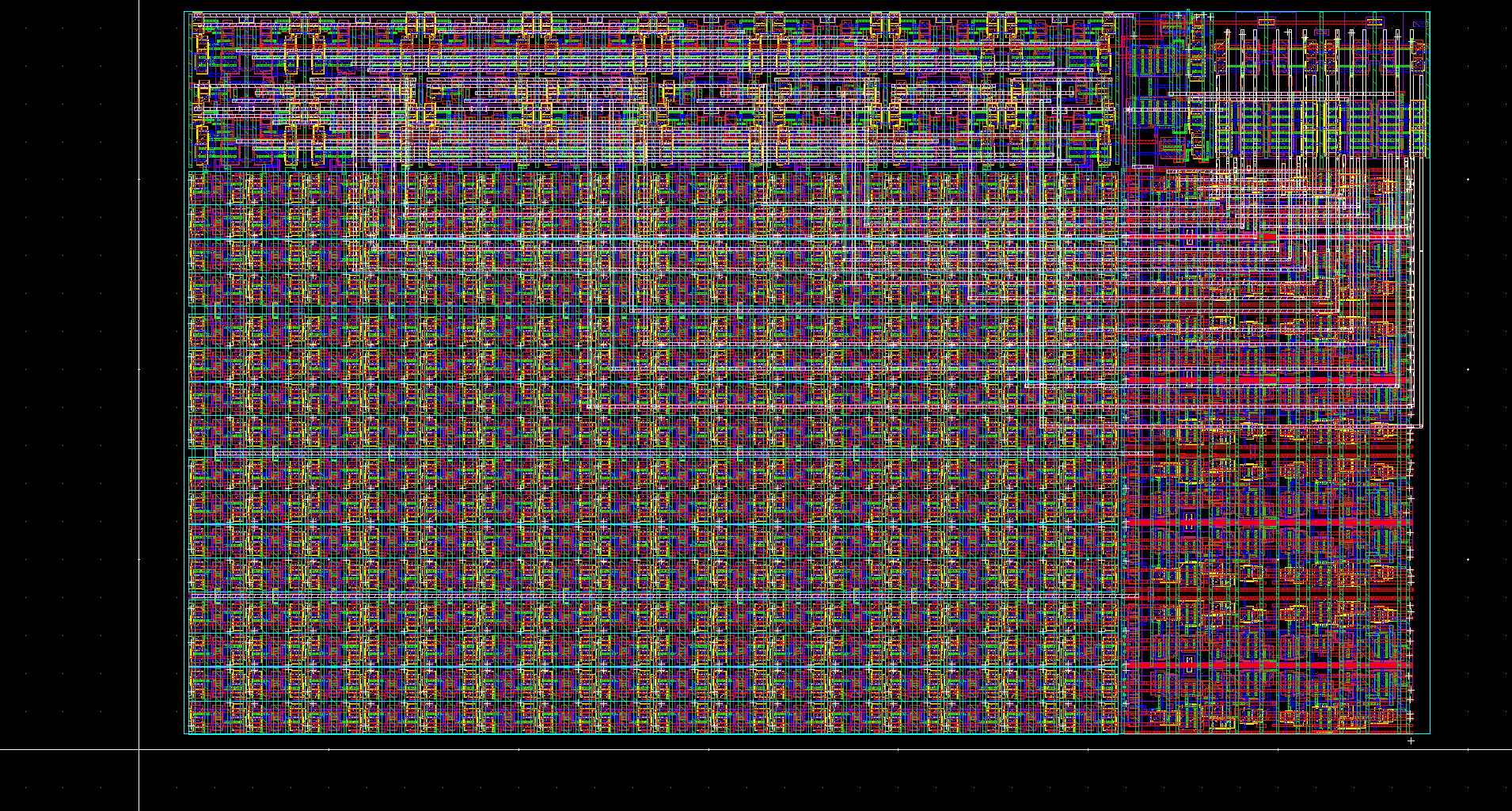

I used one month to design a 16-by-16 SRAM register file with 2 read 1 write with 45nm gbdk library.It reached the maximum frequency at 1.4 GHz in TTTT corner.I fully layouted transistors within 32umX19um boundary limit.More details is included in the project report, which is attached below.

view report -

Low Dropout Regulator Design

Low Dropout Regulator Design

In this team project, we designed schematic for a Low Dropout Regulator.It reached an open-loop gain at 35dB and 100MHz of -3dB frequency

view report -

Coding for binary design diagram(BDD)

Coding for binary design diagram(BDD)

It is a small coding assignment. I implemented the core functions a BDD tools with small basic boolean functions.

-

SAT Solver

SAT Solver

In the project, I coded the SAT solver in C language,which employed advanced algorithm such as two literal watch, to reduced complexity

-

Android App Design

Android App Design

In the project, I designed a App to help people find nearby people for car pool. I designed the UI for the app, and coded the server end.

-

Tree Leave Recognition

Tree Leave Recognition

In the project, I designed an Android App to recognize the leave of tree. I use the OpenCV as processing library and connected the OpenCV with JAVA with JNI. As final, I can detect 4 different kind of leave.

view report -

Snake Game

Snake Game

I coded this snake game for funs. If you want to run it, you need to have Visual Studio environment.

Download -

Design of Multi-core Interconnection for Merge Sort Algorithm

Design of Multi-core Interconnection for Merge Sort Algorithm

This is a semester long group project.In this project, we explored a potential implementation of merge sort that takes advantage multiple cores using network on a chip communication. We obtained the best performance in the class.

view poster -

Implementation of Cache Replacement policy using Static Re-reference Interval Prediction (SRRIP)

Implementation of Cache Replacement policy using Static Re-reference Interval Prediction (SRRIP)

I implemented a Cache Replacement policy using Static Re-reference Interval Prediction in Simplescale.