# PHYSICALLY-AWARE DIAGNOSTIC RESOLUTION ENHANCEMENT FOR DIGITAL

#### **CIRCUITS**

Yang Xue

August 2016

Department of Electrical and Computer Engineering

Carnegie Mellon University

Pittsburgh, PA 15213

**Thesis Committee:**

Ronald D. Blanton

Xin Li

Ying Zhang

Anne E. Gattiker

Jeff Schneider

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Copyright © 2016 Yang Xue

#### **Abstract**

Diagnosis is the first analysis step for uncovering the root cause of failure for a defective chip. It is a fast and non-destructive approach to preliminarily identify and locate possible defects in a failing chip. It is a software-based method that analyzes the applied tests, the failed tester response, and its netlist/layout to produce a list of diagnostic candidates that represent the locations and sometimes the behaviors/types of defects in the chip.

The conventional objective of diagnosis for identifying failure locations has been augmented with various physically-aware diagnosis techniques that are intended to improve both resolution and accuracy. Despite these advances, it is often the case, however, that resolution, *i.e.*, the number of locations or candidates reported by diagnosis, exceeds the number of actual failing locations. To address this major challenge, a novel, machine-learning-based resolution improvement methodology named PADRE (Physically-Aware Diagnostic Resolution Enhancement) is described.

PADRE uses easily-available tester and simulation data to extract features that uniquely characterize each candidate. PADRE applies machine learning to the features to identify candidates that correspond to the actual failure locations. Through various experiments, PADRE is shown to significantly improve resolution with virtually no negative impact on accuracy. Additional experiments demonstrate that PADRE is robust against data set variation and feature-data availability. Specifically, in simulation experiments, the number of defects that have perfect resolution is increased by  $5\times$  with little degradation of accuracy. Multiple silicon experiments also demonstrate similar resolution improvements.

An important investigation that typically follows diagnosis is Physical Failure Analysis (PFA). PFA is a time-consuming and destructive approach for exposing the defect in order to characterize the failure mechanisms to ultimately uncover root cause. PFA relies on an accurate and high-resolution diagnosis to locate the possible defect. In addition, however, PFA can provide information that is helpful for improving diagnosis. PADRE influences PFA within a novel, active

learning (AL) based PFA selection approach. An active-learning based PADRE (AL PADRE) selects the most useful defects for PFA in order to improve diagnostic resolution. AL PADRE uses an alternative defect selection procedure, for improving the overall accuracy and resolution of PADRE. AL PADRE is validated using both simulation and silicon-based experiments. Simulation experiments show AL PADRE can reach an accuracy of 90% with 60% less PFA, on average, compared to conventional defect selection for PFA. In the silicon experiment, by using AL PADRE, the number of chips needed to undergo PFA was reduced by more than  $6 \times$  in order to increase diagnosis accuracy by more than 20%.

During the yield learning process, the failing mechanisms that lead to defective chips may change due to perturbations in the fabrication process. It is important for PADRE to perform robustly through the entire yield learning process, therefore, additional techniques are developed to monitor the effectiveness of PADRE in real time, as well as to update PADRE efficiently and stably to cope with changing failure mechanisms. It is shown that with these additional techniques, PADRE can robustly perform through various failure mechanisms change even at early stage of the yield learning when there is insufficient diagnosis data for training.

#### Acknowledgments

Firstly, I would like to thank my supervisors Dr. Zhang Ying, Prof. Xin Li and Prof. Shawn Blanton, for their continuous support and help in this journey. I enjoy working with them, and have great respect and admiration for their insights, dedication and wisdom. I feel truly honored and fortunate to have opportunity to work with them, to know them in person and to learn from them, not only for how to advance in my study and research but also for how to become a better person.

I would like to express my gratitude to Dr. Anne Gattiker and Prof. Jeff Schneider for sitting in my PhD committee. They have shown great patience and understanding to me through many ups and downs. I really want to thank them for taking time from their busy schedules to follow up on my research and to provide many valuable suggestions and feedbacks.

I also want to express my gratitude to A\*STAR, Singapore for their financial support, I greatly appreciate their trust on me and their continuous support since even before I embarked on this journey more than six years ago. Without their support, I would never have had this great opportunity to realize my dream and to explore what I love to do.

Last but not least, I cannot express enough how grateful I am to all my friends and family who have supported me through all these years. Some of them help me with my research by answering many stupid questions from me, some of them support me emotionally when I am down, but above all, all of them share their life with me - their happiness, love and sorrow. I want to thank them for allowing me to be part of their amazing life.

## **Contents**

| 1 | Intr | duction                            | 1 |

|---|------|------------------------------------|---|

|   | 1.1  | PADRE                              | 7 |

|   | 1.2  | AL PADRE                           | 7 |

|   | 1.3  | Changing Failure Mechanisms        | 8 |

|   | 1.4  | Dissertation Organization          | 9 |

| 2 | Bacl | ground 1                           | 1 |

|   | 2.1  | Defects and Faults                 | 1 |

|   | 2.2  | Diagnosis                          | 2 |

|   |      | 2.2.1 Cause-Effect Diagnosis       | 5 |

|   |      | 2.2.2 SSL Faults                   | 5 |

|   |      | 2.2.3 Bridge Faults                | 6 |

|   |      | 2.2.4 Transistor Stuck-Open Faults | 8 |

|   | 2.3  | Per-Test Diagnosis                 | 9 |

|   | 2.4  | Summary                            | 1 |

| 3 | PAD  | RE 2                               | 3 |

|   | 3.1  | The PADRE Methodology              | 3 |

|   |      | 3.1.1 Candidate Features           | 3 |

|   |      | 3.1.2 Classifier Structure         | 8 |

|   |      | 3.1.3   | Feature Selection                   | • | 31 |

|---|------|---------|-------------------------------------|---|----|

|   | 3.2  | Experi  | iment with Simulation Data          |   | 32 |

|   |      | 3.2.1   | Setup                               |   | 33 |

|   |      | 3.2.2   | Fisher Score                        |   | 33 |

|   |      | 3.2.3   | Sequential Forward Selection        |   | 34 |

|   |      | 3.2.4   | Resolution Improvement and Accuracy |   | 38 |

|   |      | 3.2.5   | Dataset-Size Sensitivity            |   | 39 |

|   | 3.3  | Experi  | iments with Silicon Data            |   | 41 |

|   | 3.4  | Compu   | utational Cost                      |   | 46 |

|   | 3.5  | Summ    | ary                                 |   | 47 |

| 4 | AL l | PADRE   |                                     |   | 49 |

|   | 4.1  | AL PA   | ADRE Methodology                    |   | 49 |

|   |      | 4.1.1   | Discrepancy Check                   |   |    |

|   |      | 4.1.2   | Within-Margin                       |   |    |

|   |      | 4.1.3   | Stopping Criteria                   |   |    |

|   |      | 4.1.4   | Implementation                      |   | 55 |

|   | 4.2  | Simula  | ation Experiments                   |   | 57 |

|   |      | 4.2.1   | Setup                               |   | 59 |

|   |      | 4.2.2   | Results                             |   | 60 |

|   | 4.3  | Silicon | n Experiment                        |   | 63 |

|   | 4.4  | Summ    | ary                                 |   | 64 |

| 5 | Cha  | nging F | Failure Mechanisms                  |   | 71 |

| J |      | 0 0     |                                     |   |    |

|   | 5.1  |         | acy Tracking                        |   |    |

|   | 5.2  |         | ring Failure Mechanisms Training    |   |    |

|   | 5.3  |         | Dataset Training                    |   |    |

|   | 5.4  | Experi  | iments                              |   | 75 |

| Bil | bliogi | raphy   |                                     | 91 |

|-----|--------|---------|-------------------------------------|----|

|     | 6.2    | Future  | Work                                | 88 |

|     | 6.1    | Disser  | tation Contribution                 | 85 |

| 6   | Sum    | ımary a | nd Future Work                      | 85 |

|     | 5.5    | Summ    | ary                                 | 83 |

|     |        | 5.4.4   | Cross-Dataset Training              | 81 |

|     |        | 5.4.3   | Changing Failure Mechanism Training | 78 |

|     |        | 5.4.2   | Accuracy Tracking                   | 77 |

|     |        | 5.4.1   | Setup                               | 75 |

## **List of Figures**

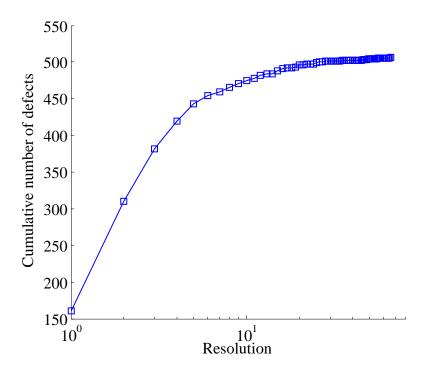

| 1.1 | The cumulative diagnostic resolution distribution of defects from a commercial       |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | chip shows that only 161 or 31.8% of a population of 507 defects have ideal          |    |

|     | resolution. The plot sorts the defects by the number of candidates for each de-      |    |

|     | fect. Each point on the plot shows the number of defects in the entire population    |    |

|     | that have candidates no greater than a certain number, ranging from one to the       |    |

|     | maximum number of candidates for a single defect                                     | 4  |

|     |                                                                                      |    |

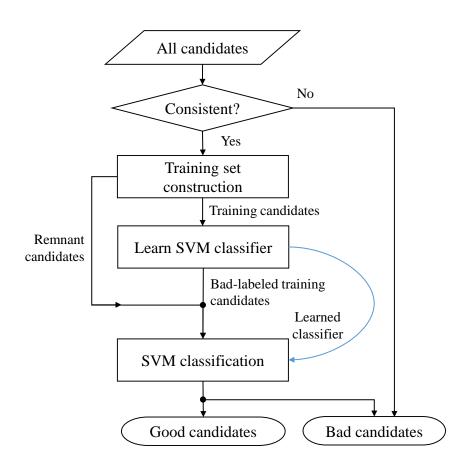

| 3.1 | PADRE takes all the candidates through a two-level classifier, in which incor-       |    |

|     | rect candidates are eliminated and correct candidates are identified. By reducing    |    |

|     | the total number of candidates while maintaining accuracy, the resolution of the     |    |

|     | diagnosis is improved                                                                | 24 |

|     |                                                                                      |    |

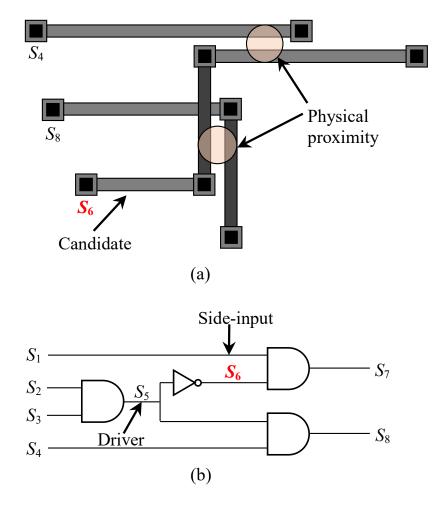

| 3.2 | Example of the neighborhood of a candidate associated with net $S_6$ : (a) the phys- |    |

|     | ical neighbors, i.e., nets in close physical proximity of the candidate and (b) the  |    |

|     | driver and receiving-cell side inputs of the candidate                               | 26 |

|     |                                                                                      |    |

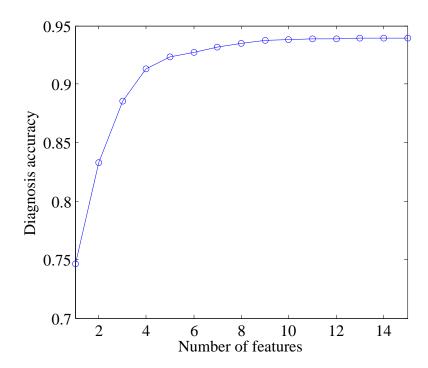

| 3.3 | The diagnosis accuracy improves following the addition of each selected feature.     |    |

|     | The accuracy plot shows a sharp increase with the addition of the top few fea-       |    |

|     | tures. As more features are selected, the accuracy increase slows and eventually     |    |

|     | saturates before all the features are selected                                       | 37 |

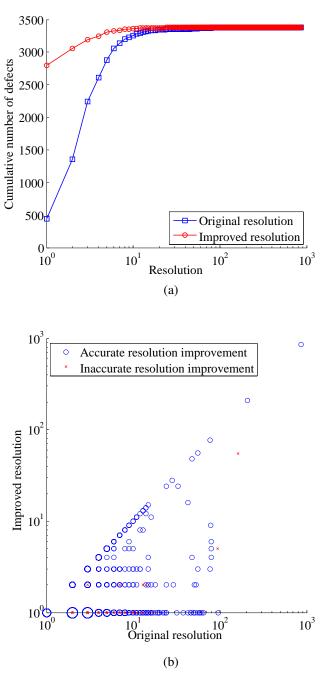

| 3.4 | (a) Resolution improvement through PADRE at the defect level shows that the               |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | number of defects exhibiting ideal resolution is increased by more than $5\times$ . (b)   |    |

|     | Each defect is plotted according to its improved resolution versus its original res-      |    |

|     | olution. Defects with accurate resolutions are marked with blue circles, whereas          |    |

|     | defects with inaccurate resolutions are marked with red crosses. The accuracy is          |    |

|     | maintained for 3,249 or 99.2% of all defects. Bubble size is proportional to the          |    |

|     | number of defects with the corresponding original/improved resolution                     | 40 |

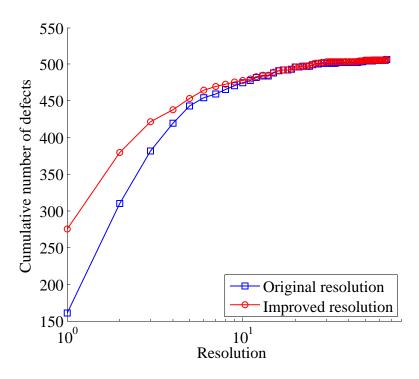

| 3.5 | Resolution improvement for the first silicon data set shows the number of defects         |    |

|     | that exhibit ideal resolution is increased by 77.6%                                       | 44 |

| 3.6 | Resolution improvement for the second silicon data set shows that the number of           |    |

|     | defects exhibiting ideal resolution is increased by nearly $2\times\ldots\ldots$          | 46 |

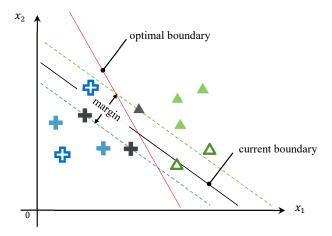

| 4.1 | Two data sets (crosses and triangles) are plotted with respect to two features,           |    |

|     | $x_1$ and $x_2$ . Solid crosses and triangles are labeled training data from two classes, |    |

|     | while unfilled crosses and triangles are unlabeled data. The support vectors (grey        |    |

|     | crosses and triangles) define the current boundary and its margin. Labeling the           |    |

|     | unlabeled data within the margin leads to a new, optimal boundary                         | 53 |

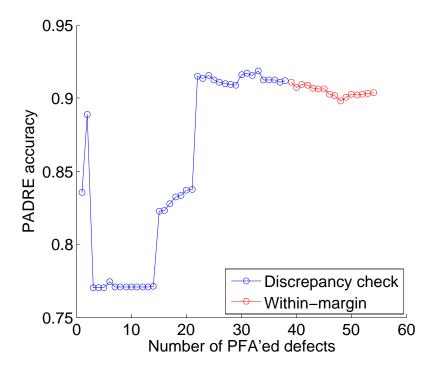

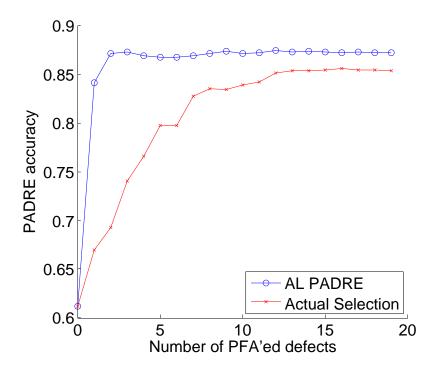

| 4.2 | PADRE accuracy versus the number of PFA'ed defects selected by AL PADRE.                  |    |

|     | The initial accuracy is 77.0%                                                             | 61 |

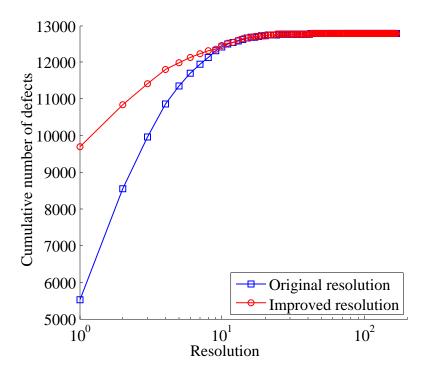

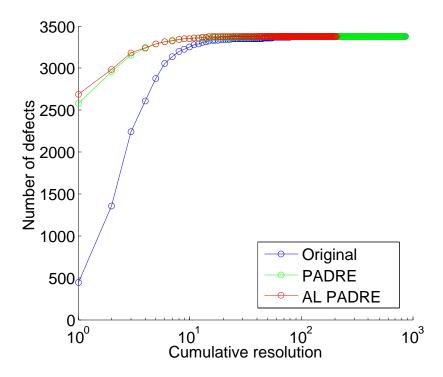

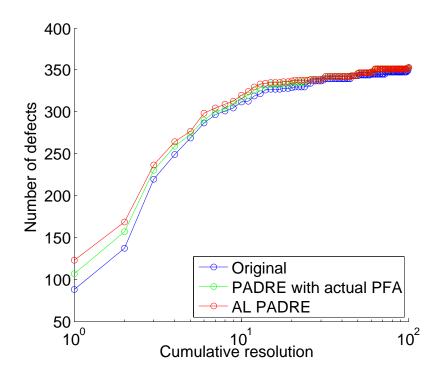

| 4.3 | The cumulative diagnostic resolution distribution shows that PADRE improves               |    |

|     | the number of defects with ideal resolution by more than $5\times$ over the original      |    |

|     | resolution, and AL PADRE further improves the number by 107. Each point on                |    |

|     | the plot shows the number of defects that have a total number of candidates no            |    |

|     | greater than the given cumulative resolution                                              | 62 |

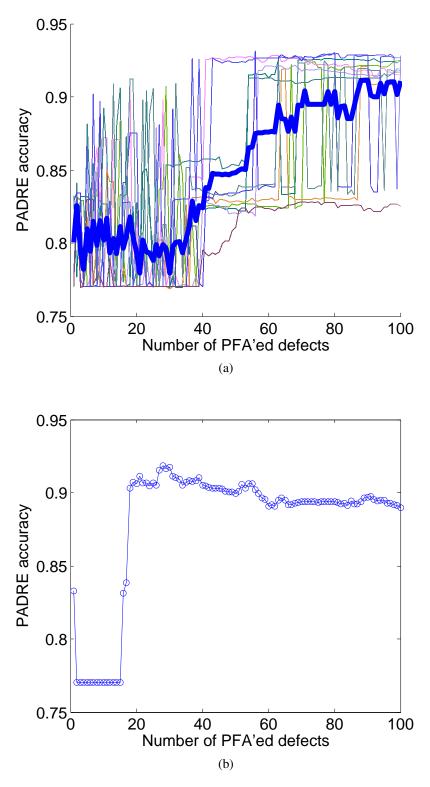

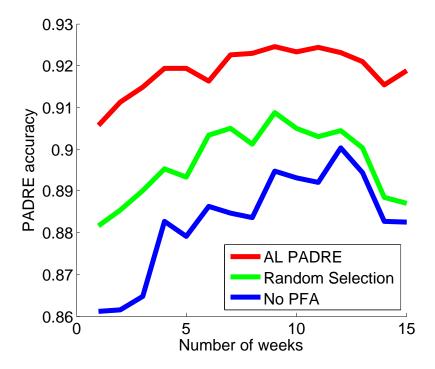

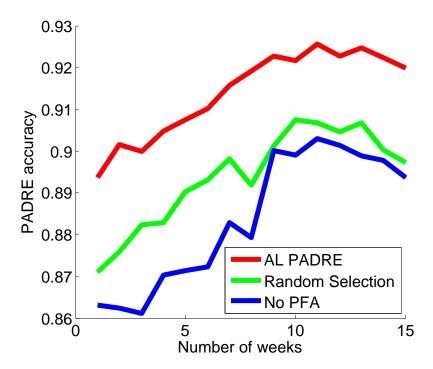

| 4.4 | PADRE accuracy versus the number of PFA'ed defects selected by (a) random                 |    |

|     | selection and (b) AL PADRE. For random selection, the average accuracy of the             |    |

|     | 100 experiments is plotted as a bold blue curve. The initial accuracy is 77%              | 65 |

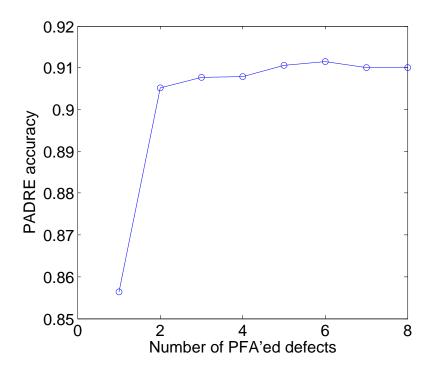

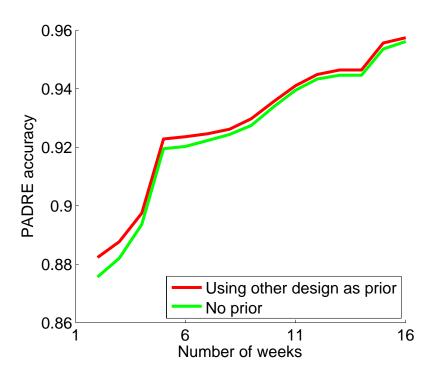

| 4.5 | PADRE accuracy versus the number of PFA'ed defects selected by AL PADRE            |    |

|-----|------------------------------------------------------------------------------------|----|

|     | when defects are selected without the five-candidate restriction                   | 66 |

| 4.6 | PADRE accuracy versus the number of weeks of PFA using three different pro-        |    |

|     | cesses, namely, PFA with AL PADRE, PFA with random selection and no PFA.           |    |

|     | Note that the first four weeks of accumulation is not shown in the plot, as no PFA |    |

|     | is performed during that period.                                                   | 67 |

| 4.7 | PADRE accuracy versus the number of weeks of PFA using three different pro-        |    |

|     | cesses, namely, PFA with AL PADRE, PFA with random selection and no PFA.           |    |

|     | Note that there is no accumulation in this setup, all three start from week one    | 68 |

| 4.8 | PADRE accuracy versus the number of PFA'ed defects for selection using AL          |    |

|     | PADRE and actual selection made by industry. The initial accuracy is $61.2\%$      | 69 |

| 4.9 | The cumulative diagnostic resolution distribution shows PADRE with actual PFA'ed   |    |

|     | defects increases the number of defects with ideal resolution from 88 to 107, and  |    |

|     | using AL PADRE can instead improves the number to 123. Each point on the plot      |    |

|     | shows the number of defects that have a total number of candidates no greater      |    |

|     | than the given cumulative resolution                                               | 70 |

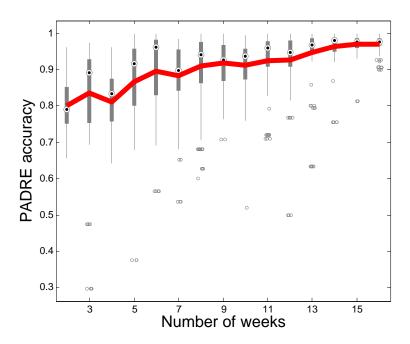

| 5.1 | The accuracy tracking shows steady increase despite the variance on defect com-    |    |

|     | position (as shown in Table 5.2)                                                   | 78 |

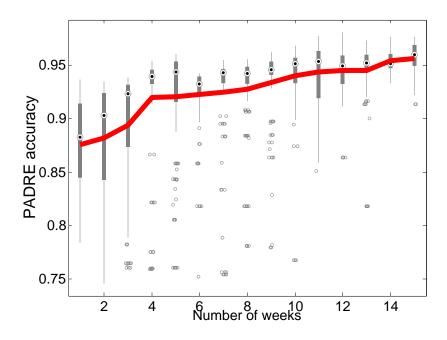

| 5.2 | The PADRE accuracy of using a cross-validated weight                               | 80 |

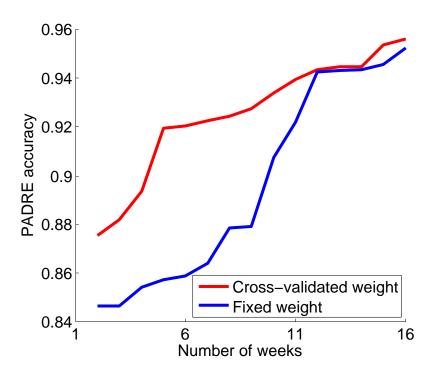

| 5.3 | The average accuracy using cross-validated weight consistently outperforms that    |    |

|     | of using a fixed weight of 20                                                      | 81 |

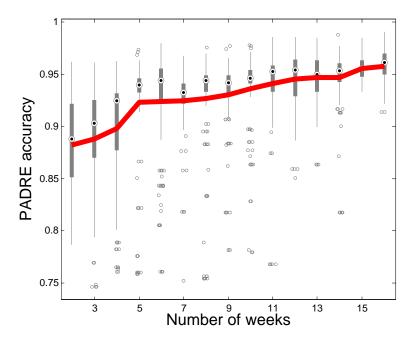

| 5.4 | The accuracy of using cross-validated weight to combine training data from two     |    |

|     | different designs                                                                  | 82 |

| 5.5 | The average accuracy with combined training data slightly but consistently out-    |    |

|     | performs that of using training data from a single design.                         | 83 |

## **List of Tables**

| 3.1 | List of Features Considered in PADRE                           | 25 |

|-----|----------------------------------------------------------------|----|

| 3.2 | Faults Injected in Failing Chips                               | 34 |

| 3.3 | Fisher Scores for Synthetic Data                               | 35 |

| 3.4 | Sequential Forward Selection of the Features                   | 36 |

| 3.5 | PADRE Candidate-level Classification Statistics                | 39 |

| 3.6 | Dataset Sensitivity Analysis with Reduced Subsets for Training | 42 |

| 3.7 | Resolution Improvement of PFAed Failing Chips                  | 45 |

| 4.1 | Discrepancy Check                                              | 52 |

| 4.2 | Faults Types Injected into the ASIC Design                     | 59 |

| 5.1 | Faults Types Injected into the ASIC Design                     | 76 |

| 5.2 | Faults Types of Failed Chip for Each Week                      | 76 |

| 5.3 | Cross-validated weight and accuracy                            | 79 |

## **Chapter 1**

#### Introduction

The semiconductor industry has undergone an explosive development in the past few decades, and revolutionized the way people live in the process. The technology node of integrated circuits (IC) has shrunk from  $10\mu m$  in 1971 to 10 nm in 2016, with billions of transistors now packed in a typical chip that powers our smart phones [1]. For decades, the scaling of transistors, driven by Moore's Law, has brought down the cost of semiconductor manufacturing, however, as the the technology node advances beyond 10 nm, it becomes evident that further scaling can no longer reduce the cost, as it becomes increasingly difficult to manufacture smaller features. In addition to the manufacturing cost, the testing of the chips also becomes more and more costly, which further shrinks the profit margin of the semiconductor industry [2]. Albeit costly, the testing is an indispensable step in the production. Considering the extremely delicate structure, the complexity of the manufacturing process, and the inherit process variation, it is of no surprise that some manufactured products may be defective. Testing filters out the defective products and safeguards the correct functionality and performance of the shipped products.

Under such circumstance, it is apparent that any defective products that cannot be shipped cut into the profit margin of the production, which is already thin. To ensure the profitability of a product, maintaining a profitable *yield* becomes extremely crucial. Yield is the percentage of manufactured products that function correctly as designed. It is not uncommon for a newly-

introduced design to experience low yield in the early stages of production. It is therefore critical to improve yield as quickly as possible, and a fast yield ramp in turn heavily depends on the ability to accurately and precisely uncover the root-cause of the defective products.

Diagnosis is a fast and non-destructive approach to identify and locate defects in a failing chip [3]. It is a software-based method that analyzes the applied tests, the chip tester response, and the netlist/layout to produce a list of scored diagnosis *candidates* that represent the locations and sometimes behaviors/types of defects within the failing chip. A candidate is different from a defect (*i.e.*, the actual physical deformation that leads to malfunction), in that it is only a representation of the likely location and behavior of a defect.

Many diagnosis techniques identify candidates by comparing the collected tester response of a failing chip with the fault simulation responses for a specific set of deduced faults using the same test patterns, i.e., applied inputs for the test. If an exact match is found, a diagnosis with an ideal resolution is produced. However, an exact match is not common, meaning that there is often mismatch between the simulation response and the tester response. When an output or test pattern that passes on the tester is predicted by the fault model to fail, a mismatch called a Tester Pass Simulation Fail (TPSF) results; similarly, when a fault predicts an output or test pattern to pass which turns out to fail on the tester, it is called a Tester Fail Simulation Pass (TFSP). For matching responses, where an output or test pattern pass or fail both on the tester and in fault simulation, a Tester Pass Simulation Pass (TPSP) or a Tester Fail Simulation Fail (TFSF) results, respectively. To quantitatively evaluate the extent of match and mismatch of various candidates, a ranking method is typically invoked (e.g., in [4]), where a normalized score is assigned to each candidate based on the weighted sum of the matches and mismatches. A diagnosis outcome with few candidates (i.e., good resolution) and very high scores are assumed to correlate with the actual defect(s) that caused failure.

Much effort has been dedicated to improving diagnosis because it is an important part of the yield-learning process for understanding the root cause of failure. Diagnosis can be followed by physical failure analysis (PFA), a time-consuming and destructive approach for exposing the

defect physically in order to characterize the failure mechanisms [5]. Due to the high cost and destructive nature of PFA, the accuracy and resolution of diagnosis is of critical importance.

In addition to being an integral part of PFA, diagnosis results from a population of failing chips also serve as input for a variety of analyses besides PFA. For instance, volume diagnosis can reveal important statistics including the defect distribution or the primary yield detractors [6, 7], and provide useful feedback for evaluating and improving the quality of manufacturing test [7, 8, 9].

In practice, diagnosis tends to be non-ideal for a variety of reasons. Two such reasons include the limitation on test set size, and the equivalent circuit I/O behavior that inherently exists among candidates. Because there is a trade-off between the time needed to both create and apply tests, and the cost of test, it is always the case that not all possible defects are fully exposed when they are detected by the production test set. Even if a comprehensive test set is economically viable, there still can be candidates that have equivalent behavior among the many locations that are specific to the standard cells used and their interconnections. Also, the fault models adopted for both test and diagnosis are not perfect either, meaning it is quite likely that the actual defective behavior cannot be fully explained by the fault model(s) adopted [10]. The overall result is an imperfect diagnosis that typically produces an accurate result but a non-ideal resolution. Here, a diagnosis is accurate if the true defect location is included in the reported candidate list, whereas the resolution is the total number of candidates reported for each defect. The diagnosis outcome is considered *ideal* if and only if the resolution equals to one and it is accurate. However, diagnosis often reports more than one candidate for a defect, where one very likely corresponds to the actual defect whereas the remaining do not. Figure 1.1 illustrates this point by showing the cumulative diagnostic resolution of defects from a commercial chip. It can be seen that just over 30% of the diagnosed defects exhibit ideal resolution.

It is possible to improve resolution with add-on techniques that rely primarily on easilyobtainable data. In particular, resolution improvement can be accomplished through the derivation of characteristics that enable *correct* candidates (candidates that correctly represent defect

Figure 1.1: The cumulative diagnostic resolution distribution of defects from a commercial chip shows that only 161 or 31.8% of a population of 507 defects have ideal resolution. The plot sorts the defects by the number of candidates for each defect. Each point on the plot shows the number of defects in the entire population that have candidates no greater than a certain number, ranging from one to the maximum number of candidates for a single defect.

locations) to be distinguished from *incorrect* ones (candidates that do not). For instance, the candidate scoring technique mentioned earlier is a proven approach for separating correct and incorrect candidates. For example, in [11, 12], it is suggested that a candidate detected by many tester-passing patterns is less likely to correlate to the actual defect location. Other work reveals that the same neighborhood state (*i.e.*, the logic state of nets near the candidate) for a correct candidate should not be observed for both TPSF and TFSF patterns [13, 14, 15]. If such a situation occurs, the candidate is said to be *inconsistent* and is likely to be incorrect [13, 14, 15]. For example, in [15], it is reported that on average 64% of the incorrect candidates are correctly identified through a check of consistency; and in [14], population of the incorrect candidates are reduced by 62%. Although these techniques are effective in identifying candidates that are likely to be incorrect, they do not directly identify correct candidates. This somewhat limits their overall improvement in resolution, particularly for defects with a large number of candidates. In such cases, even if some of the incorrect candidates are eliminated, without a means to directly identify the correct candidate among the set of all candidates, the resolution may still not be sufficient for practical PFA or other follow-on analyses.

Other than directly improving the diagnosis algorithm itself, other approaches have been reported for improving resolution. Diagnosis-oriented ATPG has drawn considerable work. For example, in [16], the authors introduce a transistor-level and defect-based ATPG for more precise test and diagnosis; in [17], the authors use fault-distinguishing ATPG to create tests that specifically detect a targeted fault without activating other faults. In [18], the authors describe an approach that directly targets faults that are derived from a physically-aware diagnosis. In [18], the correct candidates of 31% of the defects are successfully identified, whereas in [17], 97.4% of the correct candidates are successfully identified. However, the diagnostic APTG typically targets at distinguishing a pair of two candidates at a single time. Therefore, for defects with more than two candidates, the diagnostic ATPG typically involves iterative testing and test pattern generation cycles to incrementally distinguish all the faults, which causes additional test-generation time and cost.

Machine learning (ML) techniques have also been used in diagnosis, especially in various volume diagnosis approaches. In [19], the authors use a two-step approach consisting of rules and a classifier to identify bridge defects from a population of diagnosed failures. In [20], a classifier that takes the tester response as input is used to predict the fanout-free sub-circuit that most likely contains a defect. Other ML-based diagnosis approaches deal with resolution improvement more directly. In [21], the authors use an incremental *k*-nearest neighbors classifier to improve resolution of an on-chip diagnosis technique meant to identify a failing sub-circuit. In [22], a technique called RCD (root cause deconvolution) uses a Bayesian classifier to determine the defect type responsible for failure, (*e.g.*, opens at certain metal layers, bridges, or cell-level defects). RCD indirectly improves resolution by eliminating candidates that are not associated with the defect type identified by RCD. In [23], the authors describe a technique called DREAMS (DFM rule evaluation using manufactured silicon), where Expectation-Maximization technique is used to identify the DFM (design for manufacturability) rule violation responsible for failure. Similar to RCD, DREAMS improves diagnostic resolution by disregarding candidates that are not associated with the violated rule.

The issue with ML-based techniques mainly lies in the data required to learn the model. For example, in [22], in addition to the conventional test and diagnosis data, detailed layout and fabrication data are also required, which may limit the applicability of the technique. In [20], the classifier is trained with simulation data with injected virtual faults, which raises doubt about the quality of the training data, especially considering the fact that the actual tester responses of defective chips are increasingly difficult to explain with any single fault model [6].

This work attempts to contribute to the effort of improving diagnostic resolution with an easy-to-implement approach that does not require additional testing or physical analysis. We attempt to perform data mining on the easily-available diagnosis data, and try to extract information that are not directly visible in the original data to help improve resolution.

#### 1.1 PADRE

PADRE (Physically-Aware Diagnostic Resolution Enhancement) [24] improves diagnostic resolution through the use of Machine Learning (ML). Specifically, candidate-specific features are derived to characterize and distinguish the diagnosis candidates. Some of the features are well established such as TFSP, TPSF, and TFSF. Some others are new, established in this thesis for characterization of more sophisticated candidate properties. The feature data from a population of candidates are used to learn a classifier that separates correct candidates from incorrect ones.

In PADRE, we employ a two-level classifier. The first level is a simple rule-based check of the neighborhood consistency of each candidate, which is very adept at identifying some types of incorrect candidates [3, 7, 13, 14, 15]. The second level uses an SVM (support vector machine) [25] classifier that is learned from some of the candidates that pass the first level to predict which candidates are correct. PADRE essentially improves the diagnostic resolution through the process of incorrect-candidate elimination and correct-candidate identification.

#### 1.2 AL PADRE

Considering the limited resources for PFA against the vast number of failed chips, the question of which chip, and more specifically, which defect, should be selected for PFA becomes a tricky one. Note that although each failed chip may contain multiple defects, typically only one of the defects can be investigated by PFA, due to its inherently destructive nature. To help identify the most valuable defect for PFA, we describe an active learning-based methodology that can be implemented in conjunction with PADRE to select the most informative defect for resolution improvement. Active learning (AL) has been shown in many other applications to improve the accuracy of classification. It has seen wide application in text classification, image recognition, and early disease diagnosis [26, 27, 28]. AL sequentially queries the label of certain unlabeled data instances for the purpose of improving classification accuracy through improved training

data.. An AL algorithm selects the most informative instance based on pre-set criteria that best suit the application. For diagnostic resolution improvement, however, successful PFA of a defect can reveal labels (correct or incorrect) of multiple instances ( *i.e.*, all the reported candidates)<sup>1</sup>. To leverage this batch-mode property, we adopt and combine both the conventional AL selection criterion, and a novel selection criterion specifically based on the diagnosis application. The two methods are named *within-margin* and *discrepancy check*, respectively. It is shown through experiments that the two methods are very powerful in improving the accuracy of classification, because they both avoid selecting defects that are already correctly labeled by the existing classifier.

#### 1.3 Changing Failure Mechanisms

As with any machine learning based technique, the performance of PADRE is influenced by the quality of the training data, *i.e.*, whether the training data can properly represent the actual data being analysed. The training data of PADRE are extracted from the diagnosis data, which are the result of certain defects within the failed chips. In the yield-learning process, as the production changes, it is possible that the failure mechanisms may change. It is important that PADRE is able to adapt to the changing failure mechanisms to ensure its accuracy throughout its deployment.

To address this need, an accuracy tracking method is proposed. Accuracy tracking works by applying the existing classifier to some of the latest diagnosis data, of which the labels can be inferred heuristically. Then to update the classifier with the latest diagnosis data, the latest training data is weighted, so that the updated classifier can produce best possible accuracy for the most current diagnosis data.

PADRE extracts training data from the diagnosis data themselves using effective heuristics.

<sup>&</sup>lt;sup>1</sup>Successful PFA of a defect reveals the labels of all candidates associated with a defect because success implies the root-cause has been identified which in most cases the location, and thus the correct candidate has been identified. While one can probably cite rare cases where this would not be true, we ignore such possibilities in this thesis.

Although this approach is shown to be very reliable for constructing high quality training sets, the amount of training data that can be extracted is limited by the total diagnosis data available. When the available diagnosis data are limited, which may happen in the early stage of the yield-learning process, the amount of high-quality training data is consequently limited. A straightforward solution to this situation is to accumulate the diagnosis data until sufficient training data can be extracted, which hinders the yield learning process, as the application of PADRE has to be delayed until sufficient diagnosis data are accumulated.

Another approach to address the lack of data is the use of diagnosis data from other designs. The fact that it is possible to make prediction on a population of diagnosis data by learning a classifier from the diagnosis data of a different design implies that the features used by the classifier are somewhat design-independent. When combining the diagnosis data of two different designs, the key question is how to balance the weight of the data from the two different designs. Intuitively, if there are a sufficiently large amount of diagnosis data available for the targeted design, PADRE should be primarily trained using that. On the other hand, if there is limited diagnosis data from the targeted design, PADRE should rely less on its diagnosis data. Similar to the weighting proposed for handling changing failure mechanisms, weighting is proposed to balance the training data from different designs, so that the PADRE is accurate for predicting candidates from the targeted design.

#### 1.4 Dissertation Organization

The rest of the dissertation is organized as follows: Chapter 2 provides the fundamental for testing and diagnosis; Chapter 3 describes the PADRE technique with a comprehensive study on its resolution improvement capability and analysis of its application under different scenarios; Chapter 4 shows how AL PADRE leverages PFA for significantly increasing the accuracy of PADRE; Chapter 5 describes a number of techniques that help PADRE cope with changing failure mechanisms issues that can occur in the yield learning process; finally Chapter 6 summarizes

| major conclusions and contributions of this dissertation, and discusses areas for future work. |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

|                                                                                                |

## **Chapter 2**

## **Background**

#### 2.1 Defects and Faults

A defect is a physical deformation that changes the circuit structure and/or material properties of the chip. Failing outputs due to a defect result from errors on one or more signal lines upon application of certain test patterns to the Circuit under Test (CUT). Logical fault models are used to capture the logic-level misbehavior of defects. A fault is one instance of a fault model, representing a possible location of the modeled defect. Specifically, a fault represents when and where an error appears upon test application. For example, the single stuck-line (SSL) model, which is the most commonly used fault model, assumes that only one signal line can be permanently stuck at either 0 or 1 [29, 30, 31]. This means, for an SSL fault l/v, where l is one signal line in a CUT, l has an incorrect value v for every test-pattern that drives l to the logic-value v. Similar to the notion of test pattern response, fault-simulation response for a given fault is defined as the output response produced by the CUT in simulation after applying a given test pattern in the presence of the fault. Correspondingly, fault-simulation response is the set of fault simulation pattern responses for the applied test set. A fault is said to *explain* a test pattern  $t_i$  if the fault simulation pattern response is identical to the test pattern response for  $t_i$ .

Another frequently used fault type is the bridge fault [32]. It models the behavior of unwanted

connections between two or more lines. Depending on the nature of the connection, different types of bridge behaviors have been proposed to capture the resulting misbehavior. The simplest and most commonly used bridge fault models include the AND-type, OR-type and dominating-type, all of which assume a zero-resistance connection between the bridged lines [29]. These bridge faults abstract away the complex electrical characteristics of the defect by assuming that both lines will attain the same logic value. An AND (OR)-type fault assumes that the attained value is 0 (1), while the dominating-type assumes that the logic value of one line will prevail over the others. Other types of complex bridge faults consider a non-zero impedance of the connection for determining fault behavior [33, 34, 35].

Fault models for other types of defects have also been proposed. For example, the transistor stuck open model introduced in [36] assumes that a defect can cause a transistor to be permanently non-conducting or stuck-open. Multiple stuck-line (MSL) [29] faults are used to model the behavior of defects that cause stuck-faults on more than one line simultaneously. Defects that impact the delay of a CUT can often be modeled using transition [37, 38] and path delay faults [39]. The interconnect open fault model presented in [40, 41] is used to model the misbehavior due to resistive (or missing) vias along an interconnect.

#### 2.2 Diagnosis

Fault diagnosis dates back to the mid-1960s when the first algorithms for test generation were proposed [30]. The early diagnosis approaches evolved as a simple outgrowth of automatic test pattern generation (ATPG) algorithms, which use one or more fault models for generating test patterns. When a CUT failed one or more test patterns during manufacturing test, it was only natural to assume that the fault(s) associated with the failing patterns must contain some attributes of the defect in the CUT. In other words, because the failing patterns (that detect the defect in the CUT) were generated targeting some fault during the ATPG process, the same fault must somehow capture some aspect of the actual defect. Starting from this simple and intuitive

observation, fault diagnosis has become a necessarily complex task.

The need for more powerful fault diagnosis techniques stands in contrast to the needs of ATPG. Although simple fault models (typically, SSL or transition faults) suffice for generating test patterns that detect defects in nanoscale ICs, fault diagnosis based solely on the same fault models are rarely able to identify a fault that accurately represents the defect in the CUT. Some fault diagnosis approaches attempt to improve accuracy by adopting more complex fault models [10, 35, 42, 43], others use simple fault models in conjunction with complex matching techniques for localization [11, 44, 45]. Yet others focus exclusively on diagnosis of defects that behave as multiple stuck-line (MSL) faults [46, 47, 48]. In complimentary work, some researchers focus on fault-distinguishing test pattern generation for improving accuracy and resolution of existing diagnosis techniquese.g., [17, 49].

Early on, fault diagnosis techniques were categorized as either localization or fault-identification methods based on their end objective of identifying defect locations or faults, respectively. Fault diagnosis techniques can also be classified based on how they achieve their respective objectives, i.e., based on their approach. Specifically, all fault diagnosis techniques can be very broadly categorized into either cause-effect or effect-cause analysis techniques. The former identifies candidates by comparing the observed tester response of a CUT with fault simulation responses for a set of faults chosen a priori. Therefore, cause-effect techniques start with possible causes (faults) and determine if any selected *cause* can account for the *effect*, i.e., the tester response.

Similar to human diagnosticians in its main principle of relying on known failure modes, the cause-effect category of techniques had been the most popular. The fault simulation responses utilized in cause-effect techniques are typically generated once and stored in a simple but large database typically referred to as a fault dictionary [29, 30, 50, 51]. Fault dictionaries suffer from both space and time complexities, that is, the compute time and memory required to fault simulate and store fault-simulation responses for all the targeted faults is extremely prohibitive. Although research in dictionary compaction techniques have attempted to alleviate the storage issue, e.g., [52], the dictionary approach is still limited by long simulation time and its inher-

ent inefficiency in that only a small fraction of the fault simulation responses are ever used for diagnosing failures.

The success of cause-effect techniques hinges upon the availability of accurate fault models. If a fault model precisely captures the behavior of a defective CUT, a simple (exact) matching criterion can be used for identifying diagnosis candidates. Given that fault models seldom accurately model defects [12], fault diagnosis research has focussed on developing complex response matching techniques and an alternative approach known as effect-cause analysis. Rather than searching for a traditional fault whose simulation response is identical to the tester response, diagnosis approaches based on matching techniques utilize the notion of temporary stuck line (TSL) faults and a ranking metric to identify sets of TSL faults that together explain all the failing patterns. The signal lines associated with the identified set of TSL faults are reported as candidate locations.

Effect-cause analysis techniques do not use fault dictionaries but instead begin with the effect in order to find its potential causes [29]. Specifically, effect-cause analysis starts from the failing outputs and reasons back through the CUT to identify lines that (if faulty) could have caused the failing outputs. Most effect-cause techniques begin with some form of critical path tracing [53]. Although effect-cause techniques claim to be completely independent of fault models, they employ rules of fault sensitization and error propagation that are similar to SSL faults. In other words, effect-cause analysis techniques, at least in their earliest form [29], attempt to identify signal lines that cannot be driven to both logic-0 and logic-1 for the applied test patterns, which is the understood definition of an SSL fault.

A typical diagnosis output of effect-cause analysis consists of a set of signal lines or logical regions of the CUT that are suspected to be defective. The fact that effect-cause techniques can identify fault locations even when multiple lines are faulty simultaneously is another advantage over cause-effect techniques that are typically based upon a single-fault assumption [29, 51]. On the negative side, effect-cause analysis focusses on localization and does characterize the behavior of the failure. In addition, because effect-cause techniques tend to be conservative and

include many of the signal lines that could have caused the observed failing outputs, diagnosis resolution is typically low.

Since an IC can fail in a vast number of ways, the model-independent approach of effect-cause techniques is more practical than the cause-effect approach based on one or more fault models. However, use of accurate fault models increases diagnosis accuracy and resolution [10, 35]. Also, fault models enable characterization of defect behavior. In order to get the best of both worlds, most fault diagnosis techniques use a combination of effect-cause and cause-effect techniques [11, 14, 54, 55]. Specifically, potential defect locations are first identified using effect-cause analysis and fault models are then applied based on the reduced set of signal lines to identify candidates via a dynamic cause-effect analysis.

#### 2.2.1 Cause-Effect Diagnosis

The main objective of diagnosis based on cause-effect analysis is to identify a single fault (based on a presumed fault model) that can predict the observed CUT behavior. While initial techniques used SSL faults, bridge [10, 35] and transistor stuck-open faults [56] have also been utilized. In this section, we will review some cause-effect diagnosis techniques based on the fault models utilized.

#### 2.2.2 SSL Faults

The simplicity, success, and availability of existing ATPG tools for the SSL fault model made it a natural choice for fault diagnosis [30]. The earliest diagnosis techniques searched for SSL faults with simulation responses identical to the tester response. However, experience quickly revealed that stuck-at faults did not always accurately model the defect behavior observed from failing CUTs. As a result, more complex response comparison heuristics were developed to identify candidate SSL faults. The notion of fuzzy matching was used by Western Electric Company as early as 1971 to identify SSL faults whose fault-simulation responses approximately matched

the tester response [57].

Because an SSL fault does not accurately capture the behavior of many complex defect types, mispredictions and nonpredictions can occur. A misprediction occurs when a fault predicts an output to fail that does not fail on the tester, while the absence of one or more observed failing outputs in the fault simulation response results in a nonprediction. To deal more effectively with mispredictions and nonpredictions, a new method for ranking SSL faults was introduced in [4], where a score is assigned to each SSL fault. The score of an SSL fault si is calculated as a weighted sum (the weights being user-defined inputs) of the following two metrics: 1) the number of failing outputs in the tester response not present in the fault simulation response, and 2) the summation of the number of passing patterns that detect si and number of failing patterns for which si does not explain any failing output. The two metrics are zero when intersection equals the set of failing outputs in the tester response and when there are no mispredictions and nonpredictions, respectively. Faults that have the lowest score are the best candidates.

Although comparison heuristics are able to accommodate defects that do not behave exactly like SSL faults, diagnosis based on SSL faults is still limited because of the assumption that defects cause only one signal line in the CUT to become faulty. In addition, the line is assumed to be stuck-at the faulty value permanently. In reality however, there often are defects that cause errors of both polarities (0/1 and 1/0) on lines that can change for different test patterns. In other words, defects can exhibit different misbehaviors for each failing pattern. Diagnosis of such defects based solely on the SSL fault assumption may fail to identify defect locations accurately or may result in an empty diagnosis, i.e., no candidates are identified.

#### 2.2.3 Bridge Faults

Unwanted electrical connections between two lines have long been considered an important class of defects. In the logic-level domain of ATPG, fault simulation and fault diagnosis, the behavior of a two-line unwanted connection is modeled using two-line bridge faults of different types.

Cause-effect diagnosis techniques based on bridge faults utilize one or more bridge fault models to identify candidates.

A dictionary-based approach is described in [35], where diagnosis candidates are identified by simulating bridge faults and finding the faults with simulation responses identical to the tester response. A more accurate model for bridge faults, namely, the biased-voting model is used in [42] and [33]. Very good diagnosis results in terms of accuracy and resolution are reported. Based on the results of their experiments and comparisons with an alternative approach to bridge fault diagnosis, the authors observed that a more generalized fault model can lead to a more accurate fault diagnosis. Although accuracy is improved, their technique suffers from the same limitations as any other cause-effect technique. Specifically, the number of two-line bridge faults is enormous at for an n-line CUT. In [10, 35], layout analysis is used to identify the likely bridge locations, but the number of likely bridges can still be quite large and the time required to simulate and store the fault simulation responses can be prohibitive. Additionally, time-consuming transistor-level analysis is required to build the biased-voting model, but this cost can be incurred once for a standard library and then amortized over many designs.

An alternative cause-effect technique for identifying bridge fault candidates is described in [58]. Rather than using fault dictionaries, these techniques analyze each failing pattern to identify pairs of lines that satisfy the detection conditions for bridge faults. A bridge fault between two lines is detected if the two lines are driven to opposite logical values and a stuck-at fault on one of the two lines is detected. For each failing pattern, the diagnosis technique of [58] searches for pairs of lines that are 1) driven to opposite values for each failing pattern and 2) have a stuck-at fault on at least one of them explain the failing pattern. Because such technique does not use fault dictionaries generated in a static manner, it is sometimes referred to as dynamic cause-effect technique.

The most significant drawback of dynamic cause-effect technique as described above is that its applicability is limited to only those bridge faults that behave like one of the traditional bridge fault types, i.e., AND, OR and dominating bridge faults. In other words, the technique will fail to

identify the correct candidates if the bridge behaves any differently from the traditional models (e.g., if the bridge behaves according to the biased-voting model).

#### 2.2.4 Transistor Stuck-Open Faults

Transistor stuck-open (TSO) faults [36] represent the logic-level behavior of defects that cause a transistor to become non-conducting. Unlike the other fault models discussed so far, TSO faults capture misbehavior stemming from within a gate. As described in [36], SSL faults dominate TSO faults, that is, every test pattern that detects a TSO fault also detects at least one SSL fault at the input or output of the affected gate. Further, TSO faults are assumed to be detected by a sequence of patterns applied to the defective transistor. TSO faults are therefore often referred to as sequence-dependent faults.

A technique to identify gates with TSO faults is described in [59]. This technique is similar in principle to the dynamic cause-effect techniques for bridge fault diagnosis in that it utilizes the detection requirements of an assumed fault type to identify diagnosis candidates. Specifically, gates affected by TSO faults are identified using a two stage process. Initially, potential locations are identified by finding SSL faults that explain all the failing patterns. Given that this technique ignores the behavior of the intragate defect for passing patterns, this technique actually searches for a temporary stuck-line (TSL) fault (li/v)Tk, where Tk is the set of failing patterns. A sequence-dependence check is then performed for each potential location; for each TSL fault (li/v)Tk identified in the first stage, the diagnosis technique checks for a transition from logic-v to logic-v for two consecutive patterns. Locations that satisfy the transition check are reported as diagnosis candidates.

The greatest advantage of the above technique lies in its simplicity. As described in [59], this technique can be implemented with only slight modifications to existing SSL fault simulators. However, the technique is not complete in that it is not guaranteed to find the faulty gate since only a detection condition is used and not a model of all possible TSO behaviors.

An alternative TSO fault diagnosis technique based on the same principle as [59] is described in [56]. This technique employs circuit modification, where the transistor-level TSO fault is mapped to an SSL fault by transforming the transistor-level description of a suspect gate into a gate-level description.

Suspect gates are initially identified in terms of TSL faults as described earlier. SSL-based fault diagnosis (with an exact match condition) is then used to identify candidate SSL faults that are subsequently correlated back to the relevant TSO faults. Although this technique allows using the relatively straightforward SSL-based diagnosis, it has the same limitations as [56]. Also, this technique requires transforming the transistor-level description of each suspect gate into its equivalent gate-level description for each run of diagnosis.

#### 2.3 Per-Test Diagnosis

As described in the previous section, cause-effect diagnosis is limited by the lack of accurate fault models as well as the impracticality of simulating and storing the fault simulation responses for non-SSL faults. Also, cause-effect diagnosis techniques lack generality in that their applicability is restricted to the targeted set of fault models. An alternative approach to cause-effect diagnosis involves using advanced matching techniques in conjunction with SSL fault simulation to perform fault diagnosis. This approach is based on the key observation that behavior of most defects match a set of TSL faults. The basic objective of matching techniques is to identify sets of TSL faults that can together explain the observed tester response. A different method for achieving this objective have been described in the past, which is named per-test diagnosis [11]. In this approach, each failing pattern is examined as an independent source of diagnosis, hence the name *per-test*.

The earliest per-test diagnosis technique is described in [11], where SSL faults are simulated iteratively to identify sets of TSL faults that can account for all the applied test patterns. A dynamic cause-effect approach is adopted, where the SSL faults analyzed are selected using

effect-cause analysis for each failing pattern. SSL faults that explain a given failing pattern are fault simulated against other failing patterns to determine if they can be explained as well. If an SSL fault that explains all the test patterns (both failing and passing) is found, it is reported as the candidate and diagnosis stops. Otherwise, the explained failing patterns are removed from further consideration and the corresponding TSL faults are added to the candidate list. Diagnosis is repeated until all failing patterns have been explained, adding one or more TSL faults to the candidate set at each iteration step.

Based on the identified set of TSL faults, the type of defect is binned into one of two classes:

1) defects that exhibit stuck-0 and stuck-1 behavior on the same line (i.e., candidate set has  $(l_i/0)T_p$  and  $(l_i/0)T_q$ , where  $T_p+T_q$  equals set of all failing patterns), and 2) defects that exhibit stuck-at behavior on more than one signal line (i.e., several TSL faults in the candidate set). For these two defect classes, some amount of misprediction is possible for the passing patterns, but each failing pattern is expected to be accounted for by at least one TSL fault in the candidate set. Thus, defects that create a failing pattern that is not part of any TSL fault defeat this approach.

More recent per-test diagnosis techniques are described in [6, 12, 60]. The SLAT technique of [6, 60] identifies faulty lines by analyzing each failing pattern independently in a manner similar to [11]. A line li is considered faulty if the TSL fault of either polarity on li explains at least one failing pattern. The failing patterns that are not part of any TSL fault are discarded; the remaining (explained) failing patterns are referred to as SLAT patterns. The lines obtained from diagnosis of each failing pattern are analyzed using a set-covering algorithm to identify a minimal set that can account for all the SLAT patterns. The minimal set forms the diagnosis outcome and is the representation of the potential defect locations.

In [11], the SLAT philosophy is extended by 1) identifying sets of TSL faults (as against only faulty lines in SLAT) and 2) using probability theory as a basis for ranking the sets of TSL faults. All test patterns are used for determining the rank of a TSL fault set. The TSL faults in the top-ranking set are subsequently correlated with common fault models that include bridge, interconnect-open and other fault types. In the fault model correlation process, inherent

characteristics of different fault types are utilized. For example, an AND(OR)-type bridge fault is inferred if the candidate set comprises only two TSL faults, each with the 0(1) polarity and an interconnect open fault is inferred if the set consists of TSL faults of both polarities on the same line. Therefore, the per-test approach of [11] integrates the model-independent benefits of per-test diagnosis and fault-identification benefits of cause-effect diagnosis.

# 2.4 Summary

In this chapter, some background about testing and diagnosis are provided. Defects are physical deformations that change the circuit structure; faults are the models used to capture the logic-level misbehavior of defects. Diagnosis is the process to localize and identify the faults in defective chips.

Diagnosis techniques are categorized as either cause-effect or effect-cause. Cause-effect techniques require accurate fault models, from the most basic SSL fault model to other more sophisticated fault models, an accurate cause-effect diagnosis not only localizes the defect, but also reveals the nature of the defect. On the other hand, effect-cause techniques, such as per-test diagnosis, do not reply on specific fault model, which makes them more versatile for diagnosing the defects that cannot be accurately modeled with fault models.

However, despite all the efforts, diagnosis is still not perfect. The poor diagnostic resolution hinders other analyses for yield learning.

# **Chapter 3**

# **PADRE**

## 3.1 The PADRE Methodology

PADRE is a two-level classifier that identifies incorrect candidates in the first level and correct candidates in the second. The overall flow of PADRE is illustrated in Figure 3.1. PADRE takes as input the diagnosis results for a population of failing chips. Each chip may have multiple defects and each defect may have multiple candidates. For all the candidates, a set of features are extracted to characterize each candidate.

#### 3.1.1 Candidate Features

Candidate features are specific design and testing characteristics that differentiate correct candidates from incorrect ones. The candidate features now considered in PADRE are summarized in Table 3.1.

Some of the candidate features such as passing\_states, failing\_states, and inconsist\_states are physical features, because they characterize the layout characteristics of a candidate when it is both activated and sensitized. Specifically, the neighborhood state of a candidate is formally defined as the logic values driven on nets that are in physical proximity of the candidate for

Figure 3.1: PADRE takes all the candidates through a two-level classifier, in which incorrect candidates are eliminated and correct candidates are identified. By reducing the total number of candidates while maintaining accuracy, the resolution of the diagnosis is improved.

| Table 3.1: List of Features Considered in PADRE. |                                                                                           |  |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|

| Feature                                          | Description                                                                               |  |  |

| TFSF                                             | No. of Tester-Fail-Simulation-Fail (TFSF) outputs associated with the candidate           |  |  |

| TFSP                                             | No. of Tester-Fail-Simulation-Pass (TFSP) outputs associated with the candidate           |  |  |

| TPSF                                             | No. of Tester-Pass-Simulation-Fail (TPSF) outputs associated with the candidate           |  |  |

| bit_score                                        | Candidate score based on output features                                                  |  |  |

| TFSF_ptn                                         | No. of Tester-Fail-Simulation-Fail (TFSF) patterns associated with the candidate          |  |  |

| TFSP_ptn                                         | No. of Tester-Fail-Simulation-Pass (TFSP) patterns associated with the candidate          |  |  |

| TPSF_ptn                                         | No. of Tester-Pass-Simulation-Fail (TPSF) patterns associated with the candidate          |  |  |

| ptn_score                                        | Candidate score based on pattern features                                                 |  |  |

| nbr                                              | No. of neighbors of the candidate                                                         |  |  |

| failing_states                                   | No. of unique neighborhood states observed for TFSF patterns                              |  |  |

| passing_states                                   | No. of unique neighborhood states observed for TPSF patterns                              |  |  |

| inconsist_states                                 | No. of unique neighborhood states observed for both TPSF and TFSF patterns                |  |  |

| resol_ratio                                      | The resolution of the defect that the candidate is associated with                        |  |  |

| ratio_failing_states_to_TFSF_ptn                 | Ratio between no. of unique failing states and no. of TFSF patterns                       |  |  |

| ratio_passing_states_to_2 <sup>nbr</sup>         | Ratio between no. of unique passing states and 2 <sup>nbr</sup>                           |  |  |

| ratio_failing_states_to_2 <sup>nbr</sup>         | Ratio between no. of unique failing states and 2 <sup>nbr</sup>                           |  |  |

| ratio_max_0_TPSF_physical_to_physical_nbr        | Ratio between maximum no. of 0s in TPSF physical states and the no. of physical neighbors |  |  |

| ratio_max_1_TPSF_physical_to_physical_nbr        | Ratio between maximum no. of 1s in TPSF physical states and the no. of physical neighbors |  |  |

| ratio_max_0_TFSF_physical_to_physical_nbr        | Ratio between maximum no. of 0s in TFSF physical states and the no. of physical neighbors |  |  |

| ratio_max_1_TFSF_physical_to_physical_nbr        | Ratio between maximum no. of 1s in TFSF physical states and the no. of physical neighbors |  |  |

| ratio_max_0_TPSF_nbr_to_all_nbr                  | Ratio between maximum no. of 0s in TPSF states and the total no. of neighbors             |  |  |

| ratio_max_1_TPSF_nbr_to_all_nbr                  | Ratio between maximum no. of 1s in TPSF states and the total no. of neighbors             |  |  |

| ratio_max_0_TFSF_nbr_to_all_nbr                  | Ratio between maximum no. of 0s in TFSF states and the total no. of neighbors             |  |  |

| ratio_max_1_TFSF_nbr_to_all_nbr                  | Ratio between maximum no. of 1s in TFSF states and the total no. of neighbors             |  |  |

tests that detect the candidate [3]. The neighborhood nets for a given candidate, as illustrated in Figure 3.2, include:

• Physical neighbors : nets that are in close proximity

• **Drivers**: inputs of the cell that drives the candidate

• **Side inputs**: side inputs of the cells driven by the candidate

Figure 3.2: Example of the neighborhood of a candidate associated with net  $S_6$ : (a) the physical neighbors, *i.e.*, nets in close physical proximity of the candidate and (b) the driver and receiving-cell side inputs of the candidate.

Independent of any other characteristics of the circuit, the logic value of a candidate, whether faulty or fault-free, is assumed to be a function of its neighborhood state, *i.e.*, the logic values of its neighbors. The characteristics of the neighborhood may also provide an indication of the

authenticity of a candidate. The heuristic is that if a candidate is indeed a site of failure, its failing activation behavior should be a consistent function of its failing and passing states.

Many features used by conventional diagnosis are included in this thesis, such as TFSF, TFSP, and TPSF, which compare/contrast the pass-fail status of the *test outputs* observed by the tester and predicted by simulation, as well as TFSF\_ptn, TFSP\_ptn, and TPSF\_ptn, which compare/contrast the pass-fail status of the *test patterns* observed by the tester and predicted by simulation. In addition to their absolute values, the ratio between the features is also commonly used in characterizing a candidate. For example, in [61] the following ratio-based score is used:

$$bit\_score = \frac{TFSF}{TFSF + TPSF/10 + TFSP}$$

(3.1)

It should be noted that TPSP is not used in the formulation since many candidates typically have very large values for this feature that would overwhelm the significance of the remaining three. Also, TPSF is weighted by 1/10 to cope with the possible temporal stuck-at behavior of a defect, which may produce a large value for TPSF that overwhelms the other parameters in the equation, *i.e.*, TFSF and TFSP.

Similar to bit\_score, a score based on the ratio between pattern features is also included:

$$ptn\_score = \frac{TFSF\_ptn}{TFSF\_ptn + TPSF\_ptn/10 + TFSP\_ptn}$$

(3.2)

In addition to these well-established features, many other ratio-based features are newly established in this thesis. For example, ratio\_failing\_states\_to\_TFSF\_ptn characterizes the variety of different failing\_states\_to\_2<sup>nbr</sup> and ratio\_failing\_states\_to\_2<sup>nbr</sup> characterize the variety of different passing states and failing states respectively, given the maximum number of possible different states of 2<sup>nbr</sup>. Some ratio-based features in this thesis characterize the maximum density of 0s or 1s in the neighborhood states observed for TFSF or TPSF patterns, whereas some other features characterize similar properties

within only physical neighbors. All these features provide information to characterize candidates in different passing/failing situations that are not exploited by conventional diagnosis.

#### 3.1.2 Classifier Structure

PADRE is a two-level classifier; the first-level classifier consists of a single-rule discriminator eliminating incorrect candidates. The second-level classifier is an SVM classifier used to identify correct candidates.

#### First-level classifier

The first level is a one-rule discriminator that is based on the inconsist\_states feature. As described earlier, this feature counts the number of unique neighborhood states that are observed for at least one TPSF pattern and one TFSF pattern. The existence of an inconsistent state is likely an indication that the candidate is an incorrect candidate. Any candidate with a non-zero inconsist\_states is *labeled* as incorrect and is eliminated from the candidate list. A *label* refers to a prediction made by the classifier on whether a given candidate is correct or incorrect. For all the remaining candidates with no inconsistent state, their labels remain unknown and are passed on to the second level. The action of the first-level classifier can be summarized as:

$$label = \begin{cases} incorrect & inconsist\_states > 0 \\ unknown & inconsist\_states = 0 \end{cases}$$

(3.3)

#### Second-level classifier

Although the first level is able to accurately identify a large number of incorrect candidates, typically many candidates still remain unlabeled after the first level. We introduce the second level to further process the remaining unlabeled candidates, with a particular focus on identifying correct candidates. All unlabeled candidates from the first-level classifier are processed by an

SVM-based second-level classifier. The second-level classifier predicts all unlabeled candidates as either correct or incorrecct. Based on the correct candidates identified by the second-level classifier, resolution improvement is performed across all the defects. If a defect has any of its candidates predicted as correct by the second-level classifier, then all its remaining candidates which are predicted as incorrect are eliminated from the candidate list. On the other hand, if no candidate is predicted as correct, all candidates associated with the defect are retained in the candidate list.

SVM requires training data to learn a classifier. Unlike conventional supervised learning techniques, where the training data are assumed to be labeled using techniques, such as PFA, that is costly or difficult to invoke, the training data used to learn the second-level classifier in PADRE is derived from the pool of unlabeled candidates themselves. Specifically, the correct-labeled training set is obtained from all the defects with a single candidate. Assuming that diagnosis is accurate, collecting a statistically-significant set of single-candidate defects ensures that the characteristics of correct candidates are well represented by correct-labeled training set. On the other hand, the incorrect-labeled training set is obtained from all the defects with more than Q candidates, where Q is a user-defined value. The heuristic behind the incorrect-labeled training set construction is that there is likely only one correct candidate associated with a given defect. Thus for a defect with multiple candidates, all but one will be incorrect. In general, a larger Q lowers the error, but a smaller value for Q increases the amount of incorrect-labeled training data. By taking all the defects with a high number of candidates, the incorrect-labeled training set will mostly consist of incorrect candidates. For example, in this thesis we choose Q=20, which bounds the error at 5%, in other words, at most 5% of the candidates in the incorrect-labeled training set will be actually correct candidates. Note that the value of Q is chosen based on the property of available failing data, it should be high enough to ensure the quality of labeledincorrect training data, whereas it should not be too high as that will fail to produce sufficient amount of incorrect-labeled training data to match the size of the correct-labeled training data.

By studying the nature of the candidates in the correct-labeled training set, it is revealed that

the correct-labeled training set consists of only candidates that do not have any equivalent faults, *i.e.*, faults that are indistinguishable from a given candidate by contrasting their test responses. Based on their net types, such candidates can be categorized as follows:

- PI (primary input)

- PO (primary output)

- fanout of PI

- fanout of stem-net

- stem-net with a fault that is not equivalent to any faults at its driver

It should be noted that the correct-labeled training set and the incorrect-labeled training set are likely to be different in size (there are typically fewer correct candidates than incorrect candidates identified from the unlabeled pool of candidates). The imbalance of training set size may result in a biased classifier. Specifically, if the size of the incorrect-labeled training set overwhelms the size of the correct-labeled training set, the learned classifier will be heavily biased towards incorrect candidates, causing it more likely to incorrectly predict an actually correct candidate as incorrect [62]. A straightforward solution for this problem involves balancing the size of the training sets with simple re-sampling techniques. There are two approaches to perform the sampling. One approach is to under-sample the incorrect-labeled training set, and the other approach is to over-sample the correct-labeled training set. Under-sampling the incorrect-labeled training set has the benefit of low computational cost, but it incurs the risk of not properly characterizing the incorrect candidates if the difference between the sizes of two training sets is too large. We therefore choose to balance the two training sets by over-sampling the correct-labeled training set. Specifically, candidates in the correct-labeled training set are randomly duplicated until two training sets are equal in size.

In summary, the construction of the two training sets is performed as follows:

• **Initial training sets:** The initial training set of candidates that are labeled correct consists of all the candidates of defects with only a single candidate; and the initial training set

of candidates that are labeled incorrect consists of all the candidates of defects with more than Q candidates, where Q is a user-defined threshold. In this work, we set Q=20.

• **Balanced training sets:** The smaller initial training set of one class is over-sampled to match the size of the larger initial training set of the other class.

#### 3.1.3 Feature Selection

In practice, some features proposed in this thesis may not be available, which could potentially hinder the performance of PADRE. Therefore, it is important to evaluate how useful each feature is, so as to understand their impact on PADRE performance when they are not available. In addition, it is always desirable to perform resolution improvement at a lower cost. It is possible to reduce the cost of feature extraction if we can reduce the number of features used by PADRE while maintaining classification accuracy. To address these concerns, all the features are analysed to understand their effectiveness within PADRE.

Fisher score [63] is a straightforward measurement for evaluating the correlation between a feature and the candidate class. A higher Fisher score indicates a stronger correlation, and thus a more effective feature. To calculate Fisher score, it requires not only the feature data of the candidates, but also the true labels of the candidates. For feature data x of n candidates, the Fisher score of j-th feature of the data,  $x^j \in \mathbb{R}^{1 \times n}$  is calculated as:

$$F(\mathbf{x}^{j}) = \frac{\sum_{k=1}^{c} n_{k} (\mu_{k}^{j} - \mu^{j})^{2}}{\sum_{k=1}^{c} n_{k} (\sigma_{k}^{j})^{2}}$$

(3.4)

where c is the total number of classes corresponding to j-th feature,  $n_k$  is the total number of candidates in each class k,  $\mu_k^j$  and  $\sigma_k^j$  are the mean and the standard deviation of data in the k-th class corresponding to j-th feature, respectively, and  $\mu^j$  is the mean of all the data corresponding to j-th feature.

Although the Fisher score captures how strongly each feature correlates with the candidate class, it is inadequate to infer the joint effectiveness of multiple features as it does not account

for correlation among features. To evaluate the joint effectiveness of multiple features, a feature selection problem has to be solved.