# Superscalar\* Club Meeting #2

\*we really mean: superscalar speculative out-of-order

James C. Hoe Department of ECE Carnegie Mellon University

[Internal Use Draft] Superscalar Club Meeting #2, Slide 1, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

# Today's Goal: One step closer to understanding R10K

[Internal Use Draft] Superscalar Club Meeting #2, Slide 2, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

### **References Used**

**Popescu, et al., The Metaflow Architecture, 1991.**

- Yeager, MIPS R10K Superscalar Microprocessor, 1996.

- Gonzalez, et al., Processor Microarchitecture: An Implementation Perspective, Synthesis Lectures, 2010.

- Hennessy&Patterson, Computer Architecture: A Quantitative Approach, 5th Edition, 2017.

- Johnson, Superscalar Microprocessor Design, 1990.

- Shen&Lipasti, Modern Processor Design: Fundamentals of Superscalar Processors, 2013.

# Agree on Terminology btw Us (not a universal agreement)

#### **Program State Views**

Figure 5-1. Illustration of In-Order, Lookahead, and Architectural States from [Johnson, 1990]

[Internal Use Draft] Superscalar Club Meeting #2, Slide 5, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

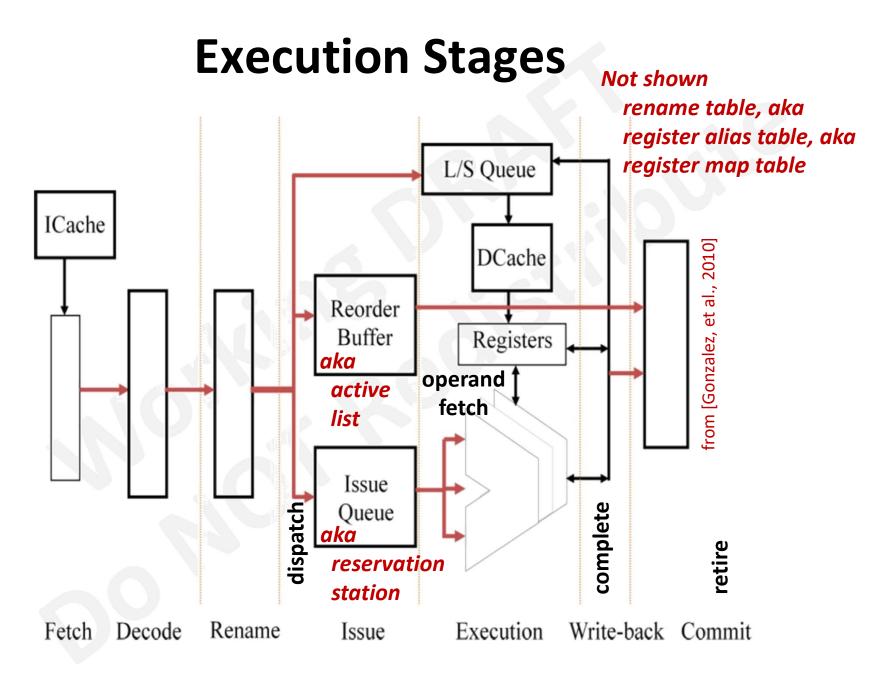

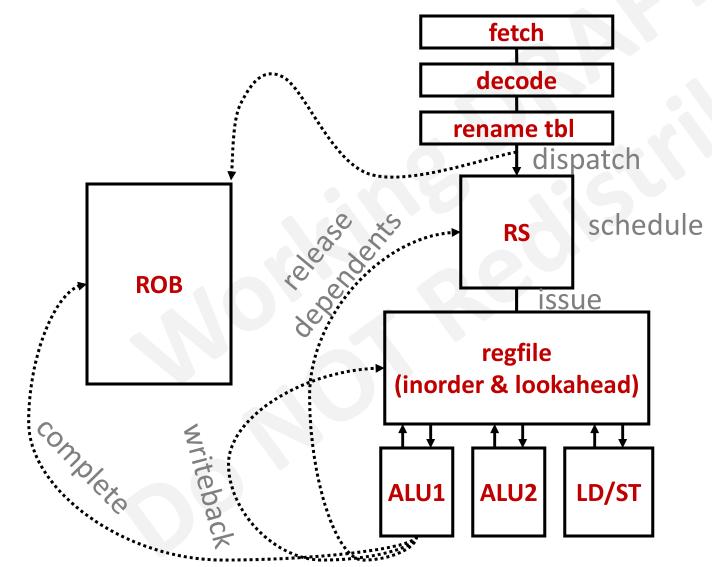

#### **Generic Mental Model**

<sup>[</sup>Internal Use Draft] Superscalar Club Meeting #2, Slide 7, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

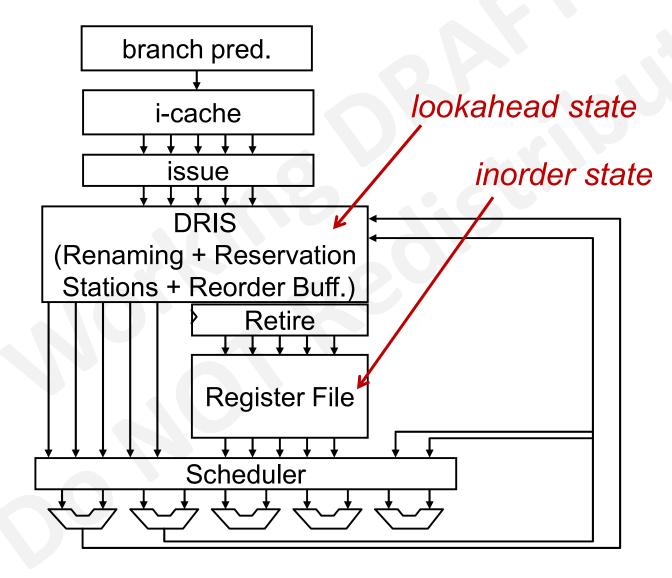

# **Metaflow DRIS**

[Internal Use Draft] Superscalar Club Meeting #2, Slide 8, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

## **Metaflow Lightning SPARC Processor**

- Superscalar fetch, issue, and execution

- Micro-dataflow instruction scheduling

- Register renaming + memory renaming

- Speculative execution with rapid rewinding

- Precise Exceptions

circa 1991

#### Claimed "Factor of 2-3 performance advantage from architecture"

#### **Metaflow Datapath**

[Internal Use Draft] Superscalar Club Meeting #2, Slide 10, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

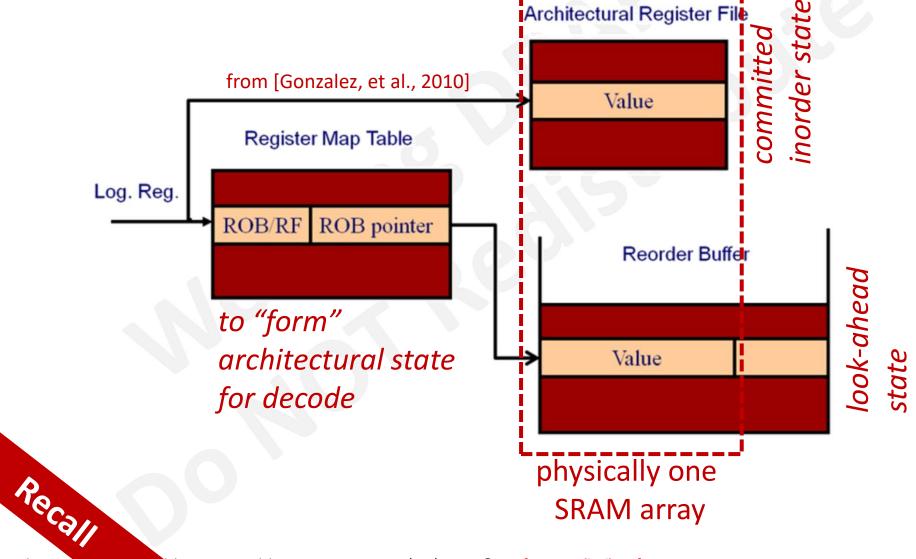

#### **ROB Rename Registers**

[Internal Use Dran

hub Meeting #2, Slide 11, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

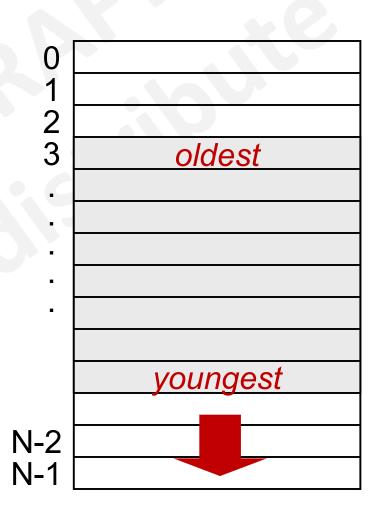

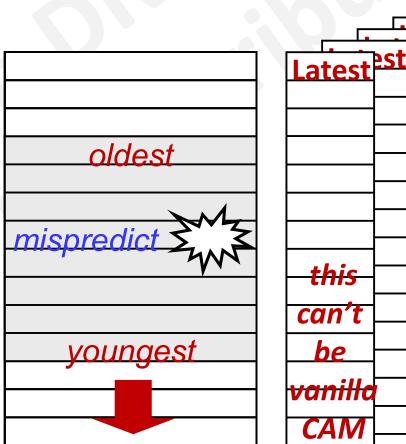

# **DRIS is ROB-like**

- Circular Queue Structure

- Instructions held in original program order

- new entry allocated at tail of queue when instruction issues

- completed entry committed inorder from head of queue to update regfile or memory

- Instruction's position in ROB is its unique *tag*

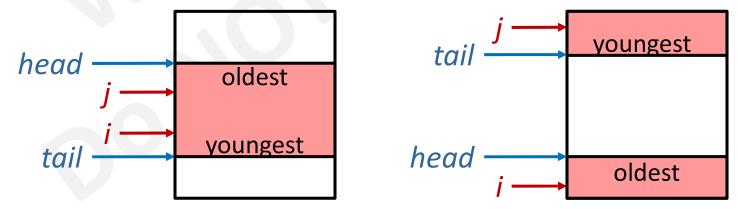

# **Color Bit**

- Head and tail pointers count around N-entry DRIS using 1+log<sub>2</sub>(N) bit

- bottom log<sub>2</sub>(N) *index* bits work the way you think

- top bit color bit alternate each round through

- Given indices *i* and *j*, *i* older than *j* when

if (*color*(*i*)==*color*(*j*)) then *index*(*i*) < *index*(*j*)

else *index*(*i*) ≥ *index*(*j*)

[Internal Use Draft] Superscalar Club Meeting #2, Slide 13, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

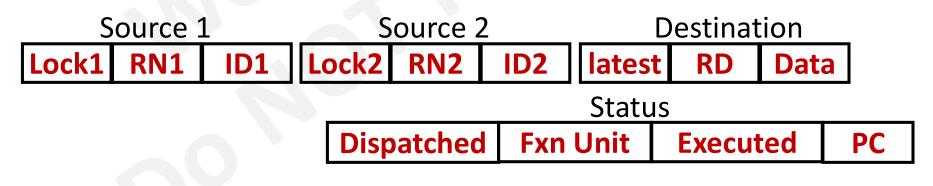

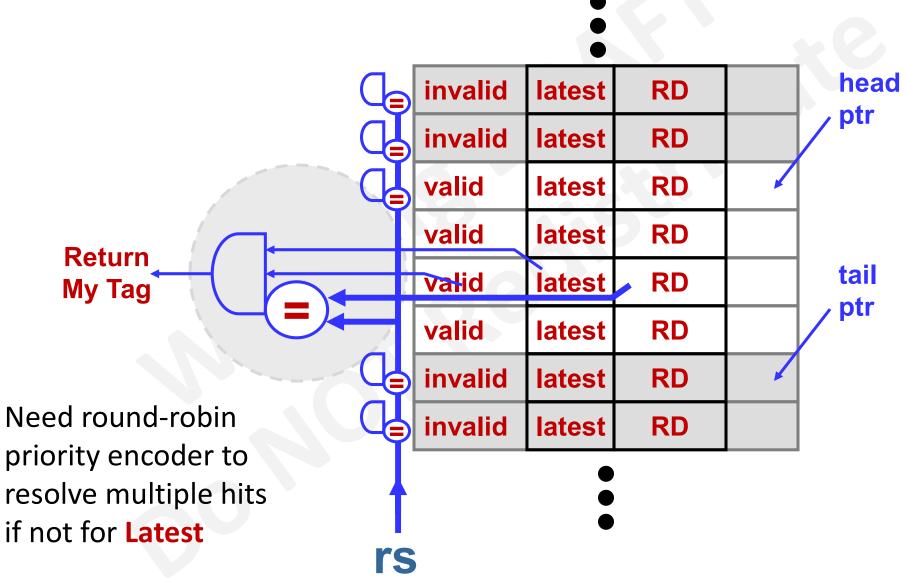

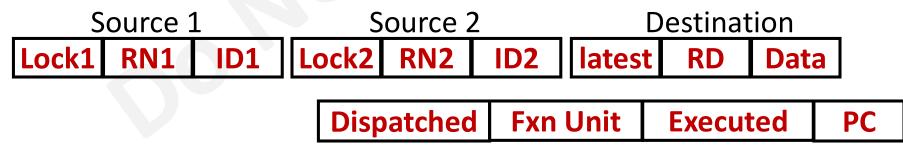

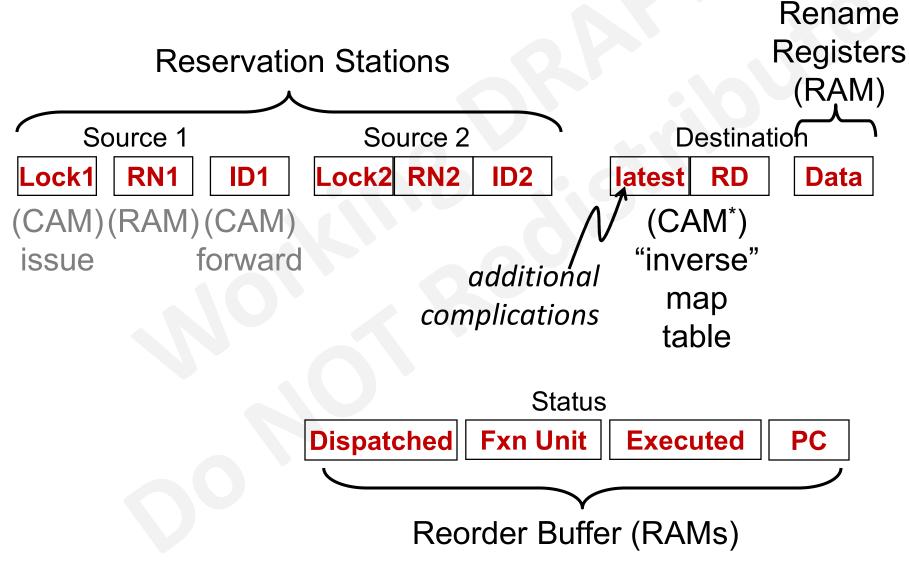

## **DRIS** is also everything else

- **ROB**: inorder record of in-flight instructions

- Rename Regfile: Data holds lookahead state of RD

- Rename Table (CAM-based): given operand rs, search RD youngest to oldest for re-definition

- Reservation Station: if !(Lock1 || Lock2)

- Address Queue: . . .

Know everything, look everywhere philosophy . . .

[Internal Use Draft] Superscalar Club Meeting #2, Slide 14, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

# "Issue": (Decode+Dispatch+Rename)

- A new ID (aka tag) is allocated to each instruction when issued into DRIS

- ID is index to next free DRIS circular queue entry

- Search DRIS (young to old) to see if rs1/2 matches

RD of older entry *i*.

- if found, set ID1/2 to i; set Lock1/2 if !Executed[i]

- if not found, set ID1/2 to (?) ; set RN1/2=rs1/2

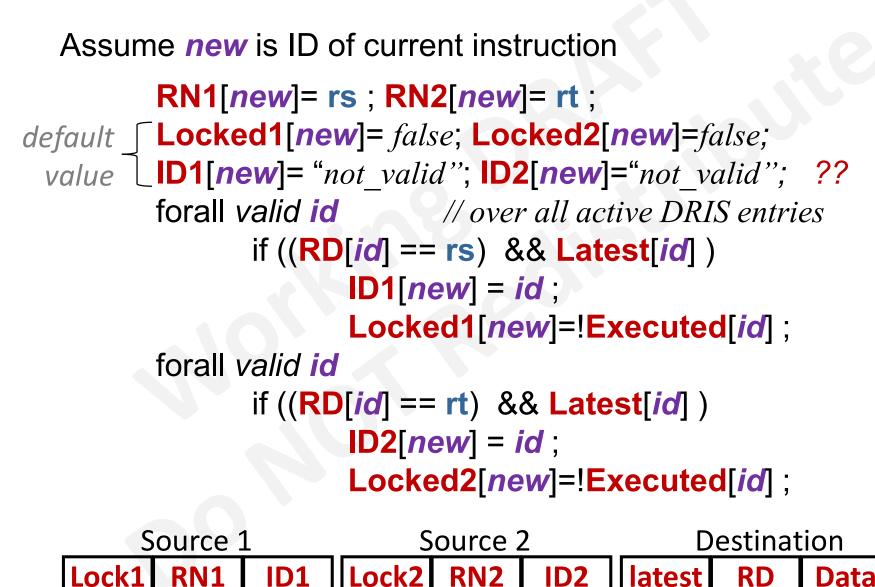

## Rename: add rd, rs, rt

Let's be a little more precise. You give it a try first.

[Internal Use Draft] Superscalar Club Meeting #2, Slide 16, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

## Rename: add rd, rs, rt

[Internal Use Draft] Superscalar Club Meeting #2, Slide 17, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

# **Associative Lookup for Just 1 Rename**

[Internal Use Draft] Superscalar Club Meeting #2, Slide 18, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

### **Superscalar Rename**

- Replicate the previous circuit, 2 per instruction

- All new entries read and update DRIS together

- replicated circuits all rename relative to same "architectural" view (i.e., from same tail ptr)

- what happens for 3-wide rename:

| add r1, r2, r3 |    | add r1, r1, r3 |

|----------------|----|----------------|

| add r4, r5, r6 | VS | add r1, r1, r4 |

| add r7, r8, r9 |    | add r1, r1, r5 |

Must do on-the-fly RAW dependence check and re-direct, O(N<sup>2</sup>) complexity

#### Rest is Easy: add rd, rs, rt

RD[new] = rd ; forall valid id ← one more CAM if (RD[id] == rd) Latest[id]=false ; Latest[new]=true ; Dispatched[new]= false ; Executed[new]= false ; FxnU[new]=Integer ALU ;

[Internal Use Draft] Superscalar Club Meeting #2, Slide 20, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

## **Micro-Dataflow Scheduling**

- The scheduler dispatches according to

- availability of pending instructions' operands

- availability of the functional units

- chronological order of the instructions

Is oldest-first the "best" strategy? What is?

Find instructions such that valid[id] && !Locked1[id] && !Locked2[id] && !Dispatched[id] && !Executed[id] && notBusy(fxnUnit[id])

Think about the circuits & multiply for superscalar

## Issue: add rd, rs, rt

- A issued instruction is sent to the functional unit with its operands and its *id*

- Operands come from:

- DRIS: Data[ID1/2[id]] when ID1/2[id] is younger than head ptr

#### in lookahead state

Regfile: Regfile[RN1/2[*id*]] when ID1/2[*id*] is older than head ptr (producer was already retired at decode or has since retired)

#### in inorder state

# Writeback/Complete

A Fxn unit returns both the *result* and the associated *id*

Data[id]=result;

Executed[id]=true ;

- Unlock RAW dependent instructions

- forall valid i

```

if (ID1[i]== id) Locked1[i]=false;

alid i

```

- forall valid i

```

if (ID2[i]== id) Locked2[i]= false;

Source 1 Source 2 Destination

Lock1 RN1 ID1 Lock2 RN2 ID2 latest RD Data

```

## Retire

- Instructions retire from DRIS inorder from oldest

- must be **Dispatched**, wait if not **Executed**

- not on wrongpath

- no older exceptions, itself could be

- Commit lookahead state to inorder state

- Regfile[**RD**[*retiree*]]=**Data**[*retiree*]

- Similarly, SW can only write memory when retiring

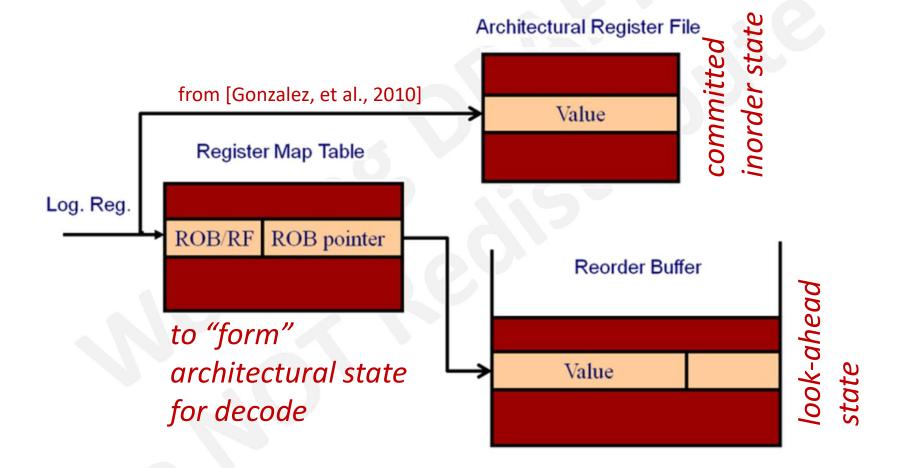

### Logical vs. Physical

[Internal Use Draft] Superscalar Club Meeting #2, Slide 25, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

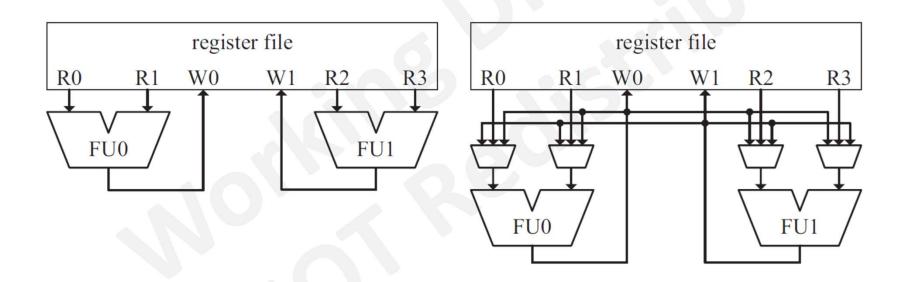

# The Cost of Implementing DRIS

- To support *N-way* rename per cycle

- Nx3 associative lookup and read

- Nx2 indexed read, Nx2 indexed write

- To support *N-way* issue per cycle

- 1 prioritized associative lookup of N entries

- N indexed write

- Nx2 indexed read in DRIS

- Nx2 indexed read in Regfile

- To support *N-way* complete *per cycle*

- N indexed write to DRIS

- Nx2 associative lookup and write in DRIS

- To support *N-way* commit per cycle

- N indexed lookup in DRIS

- N indexed write to DRIS

- N indexed write to Regfile

## Why CAM and not MAP Table?

#### What happens on exception and branch rewind?

[Internal Use Draft] Superscalar Club Meeting #2, Slide 27, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

#### **Precise Exceptions**

- On exception, stop fetching

- Wait until exception oldest in DRIS, set tail ptr to head ptr

- Done!

Does this work for branch rewind?

| oldest    |  |  |

|-----------|--|--|

|           |  |  |

| M         |  |  |

| exception |  |  |

| - Wi      |  |  |

|           |  |  |

|           |  |  |

| youngest  |  |  |

|           |  |  |

|           |  |  |

|           |  |  |

**Branch Stack**

(more next wk)

# **Rewind cannot wait for the head/oldest**

- Set tail ptr to after mispredicted branch to restart . . .

- What about Latest?

[Internal Use Draft] Superscalar Club Meeting #2, Slide 29, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

# To Sum Up

- Superscalar, speculative, out-of-order made "easy" by centralizing bookkeeping (if you could know everything at the same time)

- Circuits too elaborate (gratuitous use of large CAM especially) and inefficient (size and critical path) for what need to be accomplished

- On branch rewind

- identifying younger instructions occupying out-oforder structures by index-comparison too costly

- how to recovery the "latest" column?

- What is IPC when ILP=1? (paper doesn't say but it is handled the right way)

[Internal Use Draft] Superscalar Club Meeting #2, Slide 30, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]

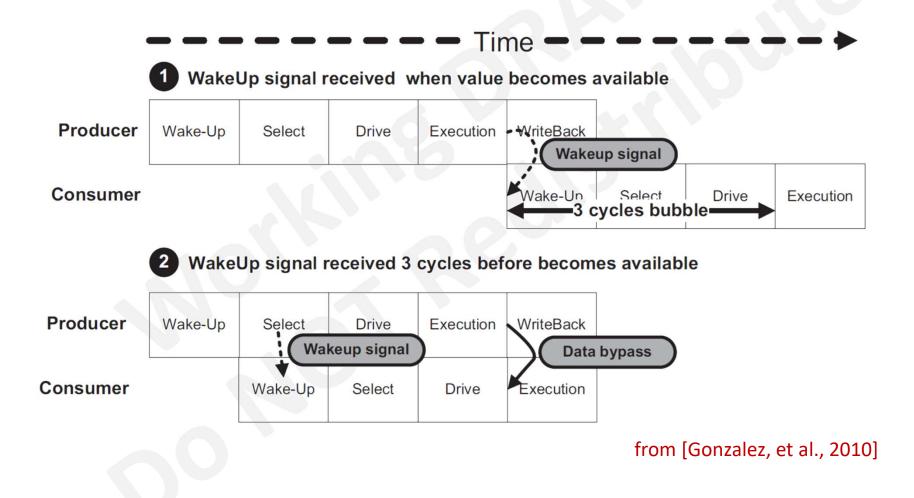

### **Issue and Forwarding Timing**

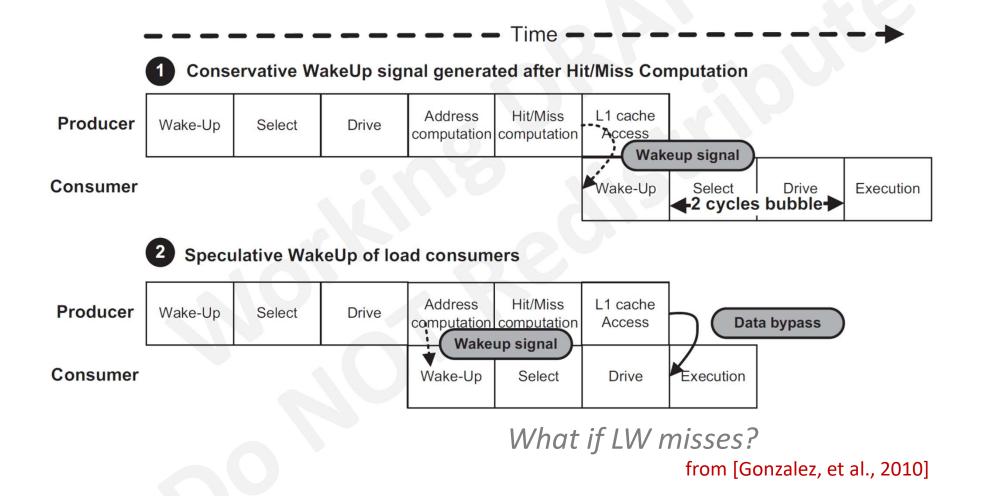

### **Scheduling Consumer of Loads**

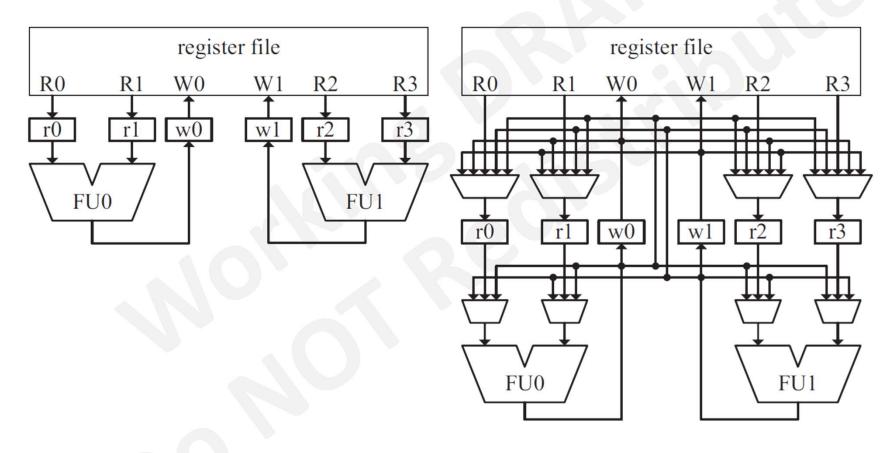

#### **Forwarding Paths Required**

from [Gonzalez, et al., 2010]

#### **Forwarding Path Complexity**

from [Gonzalez, et al., 2010]

# Read R10K very, very carefully for next week

[Internal Use Draft] Superscalar Club Meeting #2, Slide 35, James C. Hoe, CMU/ECE/CALCM, ©2023 [Do not redistribute.]