### CARNEGIE MELLON UNIVERSITY

### CARNEGIE INSTITUTE OF TECHNOLOGY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# Fingerprinting: Hash-Based Error Detection in Microprocessors

Jared C. Smolens

January 2008

Copyright © 2008 by Jared C. Smolens

All Rights Reserved

### Abstract

Today's commodity processors are tuned primarily for performance and power. As CMOS scaling continues into the deep sub-micron regime, soft errors and device wearout will increasingly jeopardize the reliability of unprotected processor pipelines. To preserve reliable operation, processor cores will require mechanisms to detect errors affecting the control and datapaths. Conventional techniques such as parity, error correcting codes, and self-checking circuits have high implementation overheads and therefore these techniques cannot be easily applied to complex and timing-critical high-performance pipelines.

This thesis proposes and evaluates architectural and microarchitectural *fingerprints*. A fingerprint is a compact (e.g., 16-bit) signature of recent architectural or microarchitectural state updates. By periodically comparing a fingerprint and a reference over an interval of execution, the system can detect errors in a timely and bandwidth-efficient manner. Architectural fingerprints capture in-order architectural state with lightweight monitoring hardware at the retirement stages of a pipeline, while microarchitectural fingerprints leverage existing design-for-test hardware to accumulate a signature of internal state.

This thesis explores two applications of fingerprints. In the Reunion execution model, this thesis shows that architectural fingerprints can detect both soft errors and input incoherence with complexity-effective redundant execution in a chip multiprocessor. Cycle-accurate simulation shows that the performance overhead is only 5-6% over more complicated designs that strictly replicate inputs. In another application, FIRST, fingerprints detect emerging wearout faults by periodically testing the processor under marginal operating conditions. Wearout fault simulation in a commercial processor show that architectural fingerprints have high coverage of widespread wearout, while microarchitectural fingerprints provide superior coverage of both individual and widespread wearout.

## Acknowledgements

First, I thank Professor James C. Hoe, my academic advisor, for guiding and supporting me in my graduate studies and providing a comfortable and productive environment in which to do research. His comments, criticism, and insight over the years have greatly refined my skills in writing, speaking, and independent research.

I also thank Professor Babak Falsafi for his guidance and advice. He has constantly provided me with motivation and a valuable second opinion throughout my time in the graduate program. I also thank my committee members Professor Shawn Blanton and Dr. Shubu Mukherjee for their time, patience, and helpful comments. Their feedback has substantially improved this thesis.

I thank my mentor at Intel Corporation, TM Mak, for supplying me with abundant information on current processor designs and using his extensive contacts to gain access to commercial designs for my research. Without his help and Intel's cooperation, there would be many more open, or even unrecognized, questions in this work. I also thank Sun Microsystems for their generous and timely release of the OpenSPARC RTL and architecture tools. With these resources I was able to quickly prototype and model many of the key ideas in this thesis. Finally, I thank the organizations that funded my research, including the National Science Foundation, Intel Corporation, and the Center for Circuit and System Solutions (C2S2).

My fellow graduate students in the TRUSS group and CALCM also deserve abundant thanks for all of the ways in which they have helped me over the years, including, but not limited to, writing and debugging simulators, coauthoring papers, proofreading papers and this thesis, fixing my talks, and tolerating my awful puns. In order of arrival to the graduate program, I specifically want to acknowledge Tom Wenisch, Roland Wunderlich, Jangwoo Kim, Stephen Somogyi, Nikos Hardavellas, Brian Gold, Eric Chung, and Eriko Nurvitadhi. I also thank Professor Charles Neuman for his advice and running commentary on the state of the world.

I am grateful for the long-standing encouragement, advice, and conversation from my friends and co-workers at Unisys Corporation, particularly Emilio Salgueiro and John Black. My experiences with the large computer systems at Unisys gave me a unique perspective on the industry and cemented my interest and curiosity for computer architecture.

I am thankful for the endless patience, love, and support I have received from my family, Gene, Susan, and Max, and from Yang Wang, who still stays close even when far away.

Finally, I must recognize those who plead: just make it perfect, how hard can it be?

# Contents

| Chapte | r 1: Introduction                                             | 1  |

|--------|---------------------------------------------------------------|----|

| 1.1    | Problem and Scope                                             | 2  |

| 1.2    | Fingerprints                                                  | 4  |

| 1.3    | Thesis contributions                                          | 4  |

| Chapte | r 2: Architectural Fingerprints                               | 7  |

| 2.1    | Fault model                                                   | 7  |

| 2.2    | Architectural Fingerprints                                    | 9  |

| 2.3    | Metrics                                                       | 10 |

|        | 2.3.1 Discussion                                              | 14 |

| 2.4    | Conclusion                                                    | 15 |

| Chapte | r 3: Architectural Fingerprint Implementation                 | 16 |

| 3.1    | Architectural Fingerprints in a Superscalar Out-of-Order Core | 16 |

|        | 3.1.1 P6 Overview                                             | 17 |

|        | 3.1.2 Architectural Fingerprint Constraints                   | 19 |

|        | 3.1.3 Pentium 4 Architectural Fingerprints                    | 23 |

|        | 3.1.4 Evaluation                                              | 24 |

| 3.2    | System-level Implementation of Architectural Fingerprints     | 25 |

|        | 3.2.1 OpenSPARC T1 Overview                                   | 26 |

|        | 3.2.2 System-level Design                                     | 28 |

|        | 3.2.3 Hardware Design                                         | 31 |

| 3.3    | Architectural Fingerprint Synthesis                           | 32 |

| 3.4     | Soft E  | rror Injection Evaluation                | 33 |

|---------|---------|------------------------------------------|----|

|         | 3.4.1   | Methodology                              | 33 |

|         | 3.4.2   | Results                                  | 35 |

| 3.5     | Conclu  | sion                                     | 37 |

| Chapter | :4: Ha  | sh Design                                | 38 |

| 4.1     | Introdu | uction                                   | 38 |

| 4.2     | Backg   | round                                    | 40 |

| 4.3     | Hash A  | Architecture                             | 42 |

|         | 4.3.1   | Design requirements.                     | 42 |

|         | 4.3.2   | Parallel Input CRC units.                | 42 |

|         | 4.3.3   | A Scalable Hash Architecture.            | 44 |

| 4.4     | Hash S  | Structures                               | 46 |

|         | 4.4.1   | Spatial Compactors                       | 46 |

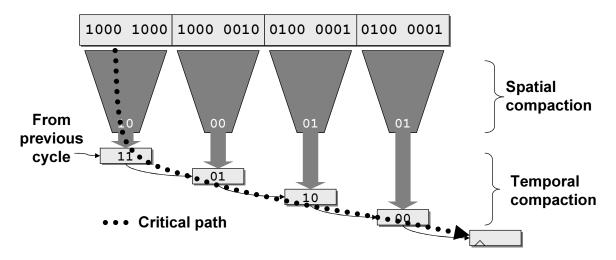

|         | 4.4.2   | Temporal Compactors                      | 49 |

| 4.5     | Evalua  | tion                                     | 52 |

|         | 4.5.1   | Methodology                              | 52 |

|         | 4.5.2   | Empirical Aliasing Properties            | 53 |

|         | 4.5.3   | Synthesis Results for latency and area   | 58 |

| 4.6     | Conclu  | sion                                     | 61 |

| Chapter | : 5: Re | union                                    | 63 |

| 5.1     | Introdu | uction                                   | 63 |

| 5.2     | Backg   | round                                    | 65 |

|         | 5.2.1   | Fault Model                              | 65 |

|         | 5.2.2   | Redundant Execution                      | 66 |

|         | 5.2.3   | Input Incoherence                        | 68 |

|         | 5.2.4   | Output Comparison                        | 70 |

|         | 5.2.5   | Fingerprints over On-Chip Interconnects. | 70 |

| 5.3     | Reunic  | on Execution Model                       | 72 |

|         | 5.3.1   | System Definition                        | 72 |

|         | 5.3.2  | Execution Model                                              | 73  |

|---------|--------|--------------------------------------------------------------|-----|

|         | 5.3.3  | Recovery                                                     | 74  |

| 5.4     | Reunic | n Microarchitecture                                          | 76  |

|         | 5.4.1  | Baseline CMP                                                 | 76  |

|         | 5.4.2  | Shared Cache Controller                                      | 77  |

|         | 5.4.3  | Processor Pipeline                                           | 80  |

|         | 5.4.4  | Serializing Check Overhead                                   | 82  |

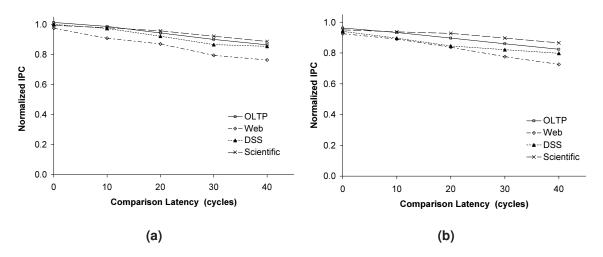

|         | 5.4.5  | Fingerprint comparison interval and latency: analytic model  | 83  |

|         | 5.4.6  | Lock Primitive Implementation                                | 85  |

|         | 5.4.7  | Checkpointing and Re-execution                               | 89  |

| 5.5     | Evalua | tion                                                         | 92  |

|         | 5.5.1  | Baseline Performance                                         | 93  |

|         | 5.5.2  | Checking Overhead                                            | 94  |

|         | 5.5.3  | Reunion Performance                                          | 95  |

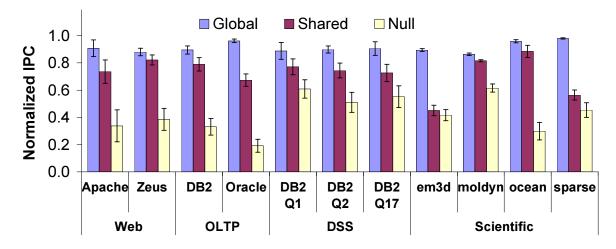

|         | 5.5.4  | Input Incoherence                                            | 97  |

|         | 5.5.5  | Synchronizing request type                                   | 99  |

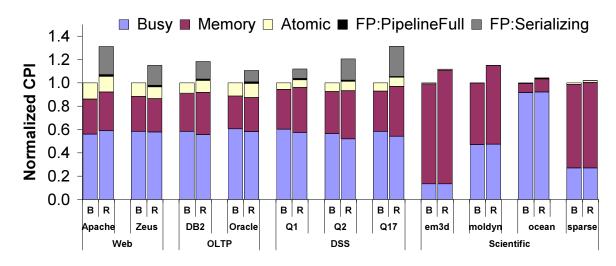

|         | 5.5.6  | Serialization Overhead                                       | 100 |

|         | 5.5.7  | Fingerprinting interval and fingerprints on the interconnect | 101 |

| 5.6     | Conclu | ision                                                        | 103 |

| Charter | . (. M |                                                              | 104 |

|         |        | 8 I                                                          | 104 |

| 6.1     |        |                                                              | 105 |

| 6.2     |        | 8- I                                                         | 105 |

| 6.3     | Metric | S                                                            | 106 |

|         | 6.3.1  | Discussion                                                   | 107 |

| 6.4     | Hardw  | are Design                                                   | 107 |

| 6.5     | Soft E | ror Injection Evaluation                                     | 110 |

|         | 6.5.1  | Methodology                                                  | 110 |

|         | 6.5.2  | Results                                                      | 110 |

| 6.6     | Conclu | ision                                                        | 112 |

### Chapter 7: FIRST

| 7.1     | Introdu | ction                                   | 113 |

|---------|---------|-----------------------------------------|-----|

| 7.2     | Backgr  | round                                   | 115 |

| 7.3     | Detecti | ion with FIRST                          | 116 |

|         | 7.3.1   | Inducing Marginal Operation             | 117 |

| 7.4     | Wearou  | ut Fault Modeling                       | 118 |

|         | 7.4.1   | Wearout Fault Injection Study           | 118 |

|         | 7.4.2   | Wearout Fault Simulation                | 119 |

| 7.5     | Evalua  | tion                                    | 121 |

|         | 7.5.1   | Feasibility of FIRST                    | 123 |

|         | 7.5.2   | Wearout Detection with FIRST            | 125 |

|         | 7.5.3   | The Persistent Nature of Wearout Faults | 134 |

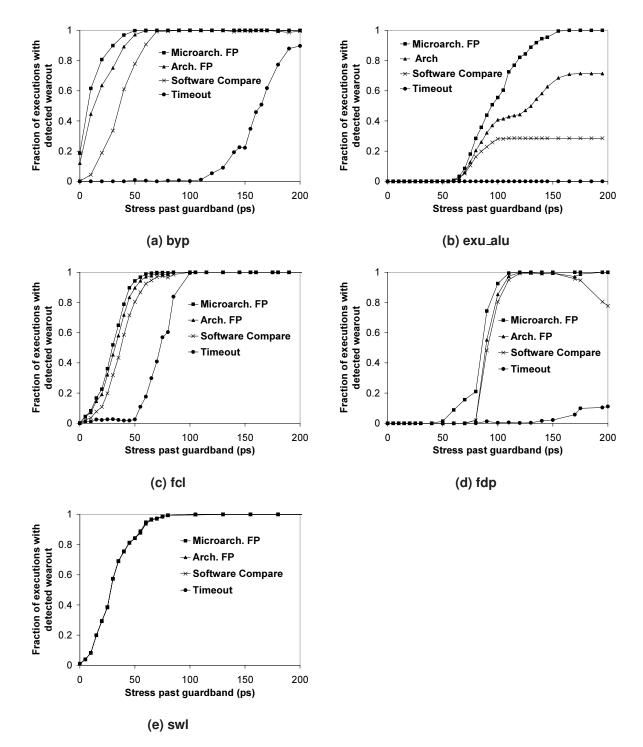

|         | 7.5.4   | Isolated Wearout Faults                 | 138 |

| 7.6     | Conclu  | ision                                   | 139 |

| Chapter | 8: Re   | lated Work                              | 140 |

| 8.1     | Concur  | rrent Error Detection                   | 141 |

| 8.2     | Wearou  | ut Detection                            | 145 |

| Chapter | :9: Co  | nclusion                                | 150 |

| 9.1     | Future  | Work                                    | 151 |

113

# **List of Tables**

| Table 1:  | IA-32 operating environment coverage.                                            | 17  |

|-----------|----------------------------------------------------------------------------------|-----|

| Table 2:  | Stack pointer consumption                                                        | 22  |

| Table 3:  | Software interface to internal architectural fingerprint registers               | 28  |

| Table 4:  | Test programs used in soft error injection.                                      | 35  |

| Table 5:  | Aliasing for spatial compactors with uniform random bit errors                   | 53  |

| Table 6:  | Aliasing properties for temporal compactors over two words                       | 56  |

| Table 7:  | Aliasing properties for temporal compactors over many words                      | 56  |

| Table 8:  | Overall Aliasing properties.                                                     | 57  |

| Table 9:  | Race outcomes during the store-conditional phase of an LL/SC pair                | 88  |

| Table 10: | Simulated baseline CMP parameters.                                               | 92  |

| Table 11: | Simulated workload parameters                                                    | 93  |

| Table 12: | Input incoherence events by phantom request strength, TLB miss frequency         | 98  |

| Table 13: | OpenSPARC structural statistics.                                                 | 123 |

| Table 14: | Fault activation results for the thread scheduler over a range of clock periods. | 124 |

| Table 15: | OpenSPARC processor parameters.                                                  | 125 |

| Table 16: | Test programs used to evaluate FIRST                                             | 126 |

# **List of Figures**

| Figure 1:  | General error detection between a system under test and a reference | 3  |

|------------|---------------------------------------------------------------------|----|

| Figure 2:  | The error detection problem and architectural fingerprints          | 5  |

| Figure 3:  | CDF of error detection as a function of instruction distance        | 11 |

| Figure 4:  | Superscalar retirement and architectural fingerprints               | 18 |

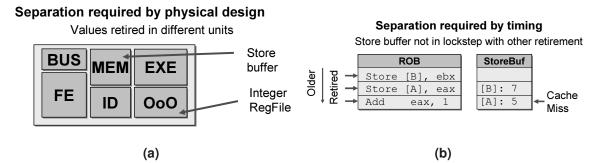

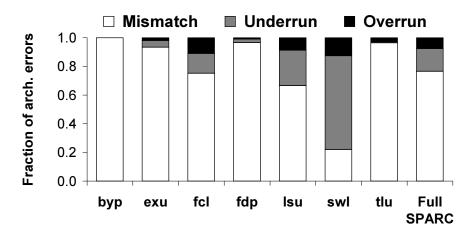

| Figure 5:  | Architectural results separated by location and timing              | 20 |

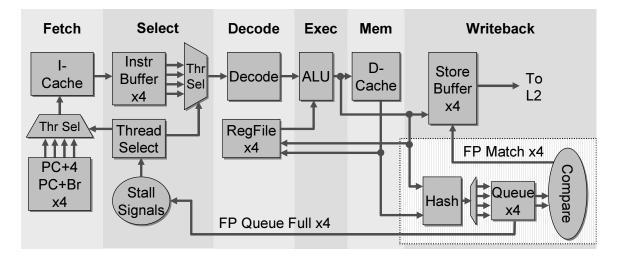

| Figure 6:  | The OpenSPARC T1 pipeline.                                          | 26 |

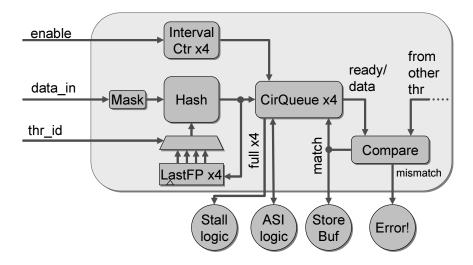

| Figure 7:  | The architectural fingerprint unit in OpenSPARC T1                  | 31 |

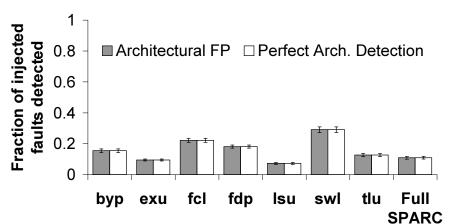

| Figure 8:  | Soft error injection detection results.                             | 35 |

| Figure 9:  | Outcomes where architectural fingerprints detected an error         | 37 |

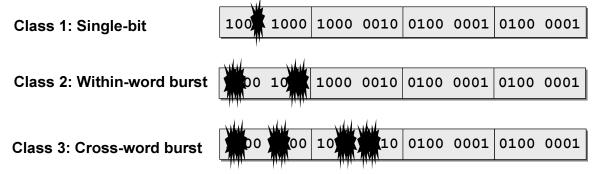

| Figure 10: | Bit error classes.                                                  | 41 |

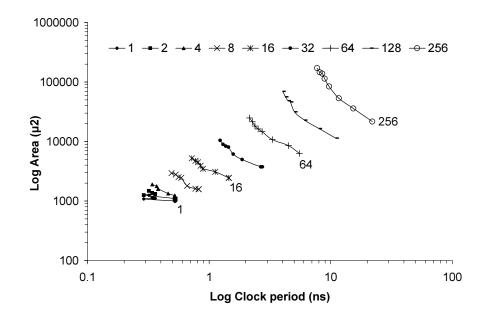

| Figure 11: | Area-delay for N-bit parallel CRC-16 units.                         | 43 |

| Figure 12: | The scalable hash architecture.                                     | 44 |

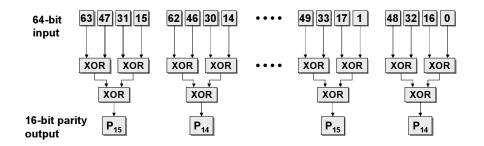

| Figure 13: | A sixty-four to sixteen parity tree-based spatial compactor         | 47 |

| Figure 14: | An eight-to-five X-compact spatial compactor and generator matrix   | 48 |

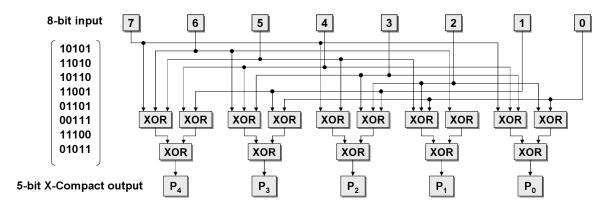

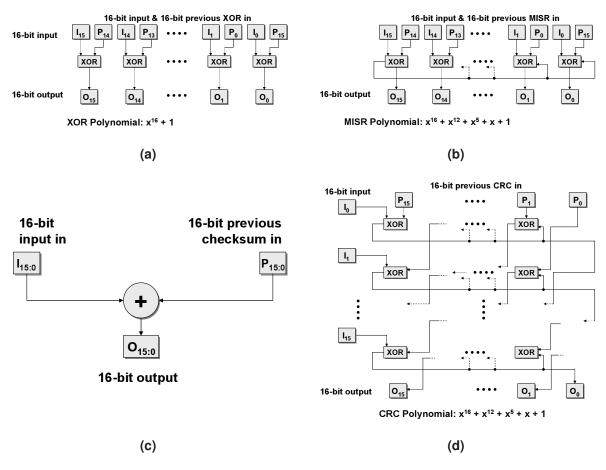

| Figure 15: | Temporal compactors.                                                | 50 |

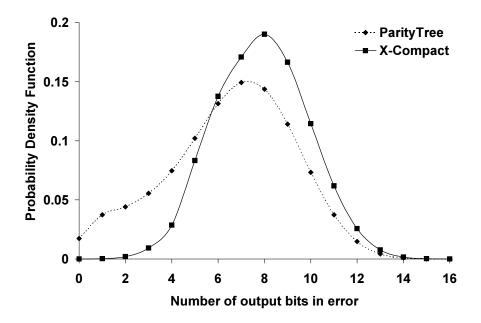

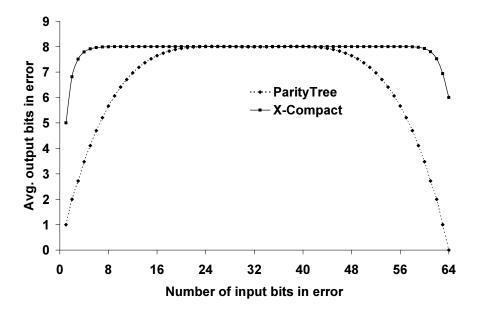

| Figure 16: | PDF of bit errors in spatial compactors                             | 54 |

| Figure 17: | Bits propagated in error by spatial compactors                      | 55 |

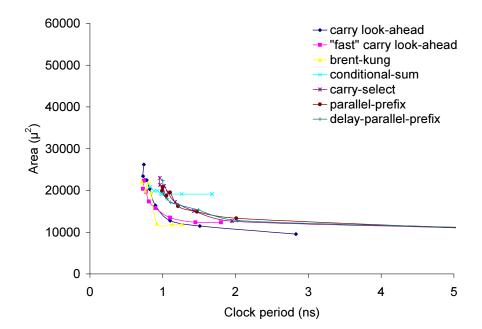

| Figure 18: | Area-latency curves for reference adders                            | 58 |

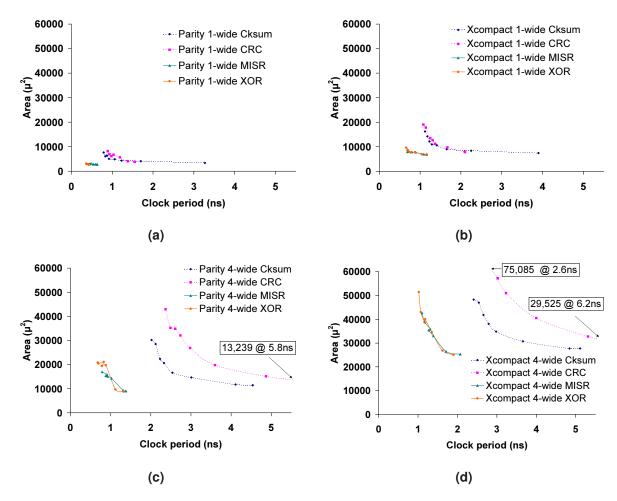

| Figure 19: | Area-latency curves for compactors.                                 | 59 |

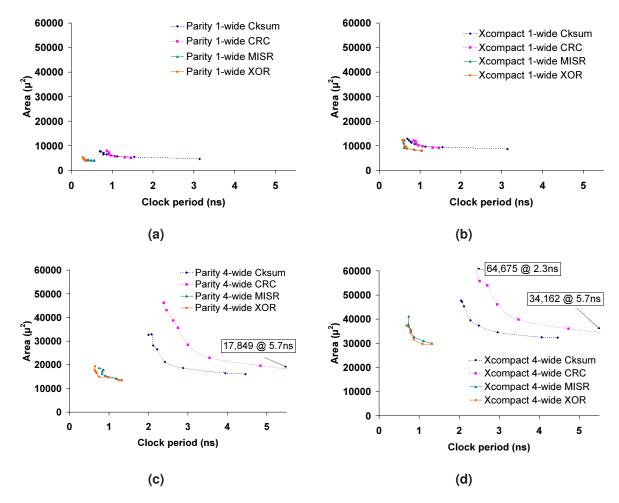

| Figure 20: | Area-latency curves for pipelined compactors                        | 61 |

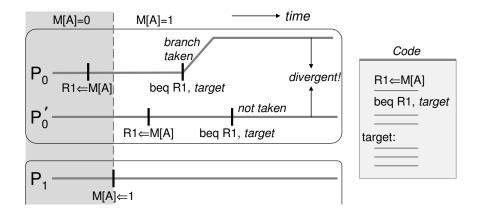

| Figure 21: | Input incoherence on redundant cores.                               | 67 |

| Figure 22: | The Reunion architecture.                                           | 72 |

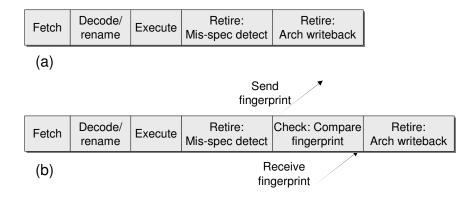

| Figure 23: | Pipelines additions for fingerprint check on retirement.                        | 76  |

|------------|---------------------------------------------------------------------------------|-----|

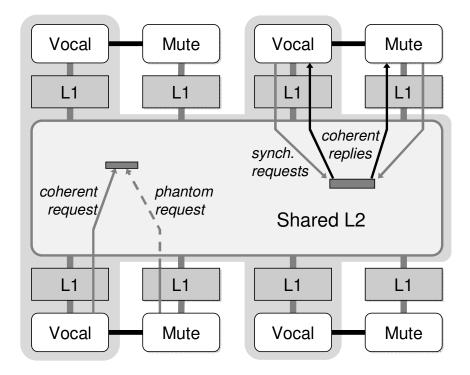

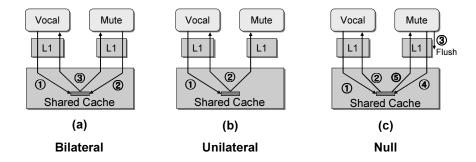

| Figure 24: | Three forms of synchronizing request.                                           | 78  |

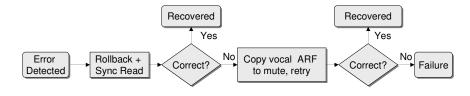

| Figure 25: | The re-execution protocol.                                                      | 81  |

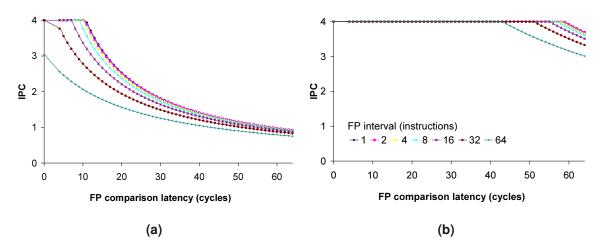

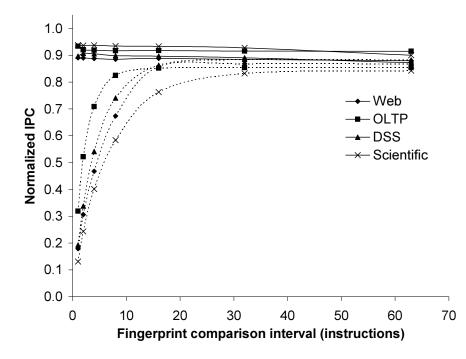

| Figure 26: | Analytic pipeline performance model for architectural fingerprint comparison.   | 85  |

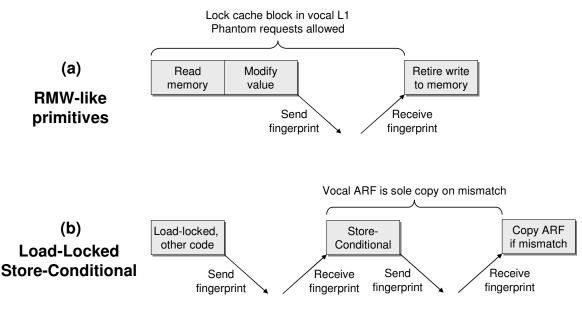

| Figure 27: | Lock implementation.                                                            | 86  |

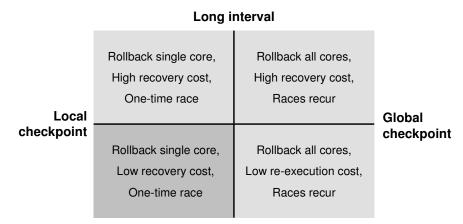

| Figure 28: | Checkpoint and recovery design space.                                           | 90  |

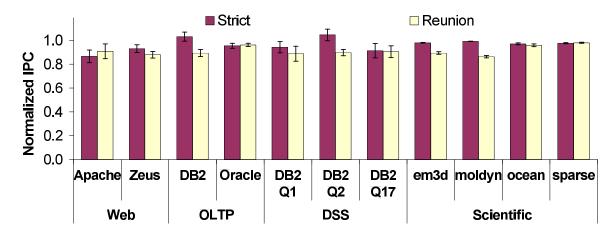

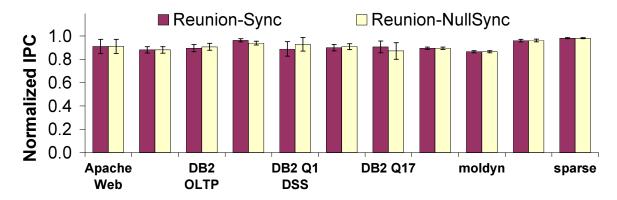

| Figure 29: | Baseline Reunion performance                                                    | 94  |

| Figure 30: | Performance sensitivity of strict and relaxed input replication                 | 95  |

| Figure 31: | Execution time breakdown for the baseline CMP and Reunion                       | 97  |

| Figure 32: | Performance of different phantom request strengths                              | 99  |

| Figure 33: | Performance with bilateral and null synchronizing requests                      | 100 |

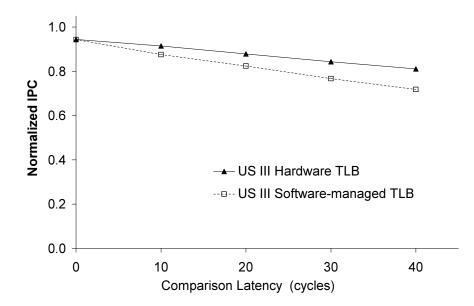

| Figure 34: | Performance with hardware and software TLBs                                     | 101 |

| Figure 35: | Performance with dedicated channels and on-chip memory interconnects.           | 102 |

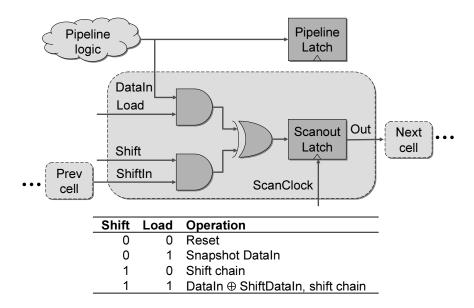

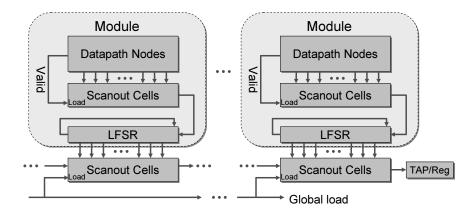

| Figure 36: | The scanout cell                                                                | 107 |

| Figure 37: | Scanout cells applied in a digital circuit.                                     | 108 |

| Figure 38: | Microarchitectural fingerprint design                                           | 109 |

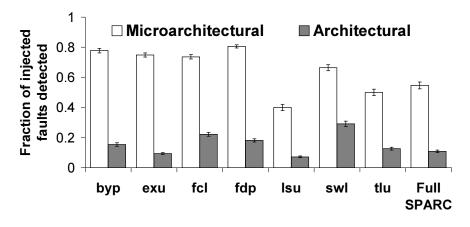

| Figure 39: | Soft error injection detection results                                          | 111 |

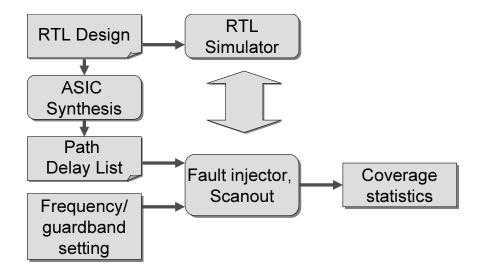

| Figure 40: | The tool flow for modeling wearout faults                                       | 120 |

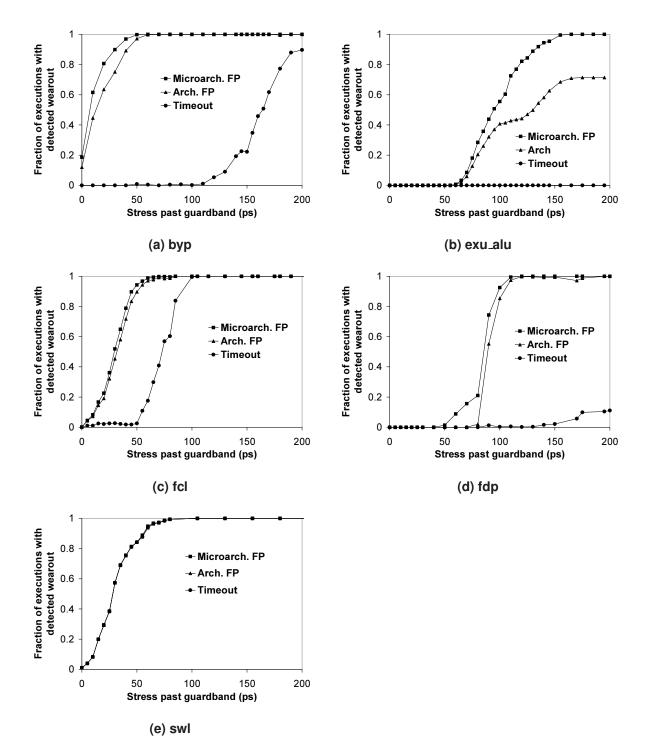

| Figure 41: | Baseline coverage of wearout faults                                             | 128 |

| Figure 42: | Wearout fault coverage by individual test program                               | 129 |

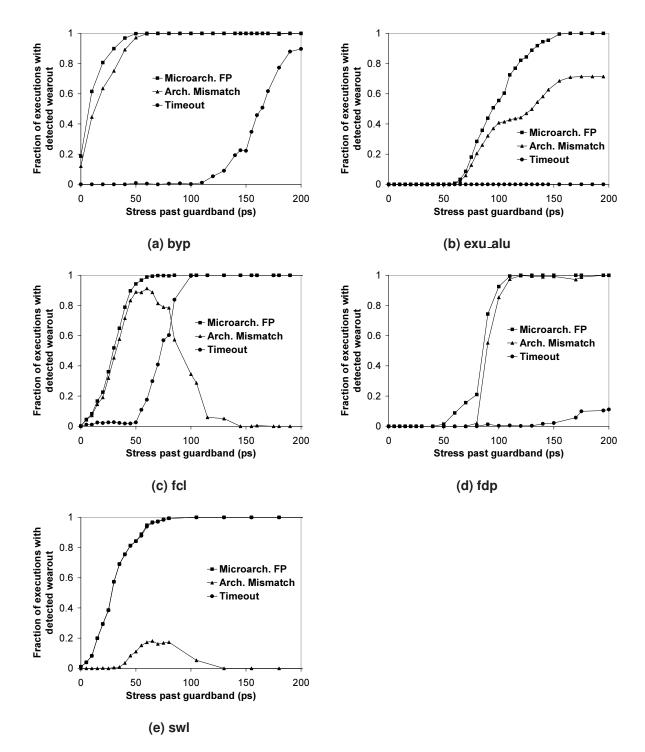

| Figure 43: | Isolated coverage of silent data corruption.                                    | 132 |

| Figure 44: | Coverage using software-based architectural error detection                     | 135 |

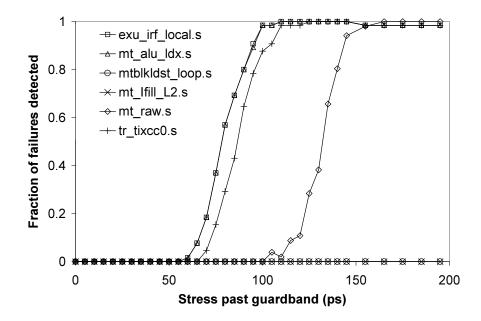

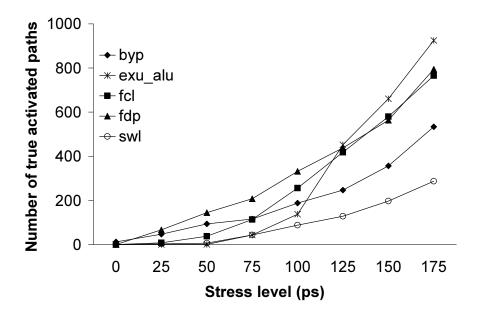

| Figure 45: | The number of true activated paths as a function of stress level for each unit. | 136 |

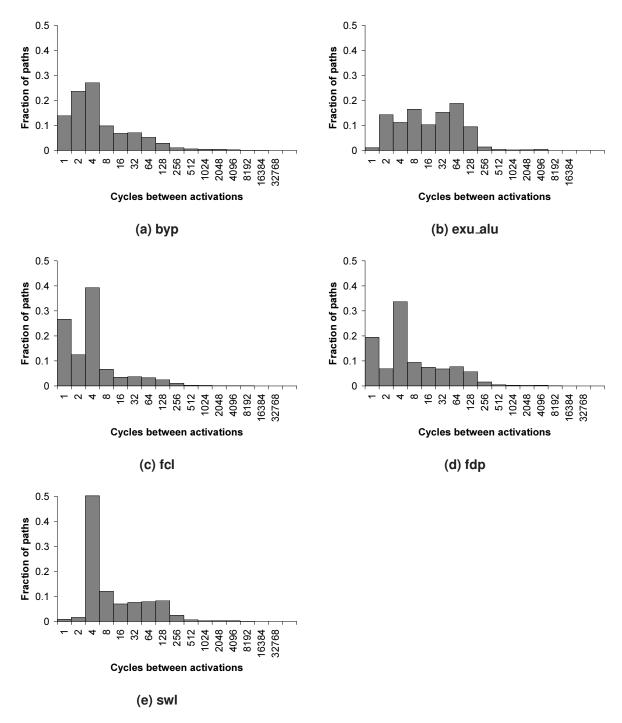

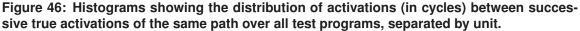

| Figure 46: | Distribution of successive fault activations by unit                            | 137 |

| Figure 47: | Detection coverage for single wearout error site                                | 138 |

### Chapter 1

### Introduction

Reliable computer systems form the backbone of critical information technology infrastructure in today's society. Once billed as the reliable substrate for microprocessors, CMOS circuits are now widely expected to suffer from increasing levels of soft errors and wearout phenomena. With process technologies entering the deep sub-micron regime, process engineers predict that perchip radiation-induced single event upsets in latches and unprotected SRAM will increase exponentially [48, 96]. New sources of intermittent faults will emerge, including process variation, narrowing voltage and thermal noise margins, and aggressive guardbands [22]. Processors will also experience "lifetime reliability" effects, where the smaller device dimensions mean that individual transistors and wires become increasingly susceptible to wearout phenomena including gate oxide breakdown, negative-bias temperature instability, hot-carrier injection, and electromigration [65, 110].

This thesis investigates mechanisms for detecting errors that occur at runtime in a processor core, focusing on two growing threats in modern processors: radiation-induced soft errors and device wearout.

**Soft Errors.** A soft error results from a transient bit upset in a digital circuit. These upsets can occur from sources such as neutrons and alpha particles striking the silicon [121]. Because these upsets originate from external physical sources, they occur at a constant rate over a processor's lifetime; however they cause no permanent damage to the underlying circuit and are therefore considered "soft." When the architectural state (e.g., architectural registers and store values and addresses) dif-

fers from the specified behavior, an architectural error is said to result. An undetected architectural error, called silent data corruption, is a serious concern because these errors can result in incorrect program execution or unexpected application crashes. Architectural errors that are detected, but uncorrected, decrease the reliability and availability of the system; however, the user can be alerted to the possibility of data corruption. With timely error detection mechanisms, a computer system can recover and maintain correct execution with rollback to a checkpoint or voting across redundant units.

**Device Wearout.** Device wearout presents another challenge to reliability. These faults develop initially as "soft breakdown" events that cause transistor switching speeds to gradually slow, while the underlying logical functions are preserved [60, 89]. Therefore, these faults initially do not produce architectural errors during normal execution conditions, but can still be observed by removing the voltage and frequency guardbands. Wearout faults steadily worsen with continued operation. If emerging wearout faults can be revealed in a test before being exposed in normal operating conditions, the system can be repaired or replaced before general-purpose execution is affected, thus preserving the system's reliability and correct operation. Eventually, the wearout faults develop into "hard breakdown," where a device fails catastrophically. Detecting these permanent failures is out of the scope of this thesis.

Without mechanisms to detect soft errors and device wearout, maintaining processor reliability will be an increasing hardship for system designers. Today's processor pipelines are largely unprotected and existing solutions for protection impose unacceptable performance and area overheads or are only applicable to specific functional units.

#### **1.1 Problem and Scope**

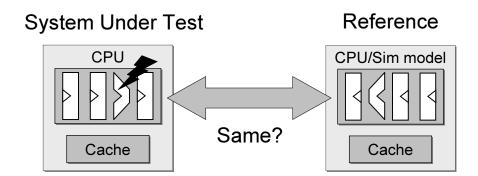

This thesis addresses the problem of timely error detection inside the processor pipeline. Figure 1 illustrates the problem. The system under test—a processor with faults in its datapath—is compared with a reference execution. The error detection mechanism is responsible for continuously comparing the two executions and detecting differences caused by the underlying faults at runtime. Over an interval of execution, the error detection mechanism must determine whether an

Figure 1. General error detection between a system under test and a reference.

error affects execution during the interval or the execution is free of errors. The reference execution can take many forms that mirror the system under test's behavior, including another processor or execution context in an symmetric or asymmetric configuration, a register-transfer level (RTL) model, or even a functional instruction set simulator.

This thesis presents two instantiations of the problem. (1) A concurrent error detection and recovery microarchitecture, called Reunion, where dual-modular redundant (DMR) processor cores symmetrically compact and compare their results against each other to detect soft errors. (2) An in-field wearout detection procedure, called FIRST, where the processor execution is compacted and compared against itself or fault-free RTL models with reduced guardbands to detect developing wearout faults.

Error detection in this thesis is limited to the datapath and control logic in unretired state contained in the processor core. Regular array structures such as caches and architectural register files have well-known and effective information redundancy mechanisms, including parity and error correcting codes (ECC) [100], which are complementary to this work. The complex design and timingcritical nature of high-performance processors precludes the use of such techniques throughout the pipeline.

This thesis identifies three metrics for evaluating error detection mechanisms:

1. *Detection latency* indicates the length of time from a fault's initial occurrence to its detection as an error. This measure is important for ensuring that entire checkpoints and intervals of execution results are free of errors.

- 2. *Comparison bandwidth* is the amount of state that must be compared to check that an execution interval is free of errors. Because buses and pins are a limited resource, the mechanism's bandwidth requirements for periodic and timely are critical to an implementation's feasibility.

- 3. *Error coverage* is the probability of detecting a given error in a timely fashion to successfully isolate or correct the error. Error coverage must be high enough to meet the desired system reliability goals, but is rarely perfect in practice [71].

The scope of this thesis is further constrained to error detection mechanisms that tolerate nondeterminism and function at-speed and at runtime (in the customer's environment). Guaranteeing deterministic behavior during runtime is impractical in many commercial designs. Detection mechanisms must allow some non-deterministic behavior while minimizing false positives and negatives. Furthermore, detection mechanisms must function properly at-speed (i.e., match the core frequency). This requirement is necessary because for soft error detection, processors are only useful products if they run at full speed, while for wearout the fault's initial onset is obscured at lower frequencies. Finally, these detection mechanisms are only useful if they can function at runtime in a customer's environment.

### **1.2 Fingerprints**

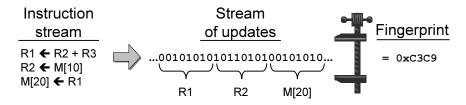

This thesis proposes and evaluates a hash-based detection mechanism, called *Fingerprinting*. A fingerprint is a compact signature (e.g., 16 bits) of a processor's updates to architectural or microarchitectural state which is periodically compared with a corresponding signature from a reference to detect errors. Fingerprinting is conceptually illustrated in Figure 2. Fingerprinting addresses the three metrics above, while permitting limited non-determinism and at-speed detection. They address detection latency by moving the point of detection close to the actual fault. Fingerprints bound the detection bandwidth by compacting updated state into a signature that concisely represents the sequence of state updates produced by the processor over an interval of execution. Finally, by carefully constructing the signature to avoid aliasing, the fingerprint can be engineered to have enough coverage to meet the design's reliability budget [71].

Figure 2: Fingerprints compress architectural and microarchitectural state updates into a compact hash.

### **1.3** Thesis contributions

This thesis proposes and evaluates two realizations of fingerprinting:

- Architectural fingerprints. Architectural fingerprints calculate a deterministic hash of architectural state updates in processors. They permit timely detection of errors that propagate to architectural state. This thesis presents a design and implementation of architectural fingerprints in commercial processor RTL. The results show that an architectural fingerprint unit in a proof-of-concept redundant execution RTL prototype adds less than 4% in area to an already very simple pipeline. Statistical fault injection experiments concretely demonstrate that architectural fingerprints are effective for detecting both soft errors state and widespread device wearout.

- **Microarchitectural fingerprints.** Microarchitectural fingerprints calculate a deterministic hash of microarchitectural state updates internal to a processor. These fingerprints allow spatial and temporal localization of faults within a processor, including those not propagated to architectural state, using existing design-for-test hardware with slight modifications to avoid common sources of non-determinism. This thesis proposes a design for microarchitectural fingerprints in a commercial processor.

This thesis makes the following contributions from studying the feasibility, implementation, and applications of fingerprints:

• Scalable Hash Architecture. This thesis proposes and evaluates a scalable hash architecture for accumulating architectural fingerprints. The proposed hash architecture, an X-compact-like [69] spatial and MISR-based [93] temporal compactor—based on traditional manufacturing test compaction architectures—is modified to compact retiring architectural state. The

design preserves evidence of errors in the output hash as effectively as an ideal cyclic redundancy check (CRC), but can scale to accept the output from wide-issue superscalar processors at a fraction of an equivalent CRC implementation's area and latency.

- **Reunion.** Reunion is a formal execution model for redundant execution across looselycoupled redundant cores in a chip multiprocessor (CMP), using architectural fingerprints. This thesis shows that a key problem in redundant execution, called input incoherence, can be detected and handled with the same mechanisms needed for soft error detection and recovery. The evaluation demonstrates that complexity-effective redundant execution for sharedmemory programs in a CMP can be achieved with only a 5-6% performance overhead over more complicated solutions that use strict input replication.

- Fingerprinting in Reliability and Self Test (FIRST). FIRST is a procedure for in-field wearout detection using microarchitectural fingerprints. FIRST identifies emerging wearout faults before they affect general execution. The study demonstrates that microarchitectural fingerprints are effective for observing both individual and widespread wearout faults. Furthermore, the study shows that architectural fingerprints are equivalent to microarchitectural fingerprints for detecting widespread wearout faults.

The remainder of this thesis is organized as follows. Chapter 2 introduces background and the concept of architectural fingerprints. Chapter 3 explores the implementation of architectural fingerprints in two modern commercial microarchitectures. Chapter 4 explores a range of hash designs for architectural fingerprints. Chapter 5 presents and evaluates the Reunion execution model, an application of architectural fingerprints. Microarchitectural fingerprints are introduced in Chapter 6. Chapter 7 presents and evaluates FIRST for both architectural and microarchitectural fingerprints. Related work is discussed in Chapter 8. This thesis concludes and identifies future research directions in Chapter 9.

### Chapter 2

### **Architectural Fingerprints**

Architectural fingerprints summarize into a compact signature the in-order architectural state updates—the general-purpose register writes and stores to memory—generated by a processor core. Architectural fingerprints expose errors in architectural state that otherwise have a long error detection latency. By periodically comparing small signatures that summarize the monitored state, entire intervals of execution are compared instantly and the comparison bandwidth can be reduced by orders of magnitude over directly comparing each architectural state update. Finally, by leveraging strong but efficient hash functions, fingerprints can avoid aliasing and therefore maintain high error coverage.

This chapter is organized as follows. The important terminology and fault model for this thesis are introduced in Section 2.1. The architectural fingerprint concept is defined in Section 2.2. The metrics for evaluating architectural fingerprints follow in Section 2.3. The following two chapters provide a study of implementing architectural fingerprints in commercial microarchitectures and a detailed study of the architectural hash design, respectively.

### 2.1 Fault model

This section introduces the terminology and fault model for the remainder of this thesis. The terminology in this thesis is adopted from the "minimum consensus" view in the dependable computing community [12].

An *architectural error* is a deviation from the defined correct architectural execution of a processor. In the context of architectural fingerprints, this term is abbreviated to *error*. This thesis is scoped to detecting errors that arise within the microprocessor core data and control paths. Unlike cache memories and external buses, which are excluded, these units are complex and irregular yet still performance-critical. Thus, the core data and control paths cannot easily be protected with traditional information redundancy mechanisms such as parity and ECC [100]. Errors propagating to SRAM arrays (which are increasingly protected by parity and ECC) can be detected as a side effect, but are not the focus of this work.

A *fault* is the hypothesized source of an error. The detection mechanisms considered in this thesis directly detect errors, not the underlying fault. Errors can propagate between components of the processor and produce. However, the error can also remain internal to the processor core or disappear altogether. In this case, the error is *masked*.

**Masking.** Masking occurs on many levels of abstraction. These are summarized below. Errors can be masked *electrically*, for example, an energetic partial strike can generate a transient glitch in logic. This glitch is attenuated by passing through several levels of combinational logic gates. *Logical* masking occurs when controlling inputs on a cone of combinational logic prevent a glitch from propagating. Glitches that reach a latch can still encounter *latch-window* masking unless they arrive in the time window when an input value is recorded by the latch [97]. Latched errors can still be *architecturally* masked if the latched error is overwritten before propagating to architectural registers or store values [73]. Finally, software can also overwrite or ignore errors propagated to architectural values through *program-level* masking. The effects of electrical, latch-window, and program-level masking are out of the scope of this thesis. Therefore, the architectural fingerprints presented in this thesis specifically contend with both logical and architectural masking.

The errors addressed by architectural fingerprints fall into two classes:

**Soft Errors.** Soft errors arise from transient faults that cause or more bit flips in a digital circuit. The underlying fault is a temporary upset and, unless captured in a sequential element such as a latch or SRAM, the effects completely disappear in a fraction of a clock cycle [17]. These faults

include well-documented sources such as energetic particle strikes [121], and decreasing electrical and thermal noise margins [22].

**Device Wearout.** Errors from device wearout are intermittent or "elusive" faults which can be observed as one or more bit flips in a digital circuit. Wearout faults initially cause missed timing (e.g., setup times) in a correctly designed and manufactured circuit because the constituent logic gates and wires gradually operate more slowly. These faults include mechanisms such as the soft breakdown associated with gate oxide breakdown [60], negative-bias temperature instability [87], hot-carrier injection [28] and electromigration [43]. The onset of wearout is gradual over time and the fault activation is exacerbated by environmental and operating conditions such as increased temperature and frequency and reduced voltage [65].

This thesis is concerned with detecting wearout during soft breakdown. Detecting hard breakdown where the device ceases functioning entirely [60] is out of the scope of this thesis, although the presented techniques may also be effective for such faults.

### 2.2 Architectural Fingerprints

Architectural fingerprints are a compact, reproducible, deterministic hash of architectural state updates from a microprocessor. Architectural state consists of general-purpose registers, values stored in memory, and excludes non-architectural information such as cache misses, speculated execution, and timing. The architectural fingerprint is conceptually illustrated in Figure 2 of Chapter 1. Architectural fingerprints between two units—units that are supposed to execute the same program—are periodically compared to detect differences due to architectural errors in the redundant executions. The frequency of comparing architectural fingerprints, measured in instructions, is defined as the architectural fingerprint *comparison interval*. Architectural fingerprints summarize the entire set of architectural results over the comparison interval.

By selecting only architectural state, comparison of the two units is simplified. Rather than requiring redundant processors to execute a program cycle-for-cycle in precisely the same way, the executions need only generate the same results. For a processor core, this means architectural values are sampled for the fingerprint in program order from processor retirement buses, only on cycles when a value is being retired and not on cycles when the buses are idle. For other models, such as functional simulators, this comprises a complete program-order trace of execution. Because the hash is constructed from discrete instruction results, the architectural fingerprint is linked to precise architectural state on instruction boundaries. This property bounds the latency of detecting architectural errors to the fingerprint comparison interval. Furthermore, this eases integration with recovery mechanisms such as checkpoints [4, 66] and precise exception rollback [103], which are generally designed to operate on an architectural instruction granularity.

The redundant units compare fingerprints at regular instruction intervals and at points beyond which recovery mechanisms cannot cross (e.g., non-idempotent operations such as external I/O). Three possible outcomes can result from the comparison. First, the comparison can result in a fingerprint mismatch when the fingerprint values differ, signaling that at least one unit is in error. With two units, the fingerprint comparison can only identify differences, but the fingerprint alone cannot determine which unit is incorrect. Voting can disambiguate this situation with three or more redundant units. Second, the comparison can correctly signal a fingerprint match when no error is present. Finally, the comparison falsely signals a match when, in fact, an error is present but the hashes alias or a common-mode failure causes the same incorrect execution in all units. The final case signifies an undetected error and loss of error coverage.

### 2.3 Metrics

The overall goal of architectural fingerprinting is to detect an error in a processor's architectural state to prevent silent data corruption (SDC) or detected, uncorrectable errors (DUE) [73]. To achieve this, the error detection mechanism must balance three inter-related measures: detection latency, comparison bandwidth, and error coverage. Each of these requirements is discussed in detail below.

**Detection Latency.** The detection latency is the distance between an error occurring and its corresponding effects being observed by the detection mechanism. For architectural fingerprints, the detection latency is measured in instructions. The detection latency is governed by the granularity at which the redundant units are compared. Ideally, errors are detected precisely when and where

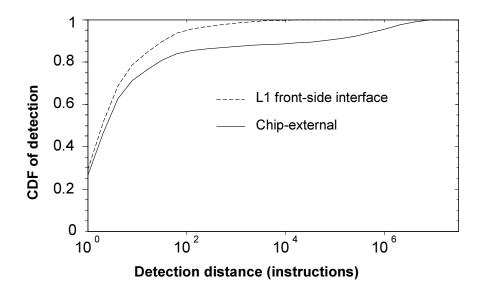

Figure 3: Cumulative distribution function (CDF) of errors detected as a function of instruction distance for a commercial OLTP workload.

they originate, however placing detection logic at every device in the processor is unrealistic. As the detection latency grows, isolating and recovering an error's effect becomes more difficult because the error can propagate to external components. Furthermore, rollback recovery becomes impossible if the processor has performed non-idempotent operations, such as network I/O, which once initiated, cannot be recalled. Hence, a hard bound on the detection latency is critical to maintaining reliability.

Traditional mainframes compare the outputs of lockstepped processors at the chip-external bus pins [16, 95]. These systems can detect errors in the values of writebacks of modified cache blocks or erroneous memory addresses that cause cache misses. While these systems are effective at detecting and isolating errors within a chip, they cannot guarantee the absence of latent errors in the processor core and caches (which have not yet propagated outside of the chip). Because of this long detection latency, recovery becomes complicated in these systems, requiring custom operating systems and applications to support rollback recovery using software checkpoints.

Several research proposals have also considered detection at the L1 cache write port [72, 88]. This observation location improves the detection latency over chip-external detection because errors must only be propagated to a store for detection. Architectural fingerprints can bring the detection latency down to individual instructions. At these short detection latencies,

The detection latency problem is now analyzed quantitatively. Figure 3 shows the fraction of

errors in architectural state propagated to the chip-external and the L1 cache interface within a fixed number of instructions in an on-line transaction processing (OLTP) workload. OLTP is an important commercial workload and is representative of other workloads such as integer SPEC CPU benchmarks. The horizontal axis shows the distance, in instructions, until an error in an instruction result is observable at the L1 cache and chip-external interfaces in a system with a 1MB L2 cache, optimistically assuming program-level masking never occurs (program-level masking furthers increases the error detection latency for errors that are still eventually detected). The vertical axis shows the fraction of instructions with errors detected at that distance for each detection mechanism. The key observation is that a significant fraction of errors (10%) remains undetected, even after executing hundreds or thousands of instructions. These long-and potentially unbounded-latencies can make recovery impossible. Such situations include times when non-idempotent I/O operations (operations that cannot be repeated) have been retired in the meantime. Similarly, for recovery mechanisms within a processor core, such as precise exception rollback [85], error detection mechanisms at the L1 cache and further from the core are insufficient for recovery because errors can be irrevocably committed to architectural register state before they propagate to a store value. This result argues for comparing state updates directly, as with architectural fingerprints, to minimize and bound the detection latency.

In Figure 3, architectural fingerprints reach complete coverage of architectural state within the comparison interval (assuming no aliasing). By directly comparing architectural state before retirement, architectural fingerprints bound the detection latency to the fingerprint comparison interval, a parameter chosen by the system designer. Bounded detection latency is possible because architectural fingerprints directly observe retiring values. Furthermore, the time required to generate an architectural fingerprint hash is minimal. Chapter 4 shows how efficient hashing circuits can update the signature in one processor clock, even in wide-issue superscalar processors.

**Comparison Bandwidth.** The comparison bandwidth counts the number of bits per cycle required to compare the execution of two units. This metric is critical to the system's overall feasibility and implementation cost and is governed both by the comparison granularity and by the comparison interval. Consider systems that directly compare execution state updates. At coarse granularities, such as the chip-external boundary, the required bandwidth is far lower than comparing every latch in the design (hundreds of bits versus millions of bits per clock). However, the cost of comparing at coarser granularities is the increased detection latency. Closer to the processor core, the bandwidth required for direct comparison increases dramatically—matching the retirement bandwidth in the architectural register file and L1 cache write port bandwidth (several hundred bits per cycle). This bandwidth can only be sustained over dedicated on-chip datapaths.

An architectural fingerprint observes as much state as direct comparison at the architectural register file and L1 cache write ports combined, but summarizes the whole sequence instructions into a hash of only a few bytes—which need not be compared every cycle. The fingerprint comparison interval has an inverse relationship with the comparison bandwidth. The Reunion study in Chapter 5 shows that an interval of just sixteen instructions is sufficient to allow comparison fingerprints over the on-chip memory interconnect of a modern chip multiprocessor. A prior study shows that intervals of thousands of instructions are acceptable for error detection across nodes in a distributed shared memory machine [105].

**Error Coverage.** Error coverage measures the fraction of all errors that can be detected before reaching an unrecoverable state. When coverage is imperfect, the processor can suffer from SDC or DUE because they were not detected in time.

Coverage decreases in several ways. First, the aliasing in the detection mechanism itself may cause erroneous state to appear error-free. Second, important state bits may be omitted or ignored in the detection mechanism (e.g., because the state register is difficult to access). Third, the system can mask errors before they reach the detection mechanism. Finally, in spite of the other factors, if the error is detected—but too late to isolate and correct it—coverage is lost. In actual designs, error coverage does need not be perfect, but it must meet a designated error budget [71].

Architectural fingerprints containing errors can alias with architectural fingerprints from errorfree execution, causing a loss of error coverage. The hashes used to generate the fingerprint necessarily lose information as a byproduct of compacting a large number of bits—with some bits in error—to fewer bits. Chapter 4 studies efficient hashes that approach ideal aliasing probabilities over a range of error patterns. Second, for microarchitectural design or physical layout reasons, not all architectural state can be included in the hash. For example, while general-purpose registers are typically written to a central register file, state such as the program counter, stack pointer, and condition code registers may be written to special, individual registers or at times avoided entirely as an architectural optimization. Fortunately, much of this state indirectly appears as part of other architectural state, and is therefore preserved in the fingerprint.

#### 2.3.1 Discussion

Next, this thesis discusses the interaction of the three metrics through the fingerprint comparison interval and two additional system-level requirements for error detection mechanisms.

**Fingerprint comparison interval.** The fingerprint comparison interval is the distance, measured in instructions between successive architectural fingerprint comparisons. The fingerprint summarizes all monitored state updates within the interval. Depending on the context, the interval can be a constant or application-dependent. For example, non-idempotent operations such as I/O can force an architectural fingerprint comparison before the end of a periodic interval. The detection latency is bounded by the comparison interval because the fingerprint summarizes all monitored architectural state updates within the interval. To the first order, comparison bandwidth is inversely proportional to the fingerprint comparison interval because only one fingerprint must be compared for each interval. Finally, error coverage depends on timely detection. If results are not held within the core prior to checking, an excessively-long interval can allow an undetected error to propagate outside of the processor and to an unrecoverable location. By contrast, if the results are held, a long comparison interval can incur a performance loss. These tradeoffs are discussed further in the context of the Reunion execution model in Chapter 5.

There are also two important system-level requirements important to error detection in this work, but independent from the metrics listed above.

**Determinism.** For architectural fingerprints, a processor is considered architecturally deterministic if it always performs the same operations and produces the same architectural outputs for a given sequence of inputs and initial conditions. This is a stronger requirement than functionally correct execution—for a given set of inputs, multiple possible architectural outcomes are correct depending on timing and the outcome of "undefined" outputs [44]. However, architectural determinism does not mean that the microarchitecture must perform precisely the same operations on a cycle-by-cycle basis, as in lockstep. Instead, only the architectural outputs must be deterministic, while the underlying microarchitecture may operate differently, or even be implemented differently, across redundant executions.

Architectural determinism is a concern because a hash-based error detection mechanism cannot discriminate between two architecturally different, yet both correct, outputs and an output containing an error. In both cases, the detection mechanism signals a potential error. In a system with only detection, this behavior decreases the effective reliability of the system by triggering on an error that does not exist. In a system with recovery, this behavior incurs unnecessary recovery operations, which affects performance and potentially leads to problems with forward progress. The latter trade-off is exploited in Chapter 5 with the Reunion execution model.

**At-speed operation.** Second, the error detection mechanism must work at-speed. Systems with runtime soft error detection cannot run more slowly than systems without detection because they must still meet aggressive performance goals in order to be competitive in the marketplace. Early wearout detection must also work at-speed because errors initially appear from timing faults that are only activated when running at the highest operating frequencies. Therefore, both applications require the error detection mechanism to run at-speed.

### 2.4 Conclusion

This chapter introduced the fault model and important terminology for this thesis. The concept of the architectural fingerprint was defined and the metrics for evaluating error detection mechanisms were presented. The following two chapters provide concrete discussion on architectural fingerprint implementation, discussing the mechanics of collecting, assembling, and comparing fingerprints in Chapter 3 and the design for a scalable architectural fingerprint hash unit in Chapter 4.

### **Chapter 3**

# Architectural Fingerprint Implementation

Architectural fingerprints have a rich interaction with the instruction set architecture and microarchitecture designs. The hardware capturing an architectural fingerprint must match the retirement bandwidth of aggressive modern superscalar, out-of-order processor designs, yet contend with the burdens of complicated instruction sets and highly optimized microarchitectures.

This chapter explores the hardware design and implementation of architectural fingerprints in two commercial microprocessor designs. This chapter assumes an understanding of the architectural fingerprints described in Chapter 2. This chapter is organized as follows. Section 3.1 presents a trace-based proof-of-concept implementation of architectural fingerprints in a superscalar out-of-order processor. Section 3.2 presents an RTL architectural fingerprint implementation and redundant execution in a multicore, multithreaded scalar pipeline microarchitecture. This chapter concludes with brief synthesis results for the architectural fingerprint unit and a statistical error injection study to demonstrate the effectiveness of architectural fingerprints for detecting errors in architectural state.

### 3.1 Architectural Fingerprints in a Superscalar Out-of-Order Core

This section describes an investigation of architectural fingerprints in a commercial superscalar, speculative, out-of-order processor core design. The investigation includes a proof-of-concept de-

| Class                                   | State                               | Captured                              |

|-----------------------------------------|-------------------------------------|---------------------------------------|

| Integer 8 general purpose registers Dir |                                     | Directly covered, except ESP          |

|                                         | EFLAGS                              | Partly covered, mask undefined fields |

|                                         | Program counter (EIP)               | Indirectly covered                    |

| Floating-point                          | 8 general purpose registers         | Directly covered                      |

|                                         | 8 MMX registers                     | Directly covered                      |

|                                         | 8 XMM registers                     | Directly covered                      |

|                                         | CR/SR/TR/MXCSR status registers     | Directly covered                      |

|                                         | x87 opcode, FIP, Data PTR registers | Not covered                           |

| Segment                                 | 6 segment registers                 | Directly covered                      |

| Memory                                  | Store addresses and value           | Directly covered                      |

Table 1: State in the basic IA-32 environment that is covered directly or indirectly by an architectural fingerprint.

sign and discusses the architectural and microarchitectural issues that only become apparent when applying the fingerprint concept to an actual microarchitecture (Intel P6).<sup>1</sup>

#### 3.1.1 P6 Overview

This section begins with an overview of the P6 microarchitecture that is relevant for capturing architectural fingerprints. The IA-32 architectural state contained in the P6 which must be captured in an architectural fingerprint is listed in the IA-32 Intel Architecture Software developer's Manual [44] and summarized in Table 1. The table also indicates whether the state can be captured directly or indirectly by an architectural fingerprint. Due to its complexity and decreasing relevance, the x87 floating-point unit is disregarded in this study. However, floating-point values in the modern MMX and XMM architectural registers are covered.

The P6 processor core is a three-wide retirement superscalar, out-of-order IA-32-compatible core, originally shipped as the Pentium Pro [94]. The most recent Core 2 microarchitectures are for the purposes of this study similar in design, except that Core 2 can retire four instructions per cycle. The core speculatively fetches and decodes CISC instructions, in order, into a sequence of RISC-like micro-ops, executes the micro-ops in a superscalar out-of-order core, and retires up to three micro-ops in program order to an architectural register file in each cycle. Micro-ops write

<sup>&</sup>lt;sup>1</sup>This section describes work done while the author had access to RTL models and internal validation tests at Intel Corporation for the later-released dual-core designs of the mobile Intel P6-based microarchitecture (Yonah) and the Intel Netburst microarchitecture (Cedarmill) designs. The discussion in this section is based on the P6 microarchitecture, as described by Shen and Lipasti [94].

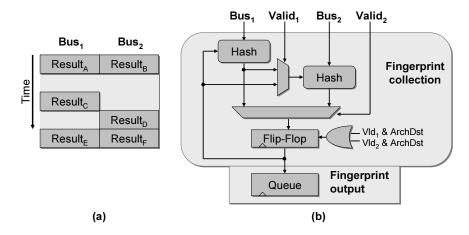

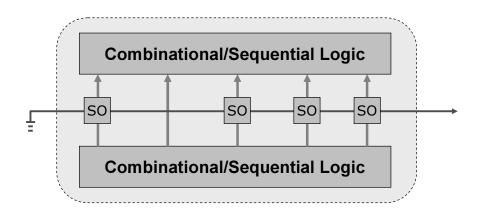

Figure 4: (a) The instruction retirement bus can retire ordered combinations of instructions. (b)The corresponding architectural fingerprint unit.

results to an entire 32-bit register or a portion of the register for legacy instructions. In each cycle, a single store can be written to the store buffer and another store can be committed non-speculatively to the cache. The state in Table 1 is a subset of the total state stored in the architectural register file because there are also temporary registers—registers that are not architecturally-visible—used by micro-ops to execute complex instructions.

Integer, control flow, and load instructions retire values in program order to the integer architectural register over a three-wide retirement bus. Fortuitously, the microarchitecture also guarantees program ordering across the three possible micro-ops retiring in a given cycle because the ROB operates as a FIFO [94]. Alternatively said, any combination of retirement buses can retire architectural results, however the buses are always ordered such that the oldest results always occur on the lowest bus numbers. This greatly simplifies collecting program-order results, as compared to a bus that allows any ordering within the cycle. The retirement combinations over time are illustrated in Figure 4(a), simplified for presentation purposes, to an equivalent two-wide pipeline. On a given cycle, both, one, or none of the buses retire architectural results. New program counter values (EIP in Intel parlance) and condition code values (EFLAGS) are also generated for each retiring microops. This means most values necessary for architectural fingerprints are already available. Valid and destination architectural register number signals exist which identify both when and to which registers a value is being written.

The store buffer has dedicated read and write ports. Values are written back out-of-order, but retired from the store buffer to the L1 data cache in program order. Physical addresses are also

written to the store buffer.

The architectural fingerprint for superscalar values is captured using an architectural fingerprint unit depicted in Figure 4. The figure is simplified for presentation purposes to a two-wide retirement. The hash unit consists of combinational logic, described in detail in Chapter 4. The multiplexer logic ensures that values are collected and hashed in program order. The illustrated logic depth is comparable to the retirement stage selection logic for the final program counter and flags registers, which indicates that the fingerprint unit can have cycle time requirements similar to existing logic.

#### **3.1.2** Architectural Fingerprint Constraints

From the above description, implementation of architectural fingerprints appears straightforward. However, the actual implementation runs into several complications—none insurmountable outlined below. These complications required the implementation of multiple independent fingerprints, based on instruction class, and the addition of simple masking logic.

**Physical design.** The initial concept of an architectural fingerprint called for a single hash of all architectural state. However, the physical design of the core makes this task difficult. The core's floorplan determines how easily various parts of architectural state can be collected and combined in an architectural fingerprint. If all state is nearby, collecting the state together poses few problems. However, processors are physically constrained and retiring data is distributed throughout the processor. For example, in the illustration in Figure 5(a), integer value retirement occurs in the execute unit, while store values are retired in the memory unit. These units can be distant from each other and communication between them requires long, slow global wires.

Instead, independent fingerprints for each output class are much better-suited to addressing the physical design constraints. Related outputs classes are typically stored close together, for example integer values, floating-point values, store values and addresses, and ancillary state, such as IA-32 segment registers are each self-contained.

The additional bandwidth cost of a few (three to four, depending on the architecture) fingerprints is small compared to the bandwidth savings from amortizing comparison across a fingerprint interval. Furthermore, the additional bandwidth may already come for free. For example, if an on-chip memory interconnect is used for transferring fingerprints, the message payload size may already be

Figure 5: Architectural fingerprints need to be generated by output class because of (a) physical design constraints and (b) ordering and timing constraints.

optimized for larger 64-bit transfers [113], which allows a handful of fingerprints to be included at no additional cost over a single fingerprint value.

Asynchronous and delayed outputs. The retirement stages of a microprocessor need only provide the illusion of program-order retirement. The actual implementation can write values to durable architectural state out of program order. This occurs on both the architecture level and microarchitecture levels. In IA-32 and most modern architectures, an example of the former situation is that the memory consistency model allows implementations to delay stores from committing to the global memory ordering (through the use of a store buffer), even after subsequent instructions have retired from the reorder buffer (ROB) to the architectural register file. Figure 5(b) illustrates the reorder buffer retiring subsequent instructions, while the store buffer delays committing older stores to cache because of a write miss. An example of the latter situation is that, related values, such as store addresses and values may be read in order, but in different pipeline stages, meaning that the values needed for architectural fingerprints are available, but not necessarily at the precise cycle time—or in the order—desired.

This problem is also largely solved by the same solution as for physical design: separate architectural fingerprints for each instruction class. This solution works because values within the same class are still retired in program order with respect to each other (e.g., integer register values and stores both retire in program order with respect to other integer register values and stores, respectively). The delayed store address problem is solved trivially by adding a staging latch to hold the value until the address becomes available. **Undefined outputs.** Some architectural outputs are nebulously defined to be "undefined" in the architecture specification [44] (this designation is not unique to IA-32, however). For these outputs, the retiring value cannot be guaranteed to be the same from one execution to another of the same program. This affects architectural fingerprints because an undefined value can cause two fingerprints to mismatch, even when no errors are present. In IA-32, a number of EFLAGS fields are undefined for several integer arithmetic and logical instructions. If a microarchitecture provides a consistent output for these fields then the fingerprint will always match. However, if there are situations where an undefined field depends on internal non-architectural state (i.e., timing-specific microarchitectural state or values on the bus, such as some architecture-specific registers), these values cannot be dependably captured in a fingerprint.

In P6, the values for these "undefined" fields are well defined in the RTL implementation. Therefore, if architectural fingerprints are compared solely between two identical microarchitectures with predictable outputs, the problem is eliminated. However, if the architectural fingerprint is compared against another reference that generates a different value, the undefined value problem must be addressed. This issue is encountered with the architectural co-simulator for P6 (a C program that validates the architectural results of the RTL model). If the entire EFLAGS register is used for an architectural fingerprint, the fingerprints generated between these two models will differ, despite both executions being legal.

A solution to this problem is to mask known undefined fields from the architectural fingerprint. This requires control logic to detect the condition and mask the aberrant bits to produce a predictable value. This solution fails if the undefined value is used in subsequent instructions through program dataflow. However, any program that does this should not be expected to work.<sup>2</sup>

**Microarchitectural Optimizations.** Optimizations for power and performance can eliminate frequent operations performed in a microarchitecture, which while architecturally defined, do not need to be strictly maintained in the microarchitecture. For example, the IA-32 architecture has a limited number of architectural registers and therefore makes extensive use of the stack pointer (known as ESP) to push and pop local values between the architectural registers and the stack.

<sup>&</sup>lt;sup>2</sup>The Intel developer's reference states "Developers must not rely on the absence of characteristics of any features or instructions marked 'reserved' or 'undefined'." [44].

| Original error                                                    | Condition                                                                                   | Outcome                |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------|

| ESP as source for load address                                    | Wrong value is loaded from the wrong address<br>Correct value loaded from the wrong address | Detected<br>Undetected |

| ESP as source for store address                                   | Store address incorrect                                                                     | Detected               |

| ESP as source for data process-<br>ing instruction or store value | Propagated to arch. reg or store value<br>Masked in arch. reg or store value                | Detected<br>Undetected |

| Incorrect value written to ESP                                    | Arch. fingerprint created for explicit write                                                | Detected               |

Table 2: Situations where ESP is consumed or updated and the corresponding detection scenarios.

In recent implementations, the ESP is only updated in limited circumstances—not always when architecturally defined and sometimes only due to microarchitecture-specific timing conditions. Therefore, when blindly observing at retiring register values, updates to the ESP can appear non-deterministic. Recent P6 implementations contain a dedicated stack pointer engine to the pipeline to improve power efficiency and reduce micro-ops per macro-instruction within the pipeline (Gochman describes this mechanism [38]). In the original P6 architecture, every macro-instruction which updates the stack pointer incurs one micro-op to do so, even if the result is never used. This optimization removes most of these micro-ops by calculating the new stack pointer at decode using a small adder in a dedicated stack engine. The architectural register file is only updated with a micro-op only when an instruction architecturally needs to read the ESP, when the register is explicitly changed by the programmer (e.g., by a move to ESP), or when the pipeline needs to restart (e.g., on mis-speculation and traps). These situations can only be fully determined dynamically.

The solution to this microarchitectural optimization is similar to the masking solution for undefined values. The microarchitecture allows inference of whether the ESP is updated by an injected micro-op or by an instruction explicitly specified by the programmer. Therefore, the fingerprint can dependably include the latter case, but ignore the former. This can cause a loss of error coverage in cases enumerated in Table 2. However, the cases where errors in the ESP cannot be detected indirectly are also cases where the ESP value is already masked, and therefore the error can be derated. The last case can be identified with existing microarchitectural signals and safely captured in the fingerprint. **Variable output widths.** The values written to architectural registers and memory are sometimes a different size than the processor's native width (for example, 64-bit processors are becoming more prevalent, yet they continue to run programs that operate on 32-bit integers and byte-sized string elements). Most architectures provide an interface for these narrow stores to memory; IA-32 also allows writes of narrower widths to architectural registers.

These varied widths generally do not present a problem with respect to architectural fingerprints. As with undefined outputs, masking logic can be used to zero-extend the missing output bits to match the native machine width.

**Micro-op Ordering.** Finally, because the P6 implements CISC instructions—which may have multiple outputs—as a sequence of micro-ops, the retirement order of the constituent micro-ops in an instruction matters for architectural fingerprints. If the ordering of micro-ops for the same complex instruction differs from implementation to implementation or even within a single implementation, the architectural fingerprints will mismatch. The microcode is read from ROM tables. Therefore, in general, the microcode outputs values in a predictable order (in spite of the myriad instruction variants and operating modes). This issue proves not to be a problem in practice.

#### **3.1.3** Pentium 4 Architectural Fingerprints

Architectural fingerprints for the rapidly-disappearing Netburst (also known as Pentium 4) microarchitecture were also briefly investigated.

The most significant difference between the P6 and Netburst microarchitectures, with respect to architectural fingerprints, is in the retirement procedure. Instead of writing retired register values to an architectural register file in program order, Netburst speculatively writes architectural register values to a physical register file that is accessed through an architectural to physical register map table [20]. At retirement, only the updated register mapping is written, in program order, to an architectural register map table. However, the values always remain in the physical register file. Furthermore, because the machine speculates aggressively, the values written to the physical register file are frequently re-written during "replays" of a speculative instruction. Furthermore, if the instruction is on the wrong-path, the final register mapping may never be retired.

This speculative writeback means that architectural fingerprints cannot be implemented in the existing Netburst microarchitecture without significant changes. Nowhere in the microarchitecture can architectural values be observed in program order. In principle, architectural fingerprints can be constructed in Netburst and other physical register file-based machines in the same way as for P6; however, the costs are prohibitive. To construct an architectural fingerprint, the values must be read out of the physical register file at retirement. To avoid impacting performance through register file port contention, this solution needs additional register file read ports that match the retirement width of the processor. This is an expensive addition in area, timing, and power to an already highly ported structure [34] and therefore makes implementing architectural fingerprints expensive in Netburst.

#### 3.1.4 Evaluation

This section presents the evaluation of the trace-based proof-of-concept architectural fingerprint implementation on a P6 RTL model.

#### Methodology

The P6 architectural fingerprint experimental setup consists of a single-core full-chip Yonah RTL model, including L2 cache and external memory, Perl-based trace collection tools, a modified version of the C-based functional x86 architectural co-simulator called archsim, and off-line trace analysis tools.

The RTL model loads and executes compiled memory images of assembly-based functional validation test programs, following a brief processor initialization and reset sequence. On every cycle during simulation, the trace collection tool monitors hand-selected internal RTL signals, latches retiring values, and dumps the raw output, cycle-by-cycle, to a trace file. This models the hardware required to capture architectural values from the actual processor. Separately, the modified architectural simulator also produces an architectural state trace for the same program.

The RTL and architectural simulator traces are processed to calculate architectural fingerprints for each architectural result, separated by physical location into different classes for integer values, floating-point values, store values and address, and x86-specific segment registers. The functional simulator has no concept of timing, while the RTL model produces detailed timing information, so the relative order of each fingerprint class differs as discussed earlier. The trace analysis tool compares sequences of each class separately. The analysis tool reports matches over the full execution of the test program and reports mismatches immediately. No errors were injected in this evaluation.

#### Results

The simulation methodology outlined above was applied to over sixty focused x86 ISA validation programs, twelve cache validation programs, the dhrystone benchmark, a paging test with virtual memory enabled, and a suite of hand-written assembly programs.

In all cases, the architectural fingerprint implementation in both the RTL monitor and archsim matched. This simulation model required numerous revisions, as new instructions and behaviors were encountered. Furthermore, architectural fingerprint also proved to be a highly-sensitive bug detector for its own implementation—whenever a single piece of state was missing or sampled at the wrong time, the architectural fingerprint was clearly different from the architectural simulator and clearly identified a specific dynamic instruction that needed investigation.

This trace-based proof-of-concept demonstrates that the data necessary for assembling architectural fingerprints is available in real superscalar out-of-order microarchitectures. Furthermore, the data can be collected feasibly with modest hardware additions for masking.

## **3.2** System-level Implementation of Architectural Fingerprints

This section studies the implementation of architectural fingerprints in the multicore, multithreaded, scalar OpenSPARC T1 processor RTL model. This study fulfills several goals. First, this study serves as a substantive demonstration of architectural fingerprints working in a commercial processor design. Second, this study quantifies the coverage of architectural fingerprints for soft errors and demonstrates that they are effective detection mechanisms for silent data corruption. Third, this study demonstrates redundant execution with architectural fingerprint comparison in both multithreaded and multicore designs. Finally, this study explores a system-level implementation where architectural fingerprint values are exposed to higher-level processes.

Figure 6: The OpenSPARC T1 6-stage pipeline with architectural fingerprint collection and comparison hardware. Pipeline figure adapted from [113].

## 3.2.1 OpenSPARC T1 Overview

This section gives an overview of the OpenSPARC T1 microarchitecture, as it relates to fingerprinting. The microarchitecture is simple enough to permit prototyping of architectural fingerprints and redundant execution directly in the RTL model.

The OpenSPARC T1 consists of eight scalar in-order processor cores. Each core selects dynamically from up to four hardware thread contexts on every cycle. The simplified pipeline is illustrated in Figure 6. The portions that relate to architectural fingerprints are now described. In the writeback stage, the pipeline determines if the instruction can retire (or, alternatively, triggered an exception). If the instruction is declared safe, the pipeline writes register values in-order into an architectural file through two write ports. One port is dedicated to values from the ALU and another for so-called "long-latency" operations such as loads and floating-point operations which can take a variable amount of time to complete (the single floating-point unit is shared across all eight cores on the chip). On any cycle, a given thread can have at most one value retiring to the register file, although two different threads can simultaneously write values. Store values and addresses are written into a dedicated eight-entry store buffer for each thread. These values are subsequently written back to the shared L2 cache.