# 18-643 Lecture 11: Memory Bound Designs

James C. Hoe Department of ECE Carnegie Mellon University

18-643-F23-L11-S1, James C. Hoe, CMU/ECE/CALCM, ©2023

# Housekeeping

- Your goal today: see examples of customizing memory paths to algorithms, and vice versa

- Notices

- Handout #5: lab 2, due noon, 10/9

- Project status report due each Friday

- Readings (see lecture schedule online)

- Kung, "Memory requirements for balanced computer architectures," ISCA 1986.

- Williams, et al., "Roofline: an insightful . . .," 2008

### **Topic 1: Arithmetic Intensity**

Last time

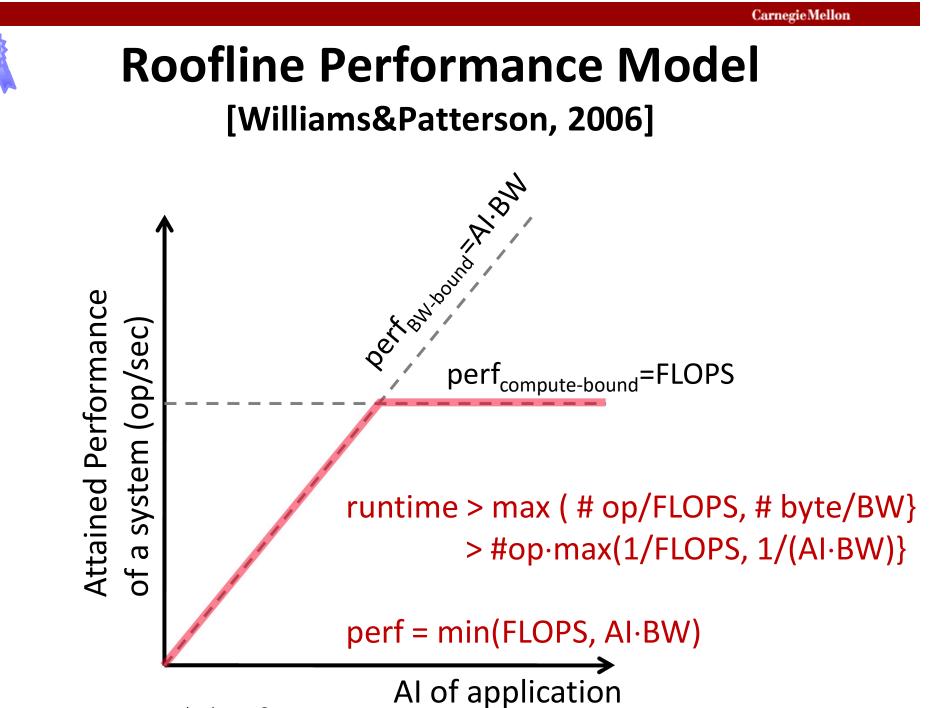

# **Arithmetic Intensity**

- An algorithm has a cost in terms of operation count

- runtime<sub>compute-bound</sub> = # operations / FLOPS

- An algorithm also has a cost in terms of number of bytes communicated (ld/st or send/receive)

- runtime<sub>BW-bound</sub> = # bytes / BW

- Which one dominates depends on

- ratio of FLOPS and BW of platform

- ratio of ops and bytes of algorithm

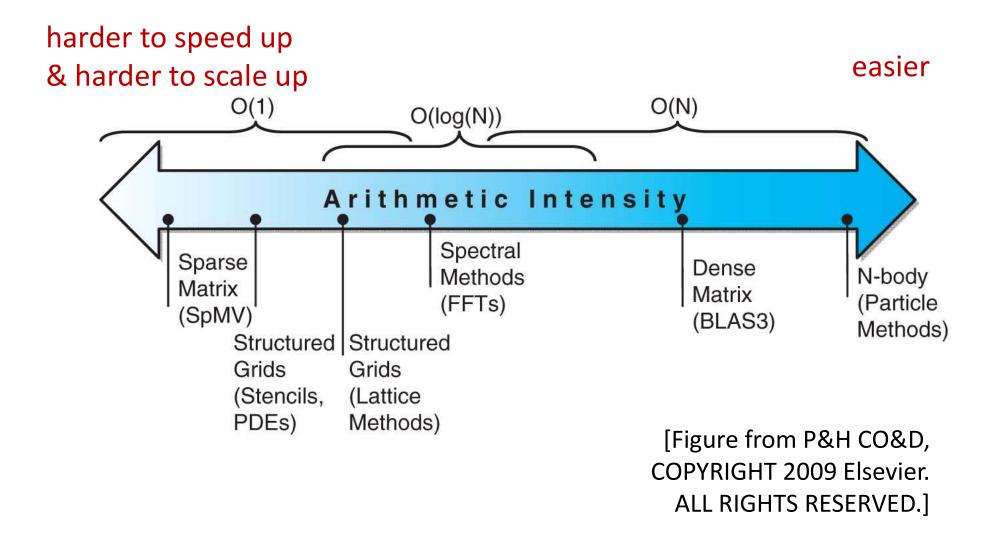

- Average Arithmetic Intensity (AI)

- how many ops performed per byte accessed

- # operations / # bytes

### **Al and Algorithms**

### Simple AI Example: MMM

```

for(i=0; i<N; i++)

for(j=0; j<N; j++)

for(k=0; k<N; k++)

C[i][j]+=A[i][k]*B[k][j];</pre>

```

- N<sup>2</sup> data-parallel dot-product's

- operation count: N<sup>3</sup> float-mult and N<sup>3</sup> float-add

- External memory access (assume 4-byte floats)

- assume N is large s.t. 1 row/col too large for on-chip

- $-2N^3$  4-byte reads (of **A** and **B**) from DRAM

$- \ldots \mathbf{N}^2$  4-byte writes (of **C**) to DRAM . . .

• Arithmetic Intensity  $\approx 2N^3/(4 \cdot 2N^3)=1/4$

GTX1080: 8 TFLOPS vs 320GByte/sec

### Less Simple AI Example: MMM

for(i0=0; i0<N; i0+=Nb)

for(j0=0; j0<N; j0+=Nb)

for(k0=0; k0<N; k0+=Nb) {

for(i=i0;i<i0+Nb;i++)

for(j=j0;j<j0+Nb;j++)

for(k=k0;k<k0+Nb;k++)

C[i][j]+=A[i][k]\*B[k][j];

}</pre>

- Imagine a 'N/N<sub>b</sub>'x''N/N<sub>b</sub>' MATRIX of N<sub>b</sub>xN<sub>b</sub> matrices

- inner-triple is straightforward matrix-matrix mult

- outer-triple is MATRIX-MATRIX mult

- To improve AI, hold N<sub>b</sub>xN<sub>b</sub> sub-matrices on-chip for data-reuse

18-643-F23-L11-S8, James C. Hoe, CMU/ECE/CALCM, ©2023

### AI of blocked MMM Kernel (N<sub>b</sub>xN<sub>b</sub>)

```

for (i=i0;i<i0+N<sub>b</sub>;i++)

for (j=j0;j<j0+N<sub>b</sub>;j++) {

t=C[i][j];

for (k=k0;k<k0+N<sub>b</sub>;k++)

t+=A[i][k]*B[k][j];

C[i][j]=t;

}

```

- Operation count: N<sub>b</sub><sup>3</sup> float-mult and N<sub>b</sub><sup>3</sup> float-add

- When **A**, **B** fit in scratchpad (2xN<sub>b</sub><sup>2</sup>x4 bytes)

- 2xN<sub>b</sub><sup>3</sup> 4-byte on-chip reads (A, B) (fast)

- $-2xN_{b}^{2}$  4-byte off-chip DRAM read **A**, **B** (slow)

- 2xN<sub>b</sub><sup>2</sup> 4-byte off-chip DRAM read/write of C (slow)

- Arithmetic Intensity =  $2N_b^3/(4 \cdot 4N_b^2) = N_b/8$

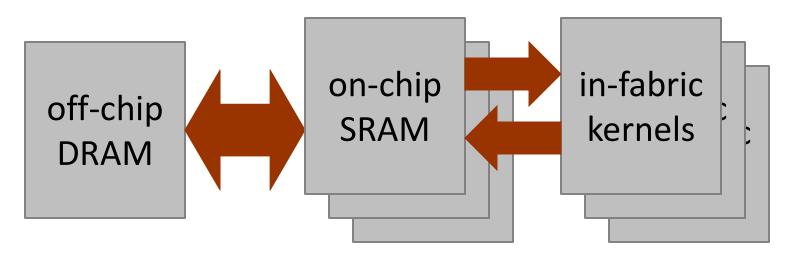

# **The Performance Balancing Act**

- Kernels' op/sec requires some byte/sec a function of algorithm and kernel size

- 2. On-chip SRAM "filters" kernel **byte/sec** down to DRAM **byte/sec** a function of SRAM **capacity**

- 3. DRAM system offers some aggregate byte/sec

a function of access pattern (algorithm)

### Some Hints on Lab 3

- Lab 3 kernel's op/sec just need to be fast enough to match memory-bound (op/byte × byte/sec)

- Lab 3 emphasis on improving memory-bound

- size tiles and order outer loops for data reuse (don't forget the batch loop!)

#### Mindful of buffer sizes and degree reuse

- use memory resources efficiently (fit bigger tiles)

- layout data in DRAM for sequential read (don't forget to widen the read path)

- Use DFX to tune the 2 layers differently

# Topic 2: Data Layout and Access Pattern

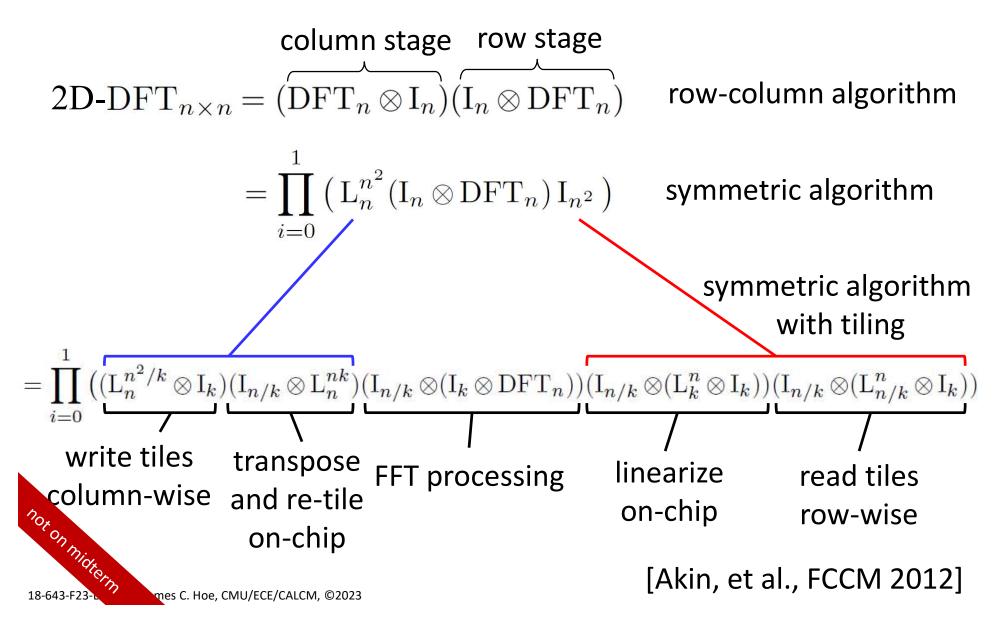

# **Data Layout and Access Pattern: 2D-FFT**

• Row-column algorithm:

$$2D-DFT_{n \times n} = (DFT_n \otimes I_n)(I_n \otimes DFT_n)$$

Column Stage Row Stage

Dataset:

(Logical abstraction

of the 2D dataset)

....

of

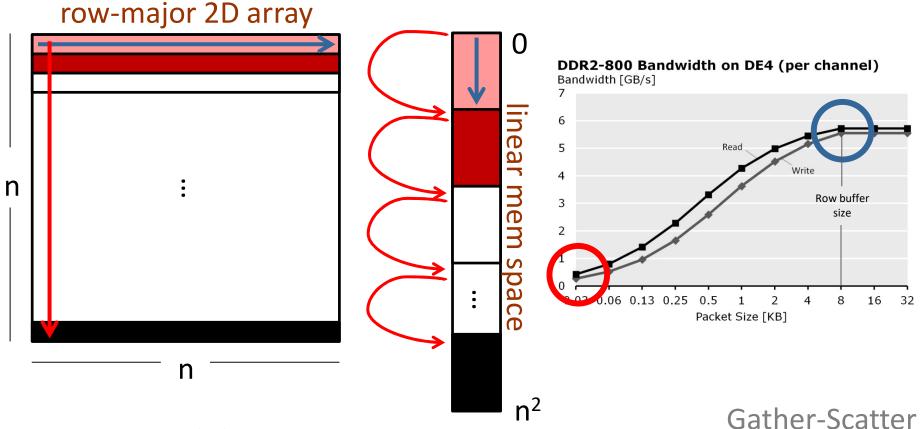

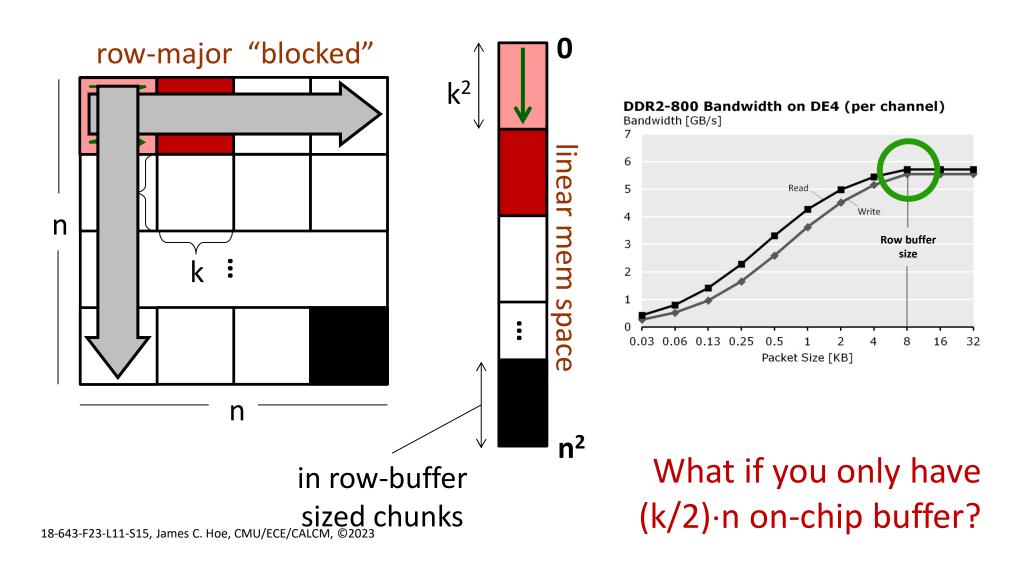

### **Inefficient DRAM Access Patterns**

- Row-wise traversal -> Sequential accesses

- Column-wise traversal -> Large strided accesses

#### **Tiled Layout and Access Patterns**

# Design Generator w/ Tensor Formalism

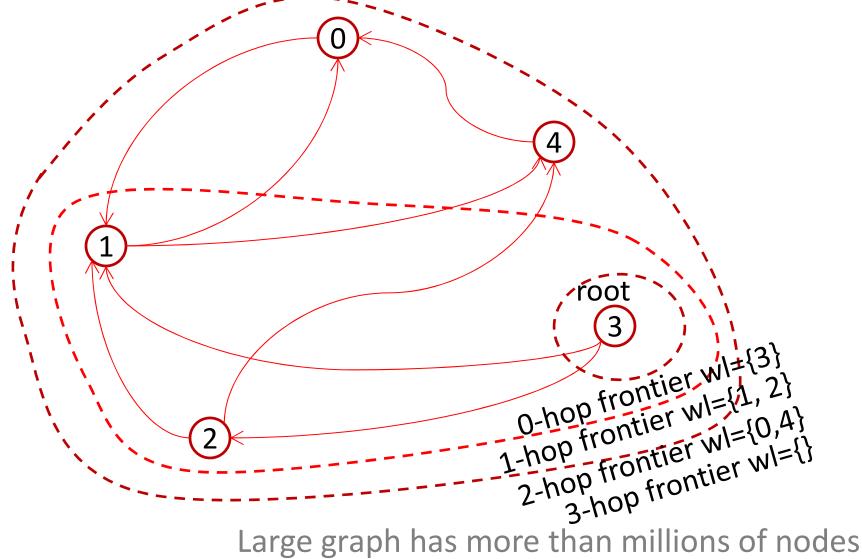

# **Topic 3: Irregular**

with may be handful edges per node

18-643-F23-L11-S18, James C. Hoe, CMU/ECE/CALCM, ©2023

### **Breadth-First Search (Pseudo Code)**

```

foreach (node n in graph) n.dist=\infty;

worklist = {root}; root.dist=0;

foreach (node n in worklist) {

foreach (neighbor of n) {

if (n.dist + 1 < neighbor.dist) {</pre>

Has Parallelism?

Yes, not perfect,

input-dependent

neighbor.dist = n.dist + 1;

add neighbor to worklist;

}

```

(see http://iss.ices.utexas.edu/?p=projects/galois/ benchmarks/bread\_first\_search)

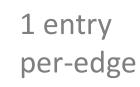

### **Real Code with CSR Memory Accesses**

```

while(wl.mHowmany) { // worklist not empty

// repeat for each node on frontier

int curr=wl.mList[wl.mDeq];

// S0

int myDist=graph->mPerNode[curr].dist;

// S1

// S1

int scan=graph->mPerNode[curr].edges;

{ ... dequeue from worklist ... }

while (numEdges--) {

// repeat for each neighbor

int dest=graph->mPerEdge[scan].dest;

// S2

int destDist=graph->mPerNode[dest].dist;

// S3

if ((myDist+1)<destDist) {</pre>

// S4

// S4

graph->mPerNode[dest].dist=myDist+1;

{ ...enqueue dest to worklist...}

// S5

}

scan++;

}

```

# Compressed Sparse Row (CSR) Adjacency Matrix

3

dense sparse

$dest \rightarrow$ Src-2 3 0 1 1  $\mathbf{O}$ 1 ()1 1 () $\mathbf{O}$ ()2 1 1  $\mathbf{O}$ ( ) 3 1  $\bigcap$ ( ) 0 3

array indexed by row/src idx (holds offset into element array) 0 1 2 2 3 5 1 entry per-node

3

array of all non-0 elements in row-order (holds col/dest index)

3

1

0

Large graph has millions or more nodes each with may be handful edges per node

18-643-F23-L11-S21, James C. Hoe, CMU/ECE/CALCM, ©2023

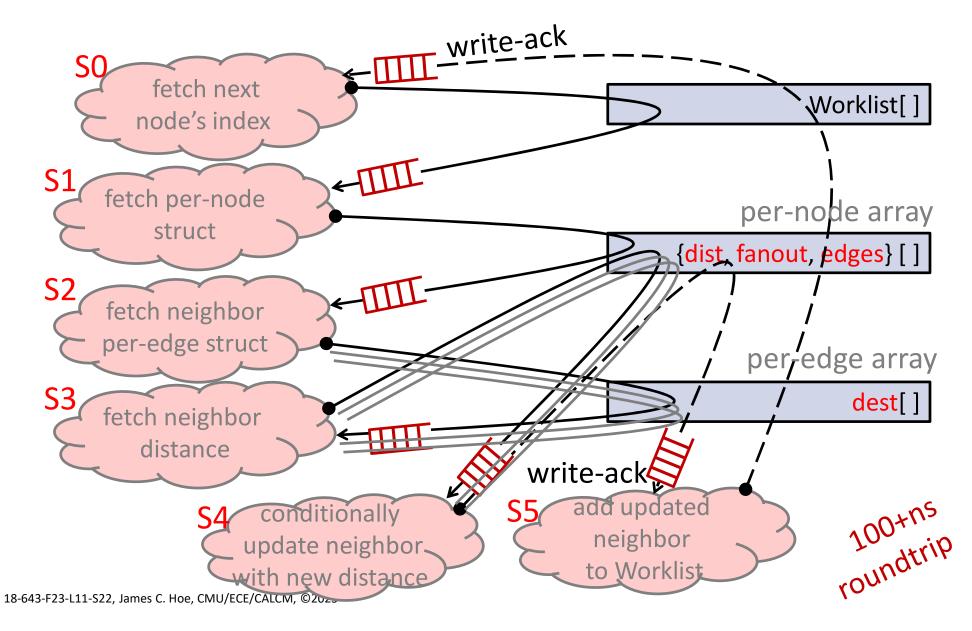

### **Elastic HW Processing Pipeline**

caching

# **BFS Irregular Access Pattern**

- Irregular and graph dependent

- S0 read worklist: spatial locality, non-temporal

- S1 read node array (self): no locality

- S2 read edge array: some spatial locality, non-temporal

- S3 read node array (neighbor): no locality

- S4 write node array (neighbor): temporal with S3

- S5 write worklist: spatial locality, non-temporal

- S3 most problematic of all

- S1 and S3 lack locality but S3 repeated per neighbor

- same number of S2 and S3 but S2 has spatial locality

- BTW, S3 and S4 could have RAW hazard

- BTW, all read/write granularity is multi-word

18-643-F23-L11-S23, James C. Hoe, CMU/ECE/CALCM, ©2023

### How can "Caching" Help?

- Custom cache for only neighbor distance in node array (read in S3 written in S4)

- RAW hazard interlock when nodes in pipeline have same neighbor (stall S3 until conflict-free)

- Coalesces neighbor updates (collect partial writes to multi-word DRAM block)

Organized and operated unlike an ABC cache!!

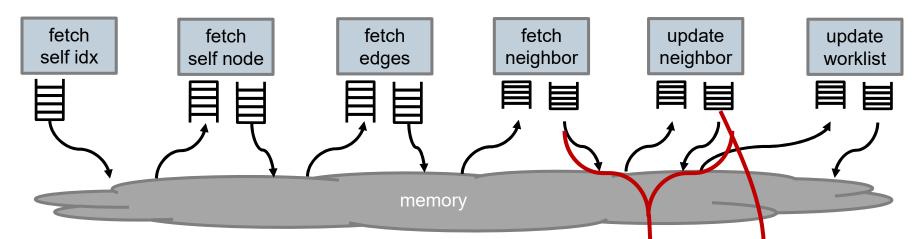

### How can HBM BW help?

- HBM gives you 512GB/sec

- data partitioned 32 ways

- 100s nsec latency

- 32 byte per fetch

- Partition graph data into

32 banks s.t. maximizing

non-conflict concurrent accesses across channel

- Per channel, prefetch many 10s of outstanding read requests to cover latency (Little's Law)

- Re-index nodes in graph s.t. maximizing spatial locality of each 32B fetch

## **Complexity of Sparse Algorithms**

• Graph processing expressible using linear algebra primitives: SpMV, SpMSpV, SpMM, . . .

Simplicity of form belies performance difficulties

- Basic challenges in <u>large data set</u>, <u>low arithmetic</u> <u>intensity</u>, and <u>irregular access pattern</u>

- graph-dependent behavior requires multiple implementations of same primitive depending on:

- size and sparsity

- structured?

- compressed format: CSR, CSC, COO, . . .

Each combination a different optimal design

# **Parting Thoughts**

- When scaling data size and performance, memory design quickly become the PROBLEM

- capacity, bandwidth, latency

- FPGAs specialization is an asset

- balance memory throughput and compute throughput

- have data to the right place at the right time

- alter algorithm to memory constraints

- Designing "memorypath" as important as designing "datapath"