# **18-643 Lecture 7: C-to-HW Synthesis:**

James C. Hoe Department of ECE Carnegie Mellon University

18-643-F23-L07-S1, James C. Hoe, CMU/ECE/CALCM, ©2023

# Housekeeping

- Your goal today: develop a mental model for how to turn "proper" C into "proper" HW, whether by a compiler or by hand

- Notices

- Handout #4: lab 1, due noon, 9/25

- Project status report due each Friday

- Readings (see lecture schedule online)

- for perspective: "The challenges of hardware synthesis from C-like languages," Edwards, 2005.

- for textbook treatment: Ch 7, Reconfigurable

Computing

# C as Model of Computation for HW?

- Common arguments for using C to design HW

- easy algorithm specification

- popularity, popularity, popularity

- A large semantic gap to bridge

- sequential thread of control

- abstract time

- abstract I/O model

- missing structural notions: bit width, ports, modules

- reactive excution

- No problem getting HW from C, but good HW?

All sequential, imperative languages

#### **A Program is a Functional-Level Spec**

```

int fibr(int n) {

if (n==0) return 0;

if (n==1) return 1;

return fibr(n-1)+fibr(n-2);

}

```

#### **A Program is a Functional-Level Spec**

```

int fibm(int n) {

int *array,*ptr; int i;

if (n==0) return 0;

if (n==1) return 1;

array=malloc(sizeof(int)*(n+1));

array[0]=0; array[1]=1;

for(i=2,ptr=array ; i<=n ; i++,ptr++)</pre>

* (ptr+2) =* (ptr+1) +*ptr;

i=array[n];

free(array);

return i;

}

```

#### **A Program is a Functional-Level Spec**

```

int fibi(int n) {

int last=1; int lastlast=0; int temp;

if (n==0) return 0;

if (n==1) return 1;

for(;n>1;n--) {

temp=last+lastlast;

lastlast=last;

last=temp;

}

return temp;

}

```

# **Opening Questions**

- Do they all compute the same "function"?

- Should they all lead to the same hardware?

- Should they all lead to "good" hardware?

- what does recursion look like in hardware?

- what does malloc look like in hardware?

# What is in a C Function?

- What it specifies?

- abstracted data types (e.g., int, floats, doubles)

- operators and step-by-step procedure to compute the return value from input arguments

- a sequential execution

- What it doesn't specify?

- encoding of the variables

- where the state variables are stored

- what types and how many functional units to use

- execution timing, neither in terms of wall-clock time, clock cycles, or instruction count

- what is strictly necessary for correctness

#### Mapping Program to Hardware

- For you to produce "good" structural RTL

- identify suitable "temporal and spatial pattern"

- flesh out concrete datapath (bit/cycle exact)

- develop correct and efficient control sequencing

- C-to-HW (i.e., C-to-RTL) compiler bridges the gap between functionality and implementation

- extract parallelism from a sequential specification

- fill in the details below the functional abstraction

- make good decisions when filling in the details

Keep in mind: what you don't need to specify you also can't control

# A Look at Scheduling and Allocation

18-643-F23-L07-S10, James C. Hoe, CMU/ECE/CALCM, ©2023

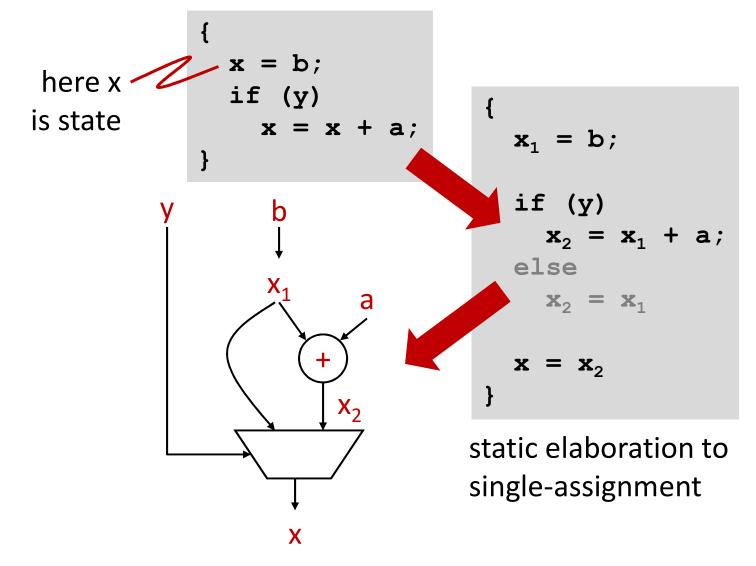

#### **Procedural Block to Data Flow Graph**

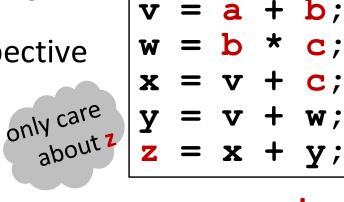

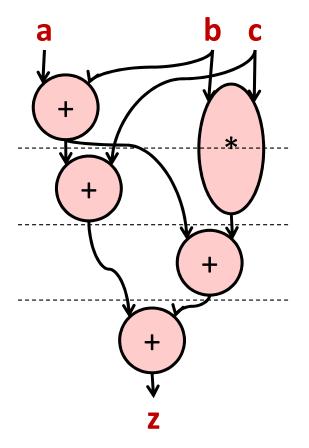

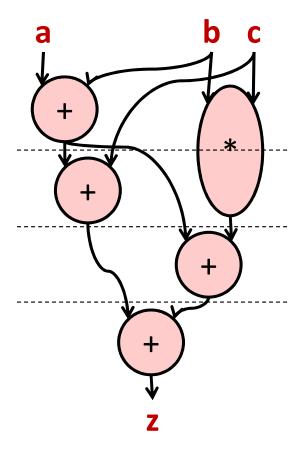

# **Data Flow Graph**

- Captures data dependence irrespective of program order

- nodes=operator

- edge=data flow

- "Work" is total delay if done sequentially

- e.g., if delay(+)=1, delay(\*)=2, work = 6

- "Critical path" is the longest path from input to output

- e.g., critical path delay = 4

- no implementation can complete faster than critical path delay

#### Combinational or sequential??

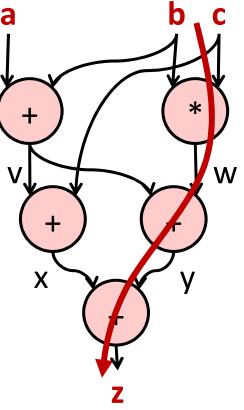

# **Program-Order, Sequential Mapping**

- Need only one of each functional unit type: 1 adder, 1 multiplier

- Delay equal "work": 6

In contrast, if combinational

- 4 adder, 1 multiplier

- delay=4

# Is there a shorter schedule for 1 adder and 1 multiplier?

# **Optimized Sequential Mapping**

- In general,

- given a set of functional units, what is the shortest schedule

- given a schedule, what is the minimum set of functional units

- given a target delay (>= critical path),

find a min-cost schedule

- Very efficient algorithms exist for solving the above

- Harder part is setting the right goal

- minimum delay could be expensive

- minimum resource could be slow

delay=4 using 1 adder and 1 multiplier

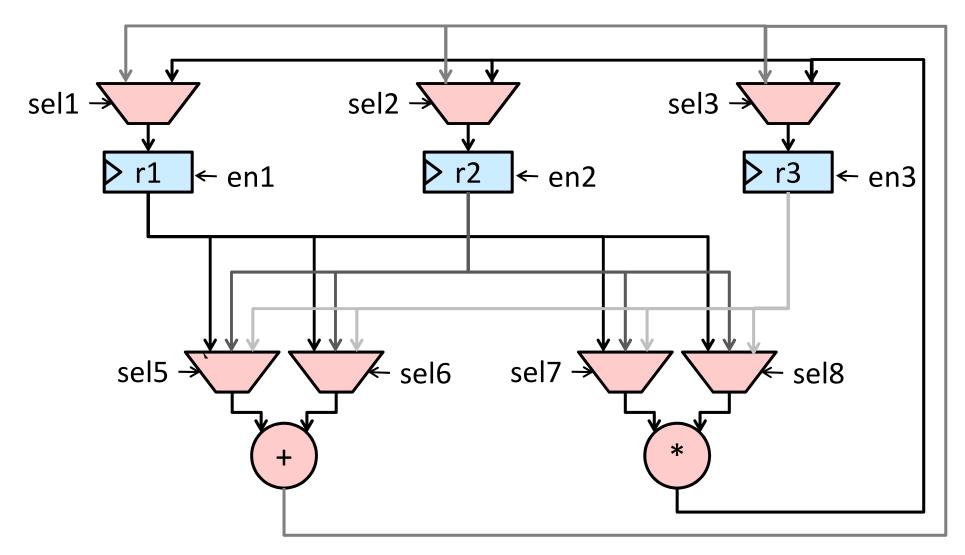

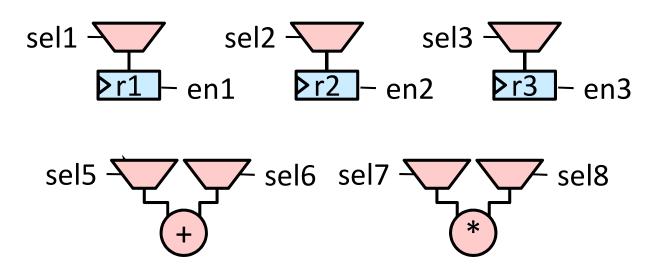

#### **Generating Datapath**

#### How do I know 3 registers are needed?

## **Control FSM**

• Assume initially a in r1; b in r2; c in r3

| r1   |     | r2   |     | r3   |     | add  |      | mult |      |

|------|-----|------|-----|------|-----|------|------|------|------|

| sel1 | en1 | sel2 | en2 | sel3 | en3 | sel5 | sel6 | sel7 | sel8 |

| add  | 1   | -    | 0   | -    | 0   | r1   | r2   | r2   | r3   |

| -    | 0   | add  | 1   | mul  | 1   | r1   | r3   | r2   | r3   |

| add  | 1   | -    | 0   | -    | -   | r1   | r3   | -    | -    |

| add  | 1   | -    | -   | -    | -   | r2   | r1   | -    | -    |

18-643-F23-L07-S16, James C. Hoe, CMU/ECE/CALCM, ©2023

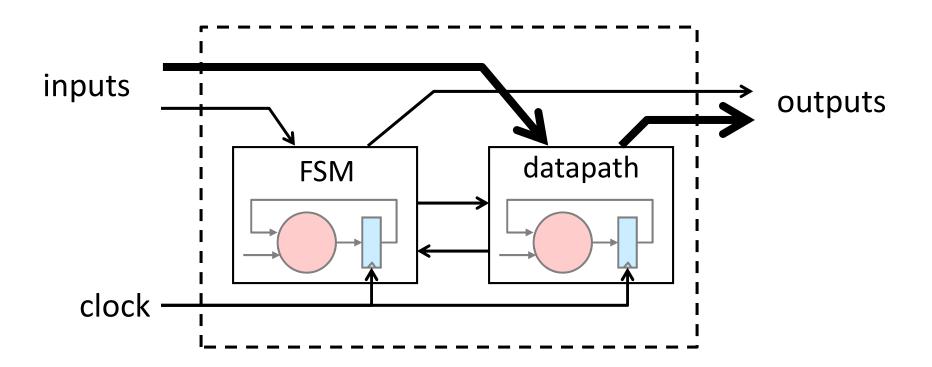

## It should remind you of this

## **Good Hardware Needs Concurrency**

# Where to Find Parallelism in C?

- C-program has a sequential reading

- Scheduling exploits operation-level parallelism in a basic block (~ work/critical-path-delay)

- "ILP" is dependent on scope

- techniques exist to enlarge basic blocks and to increase operation-level parallelisms: loopunrolling, loop pipelining, superblock, trace scheduling, etc.

Many ideas first developed for VLIW compilation

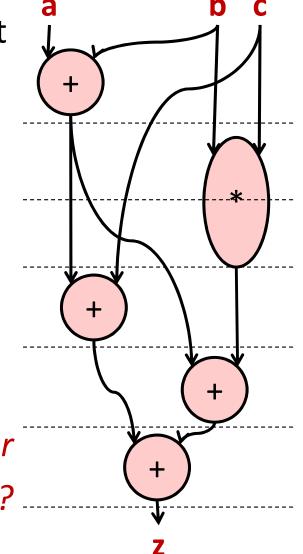

• Structured parallelism can be found across loop iterations, *e.g., data parallel loops*

b[i+1] c[i+1]

## **Loop Unrolling**

for(i=0;i<N;i++)

{

v = a[i]+b[i];

w = b[i]\*c[i];

x = v+c[i];

y = v+w;

z[i] = x+y;

}</pre>

data-parallel iterations

\_ b[i] → c[i] a[i+1] for(i=0;i<N;i+=2)</pre> a[i] v = a[i]+b[i];w = b[i]\*c[i]; $\mathbf{x} = \mathbf{v} + \mathbf{c}[\mathbf{i}];$ y = v + w;z[i] = x+y;v = a[i+1]+b[i+1];w = b[i+1]\*c[i+1];┽  $x_{-} = v' + c[i+1];$  $\mathbf{y} = \mathbf{v} + \mathbf{w}$ ; z[i]  $z[i+1] = x_+y_;$

work=?? critical path=??

z[i+1]

|                                                                                                                         |                                                                                                                                             | CarnegieMellon                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L                                                                                                                       | .oop Pipelining                                                                                                                             | <pre>v = a[0]+b[0];<br/>w = b[0]*c[0];<br/>x = v+c[0];<br/>y = v+w;</pre>                                                                                      |

|                                                                                                                         | <pre>v = a[0]+b[0];<br/>w = b[0]*c[0];<br/>+1</pre>                                                                                         | v = a[1]+b[1];<br>w = b[1]*c[1];                                                                                                                               |

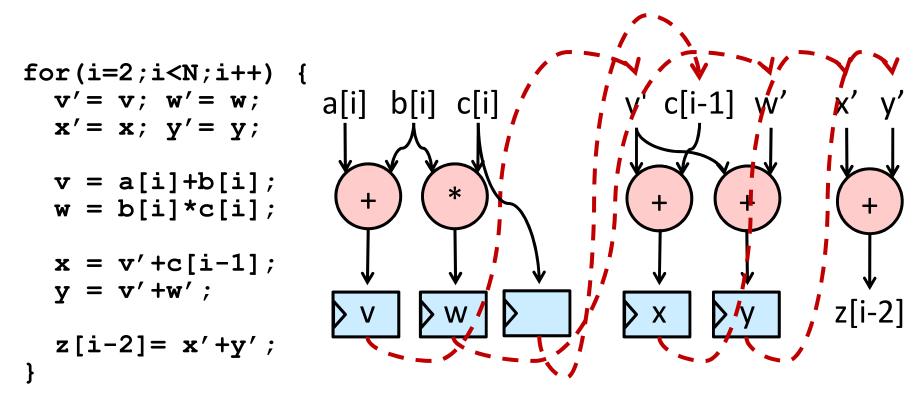

| <pre>for (i=0;i<n;i++) pre="" v="a[i]+b[i];" w="b[i]*c[i];" x="v+c[i];" y="v+w;" z[i]="x+y;" {="" }<=""></n;i++)></pre> | <pre>for (i=1;i<n;i++) v="a[i]+b[i];" v'="v;" w="b[i]*c[i];" w'="w;" x="v+c[i-1];" y="v+w;" z[i-1]="x+y;&lt;/pre" {="" }=""></n;i++)></pre> | <pre>for (i=2;i<n;i++) v="a[i]+b[i];" v'="v;" w="b[i]*c[i];" w'="w;" x="v'+c[i-1];" x'="x;" y="v'+w';&lt;/pre" y'="y;" z[i-2]="x+y;" {="" }=""></n;i++)></pre> |

| 18-643-F23-L07-S21, James C. Hoe, CMU/ECE/CALC                                                                          | CM, ©2023                                                                                                                                   | z[i-1] = x+y;                                                                                                                                                  |

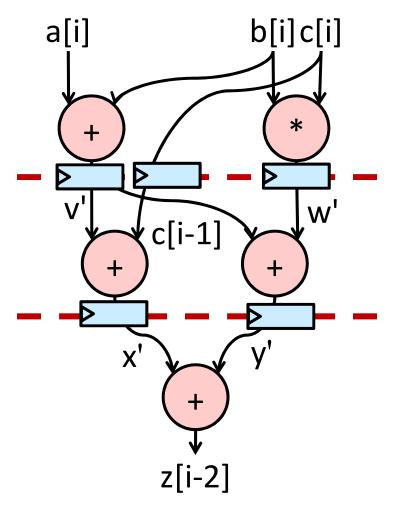

#### **Pipelined Loop**

- In SW, loop pipelining increases producer-consumer distance

- In HW, work on parts of 3 different iterations in same cycle

18-643-F23-L07-S22, James C. Hoe, CMU/ECE/CALCM, ©2023

work=?? critical path=??

## **Pipelined Loop**

- In SW, loop pipelining increases producer-consumer distance

- In HW, work on parts of 3 different iterations in same cycle

This looks more familiar?

#### **How Hard is MMM?**

```

float A[N][N], B[N][N], C[N][N];

for(int i=0; i<N; i++) {</pre>

for(int j=0; j<N; j++) {</pre>

for(in k=0; k<N; k++) {</pre>

C[i][j]=C[i][j]+A[i][k]*B[k][j];

}

}

- \mathsf{T}_{1}, \mathsf{T}_{\infty}, \mathsf{P}_{\text{avg}} = \mathsf{T}_{1/} \mathsf{T}_{\infty}?

- # of memory access?

-T_1 / # of memory access?

```

## What is all not said in the code?

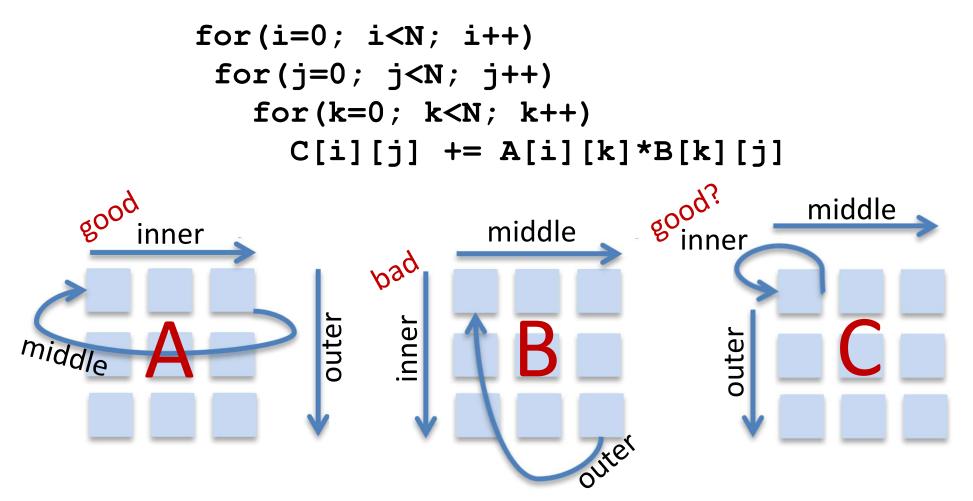

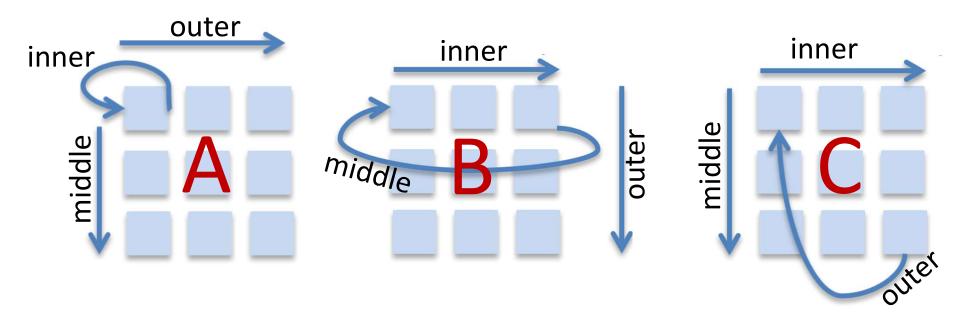

#### A Look at dependency & memory access

(1) Assume row-major layout and large 2-power N (2) 64-Byte DRAM interface and 8-KByte row buffer

18-643-F23-L07-S26, James C. Hoe, CMU/ECE/CALCM, ©2023

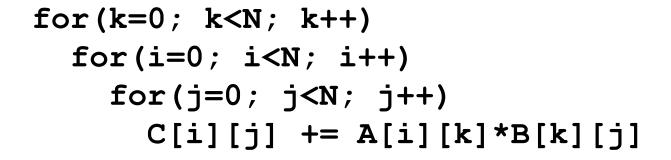

#### **Loop Reordering**

#### Data-parallel over the i and j loops

# **Loop Reordering Affects Parallelism**

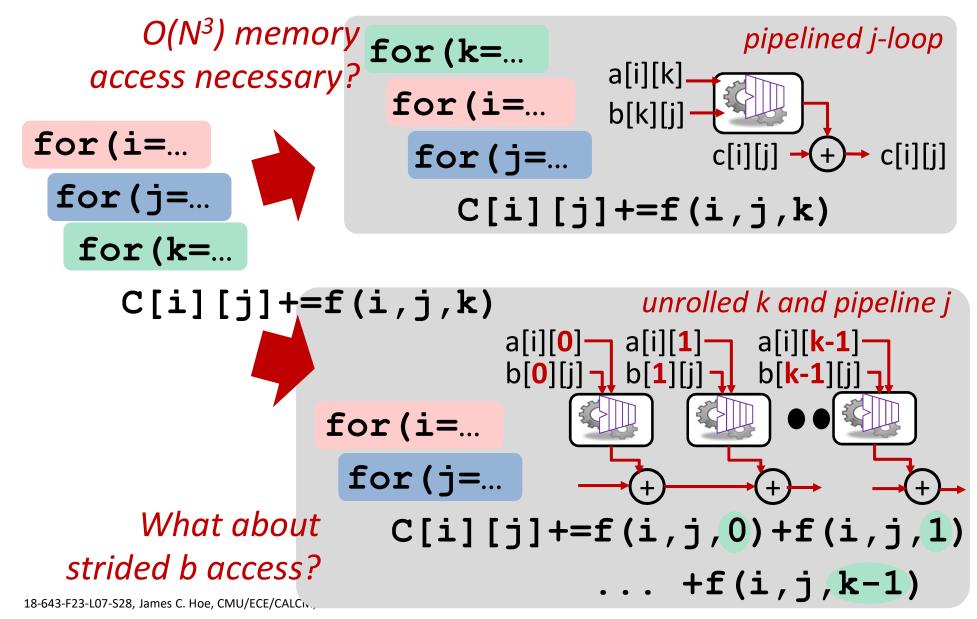

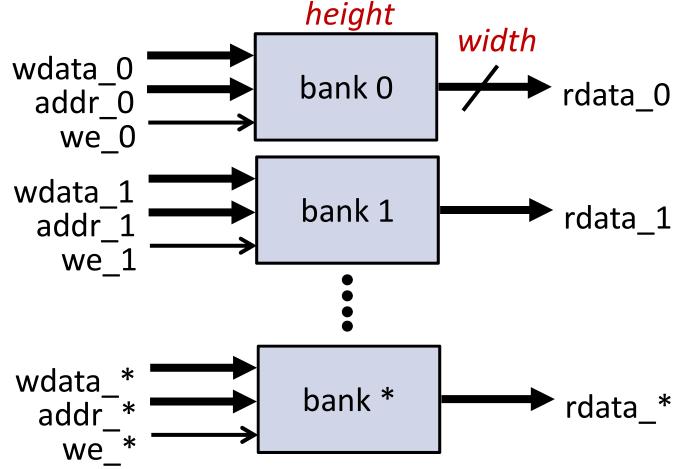

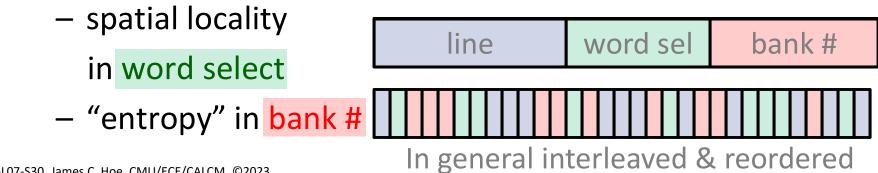

# **Memory not Monolithic Abstraction**

Control memory organization to match access pattern

word sel

ľg<sub>2</sub>W

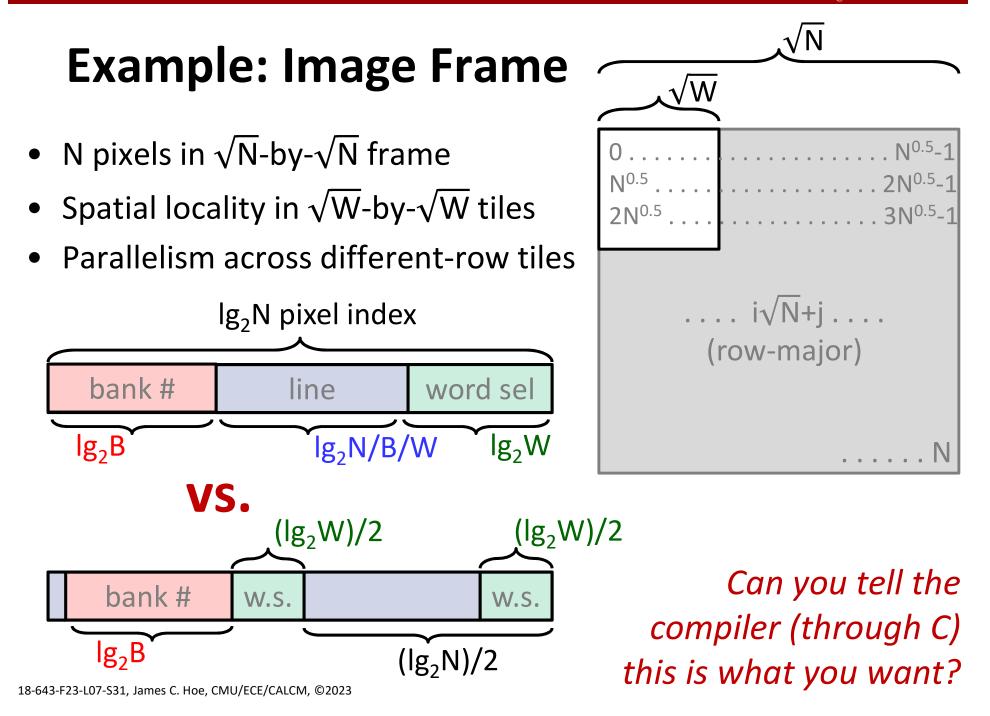

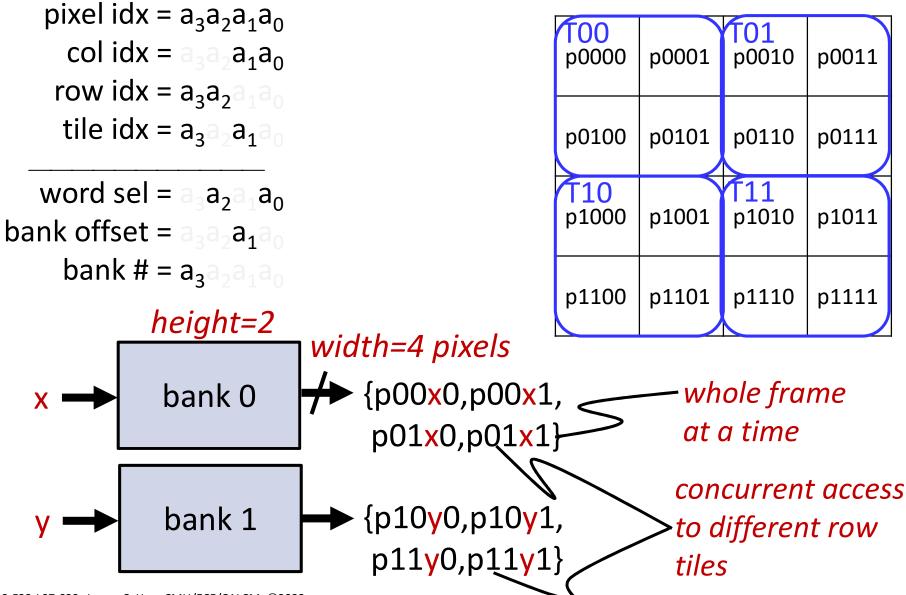

# **Control over Data Layout**

• An array of N words; index is  $lg_2N$  bits

lg<sub>2</sub>N array index (sequential)

line

lg<sub>2</sub>N/B/W

- N-word total storage

Ig<sub>2</sub>B

- divided into B banks; bank number is lg<sub>2</sub>B bits

- each bank is W-word wide; word-select is lg<sub>2</sub>W bits

bank #

- line index within bank is  $lg_2(N/B/W)$  bits

- Assign bank #, word select and index to maximize

# A Small Concrete Example: N=16, W=4

18-643-F23-L07-S32, James C. Hoe, CMU/ECE/CALCM, ©2023

# **Parting Thoughts**

- C-to-HW compiler fills in details between algorithm and implementation

- No magic—good HW only if it is in the program

- not every computation is right for HW so not every C-program is right for HW

- even for right ones, how the C is written matters

- C-to-HW technology is very real today

- work very well on some domain or applications

- has blindspots; need human-in-the-loop pragmas

Useful in different ways to an expert HW designer vs.

a so-so HW designer vs. a SW programmer