## 18-447 Lecture 8: Data Hazard and Resolution

James C. Hoe

Department of ECE

Carnegie Mellon University

#### Housekeeping

- Your goal today

- detect and resolve data hazards in in-order instruction pipelines

- control dependence next time

- Notices

- HW 2, due Mon 2/19

- Lab 2, status check wk6, due wk7 (Handout #7)

- Readings

- P&H Ch 4

### **Instruction Pipeline Reality**

- Not identical tasks

- coalescing instruction types into one "multifunction" pipe

- external fragmentation (some idle stages)

- Not uniform suboperations

- group or sub-divide steps into stages to minimize variance

- internal fragmentation (some too-fast stages )

- Not independent tasks

- dependency detection and resolution

- next lecture(s)

#### **Data Dependence**

Data dependence

$$x3 \leftarrow x1 \text{ op } x2$$

$x5 \leftarrow x3 \text{ op } x4$

$x3 \leftarrow x1$  op x2 Read-after-Write (RAW)

Anti-dependence

$$x3 \leftarrow x1$$

op  $x2$

$x1 \leftarrow x4$  op  $x5$

$x3 \leftarrow x1$  op x2 Write-after-Read (WAR)

Output-dependence

$$x3 \leftarrow x1 \text{ op } x2$$

$x3 \leftarrow x6 \text{ op } x7$

$\Rightarrow$  x3  $\leftarrow$  x1 op x2 Write-after-Write (WAW)

Don't forget memory instructions

alse dependence

#### Dependence vs Hazard: e.g. RAW

Dependence is property of program; hazards specific to microarchitecture

#### Register Data Hazard Analysis

|     | R/I-Type | LW       | SW      | Bxx     | Jal      | Jalr     |

|-----|----------|----------|---------|---------|----------|----------|

| IF  |          |          |         |         |          |          |

| ID  | read RF  | read RF  | read RF | read RF |          | read RF  |

| EX  |          |          |         |         |          |          |

| MEM |          |          |         |         |          |          |

| WB  | write RF | write RF |         |         | write RF | write RF |

- For a given pipeline, when is there a register data hazard between 2 dependent instructions?

- dependence type: RAW, WAR, WAW?

- instruction types involved?

- distance between the two instructions?

#### Hazard in In-order Pipeline

younger stage X **RF Write** j: \_←r<sub>k</sub> RF Read j: r<sub>k</sub>←\_\_ **RF Write** j: r<sub>k</sub>←\_\_ stage Y **RF Write**  $i: \_\leftarrow r_k$ RF Read i: r<sub>k</sub>←\_\_ **RF Write** i: r<sub>k</sub>←\_\_ older **WAR Hazard RAW Hazard WAW Hazard**  $dist_{dependence}(i,j) \leq dist_{hazard}(X,Y) \Rightarrow Hazard!!$  $dist_{dependence}(i,j) > dist_{hazard}(X,Y) \Rightarrow Safe$

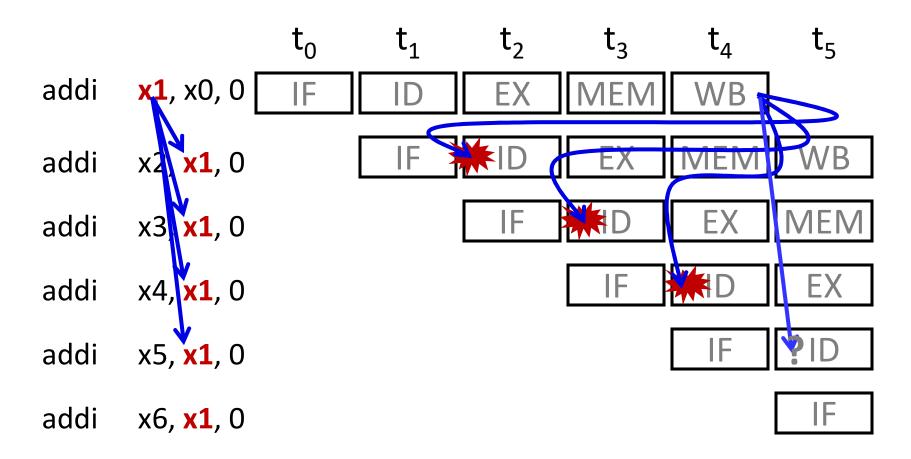

#### **RAW Hazard Analysis Example**

|     | R/I-Type | LW       | SW      | Bxx     | Jal      | Jalr     |

|-----|----------|----------|---------|---------|----------|----------|

| IF  |          |          |         |         |          |          |

| ID  | read RF  | read RF  | read RF | read RF |          | read RF  |

| EX  |          |          |         |         |          |          |

| MEM |          |          |         |         |          |          |

| WB  | write RF | write RF |         |         | write RF | write RF |

- Older I<sub>A</sub> and younger I<sub>B</sub> have RAW hazard iff

- I<sub>B</sub> (R/I, LW, SW, Bxx or JALR) reads a register written

by I<sub>A</sub> (R/I, LW, or JAL/R)

- $\operatorname{dist}(I_A, I_B) \leq \operatorname{dist}(ID, WB) = 3$

What about WAW and WAR hazard? What about memory data hazard?

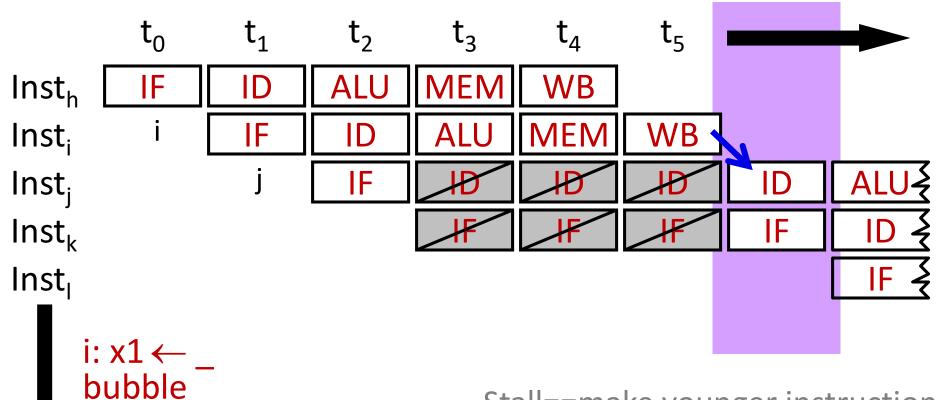

# Pipeline Stall: universal hazard resolution

bubble bubble j: \_ ← x1 dist(i,j)=4 Stall==make younger instruction

wait until hazard passes

1. stop all up-stream stages

2. drain all down-stream stages

## **Pipeline Stall**

|     | t <sub>1</sub> | t <sub>2</sub> | t <sub>3</sub> | t <sub>4</sub> | t <sub>5</sub> | t <sub>6</sub> | t <sub>7</sub> | t <sub>8</sub> | t <sub>9</sub> | t <sub>10</sub> | t <sub>11</sub> |

|-----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|

| IF  | -              | j              | k              | k              | k              | k              |                |                |                |                 |                 |

| ID  | h              |                | j              | j              | j              | j              | k              | I              |                |                 |                 |

| EX  |                | h              | i              | bub            | bub            | bub            | j              | k              | ı              |                 |                 |

| MEM |                |                | h              | i              | bub            | bub            | bub            | j              | k              |                 |                 |

| WB  |                |                |                | h              | i              | bub            | bub            | bub            | j              | k               | I               |

i:

$$x1 \leftarrow \underline{\phantom{a}}$$

i:  $\leftarrow x1$

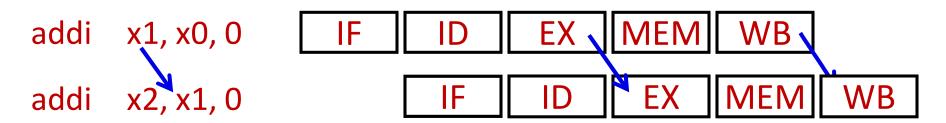

### Pop Quiz: What happens in this case?

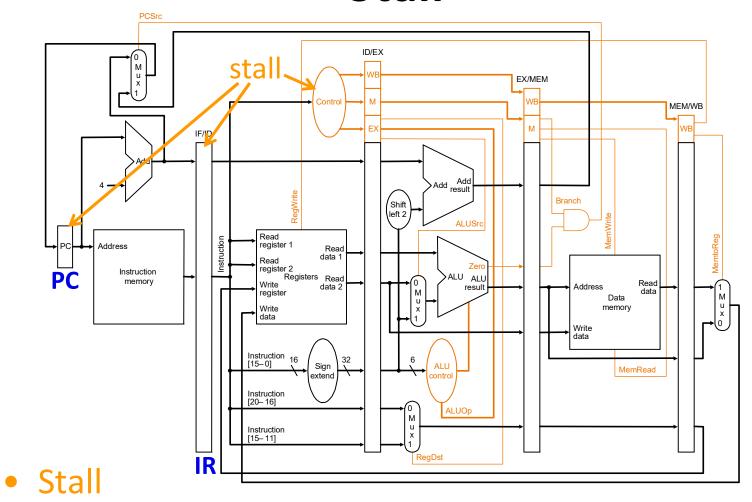

#### Stall

- disable PC and IR latching

- set RegWrite<sub>ID</sub>=0 and MemWrite<sub>ID</sub>=0

#### When to Stall

- Older I<sub>A</sub> and younger I<sub>B</sub> have RAW hazard iff

- I<sub>B</sub> (R/I, LW, SW, Bxx or JALR) reads a register written by I<sub>A</sub> (R/I, LW, or JAL/R)

- $-\operatorname{dist}(I_{\Delta},I_{B}) \leq \operatorname{dist}(ID,WB) = 3$

Above is about existence of hazard

- Operationally, to detect hazard in time to prevent:

- before I<sub>B</sub> in ID reads a register, I<sub>B</sub> needs to check if any I<sub>A</sub> in EX, MEM or WB is going to update it

(if so, value in RF is "stale")

#### **Stall Condition**

- Helper function

- useRs1(I) returns true if I uses rs1

- Stall IF and ID when

```

(rs1_{ID}==rd_{EX}) && RegWrite<sub>EX</sub> && useRs1(IR<sub>ID</sub>) && rs1<sub>ID</sub>!=x0 or (rs1_{ID}==rd_{MEM}) && RegWrite<sub>MEM</sub> && useRs1(IR<sub>ID</sub>) && rs1<sub>ID</sub>!=x0 or (rs1_{ID}==rd_{WB}) && RegWrite<sub>WB</sub> && useRs1(IR<sub>ID</sub>) && rs1<sub>ID</sub>!=x0 or (rs2_{ID}==rd_{EX}) && RegWrite<sub>EX</sub> && useRs2(IR<sub>ID</sub>) && rs2<sub>ID</sub>!=x0 or (rs2_{ID}==rd_{MEM}) && RegWrite<sub>MEM</sub> && useRs2(IR<sub>ID</sub>) && rs2<sub>ID</sub>!=x0 or (rs2_{ID}==rd_{WB}) && RegWrite<sub>MEM</sub> && useRs2(IR<sub>ID</sub>) && rs2<sub>ID</sub>!=x0 or (rs2_{ID}==rd_{WB}) && RegWrite<sub>WB</sub> && useRs2(IR<sub>ID</sub>) && rs2<sub>ID</sub>!=x0

```

It is crucial that EX, MEM and WB continue to advance during stall

#### Impact of Stall on Performance

- Each stall cycle corresponds to 1 lost ALU cycle

- A program with N instructions and S stall cycles:

- S depends on

- frequency of hazard-causing dependencies

- distance between hazard-causing instruction pairs

- distance between hazard-causing dependencies

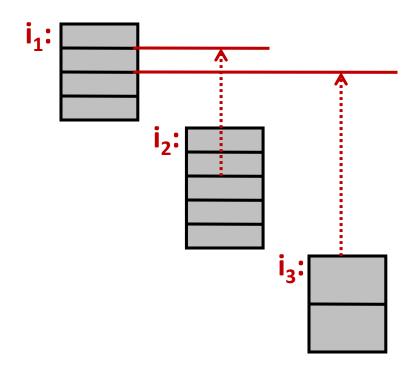

(suppose i<sub>1</sub>,i<sub>2</sub> and i<sub>3</sub> all depend on i<sub>0</sub>, once i<sub>1</sub>'s hazard is resolved by stalling, i<sub>2</sub> and i<sub>3</sub> do not stall)

#### Sample Assembly [P&H]

for  $(j=i-1; j>=0 \&\& v[j] > v[j+1]; j-=1) { ..... }$

```

addi $s1, $s0, -1

3 stalls

for2tst:

slti $t0, $s1, 0

3 stalls

$t0, $zero, exit2

bne

$t1, $s1, 2

sll

3 stalls

$t2, $a0, $t1

add

3 stalls

$t3, 0($t2)

lw

$t4, 4($t2)

lw

3 stalls

$t0, $t4, $t3

slt

3 stalls

beq

$t0, $zero, exit2

$s1, $s1, -1

addi

for2tst

```

exit2:

#### Data Forwarding (or Register Bypassing)

- What does "ADD r<sub>x</sub> r<sub>y</sub> r<sub>z</sub>" mean? Get inputs from RF[r<sub>y</sub>] and RF[r<sub>z</sub>] and put result in RF[r<sub>x</sub>]?

- But, RF is just a part of an abstraction

- a way to connect dataflow between instructions

"operands to ADD are resulting <u>values</u> of the last instructions to assign to RF[r<sub>v</sub>] and RF[r<sub>z</sub>]"

- RF doesn't have to exist/behave as a <u>literal object!!!</u>

- If only dataflow matters, don't wait for WB . . .

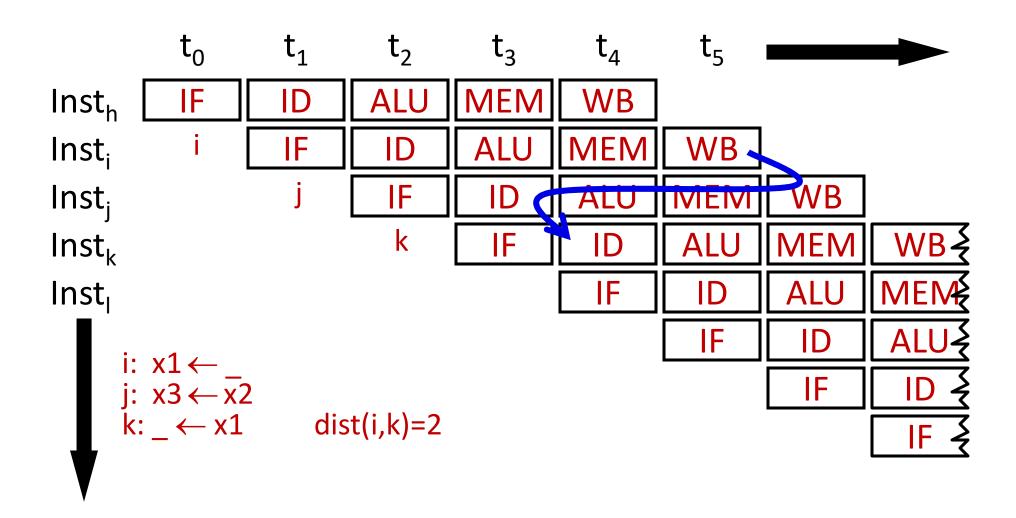

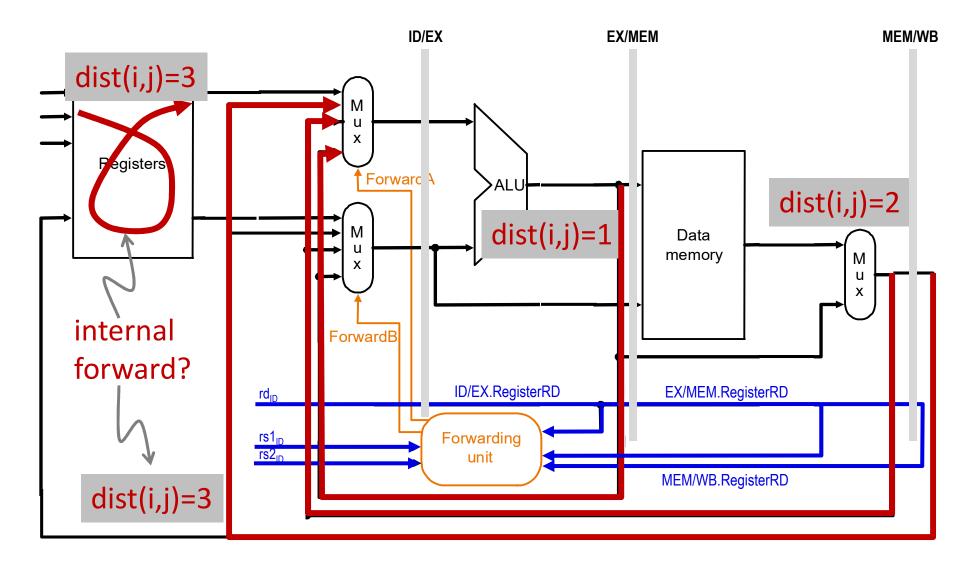

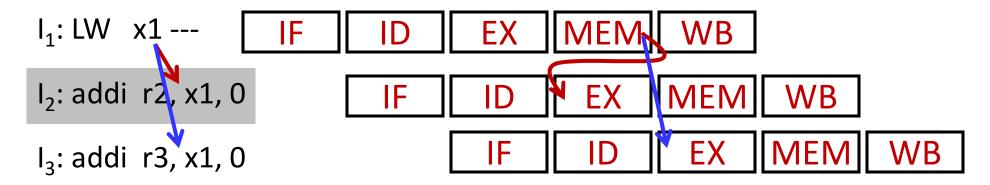

#### Resolving RAW Hazard by Forwarding

- Older I<sub>A</sub> and younger I<sub>B</sub> have RAW hazard iff

- I<sub>B</sub> (R/I, LW, SW, Bxx or JALR) reads a register written by I<sub>A</sub> (R/I, LW, or JAL/R)

- $-\operatorname{dist}(I_A, I_B) \leq \operatorname{dist}(ID, WB) = 3$

- To detect hazard in time to prevent, before I<sub>B</sub> in ID reads a register, I<sub>B</sub> needs to check if any I<sub>A</sub> in EX, MEM or WB is going to update it

- Before: I<sub>B</sub> need to stall for I<sub>A</sub> to <u>update RF</u>

- Now: I<sub>B</sub> need to stall for I<sub>A</sub> to <u>produce result</u>

- retrieve | result from datapath when ready

- retrieve youngest if multiple "apparent" hazards

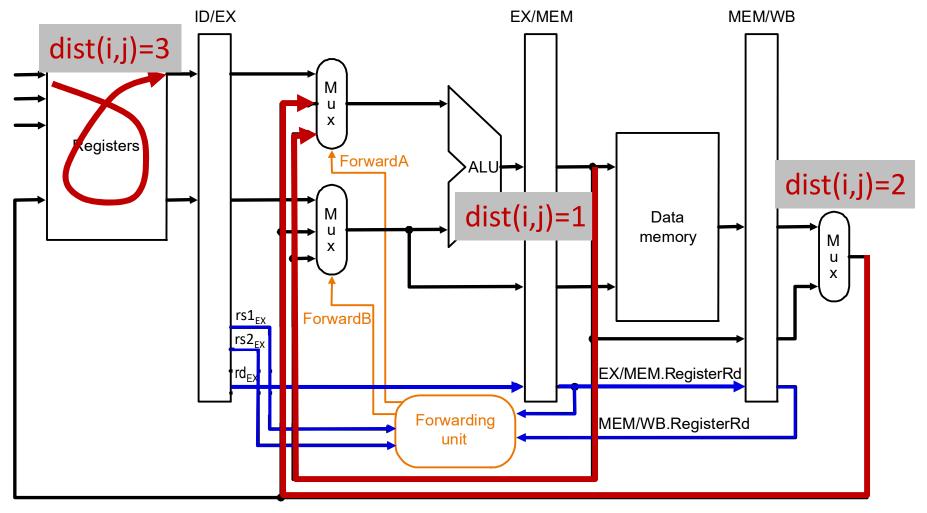

### Forwarding Paths (v1)

#### Forwarding Paths (v2)

better if EX is the fastest stage

#### Forwarding Logic (for v1)

```

if (rs1_{ID}!=0) && (rs1_{ID}==rd_{EX}) && RegWrite<sub>EX</sub> then forward writeback value from EX  // dist=1 else if (rs1_{ID}!=0) && (rs1_{ID}==rd_{MEM}) && RegWrite<sub>MEM</sub> then forward writeback value from MEM  // dist=2 else if (rs1_{ID}!=0) && (rs1_{ID}==rd_{WB}) && RegWrite<sub>WB</sub> then forward writeback value from WB  // dist=3 else  // dist > 3

```

Must prioritize young-to-old Why doesn't *useRs1*() appear? Isn't it bad to forward from LW in EX?

#### Data Hazard Analysis (with Forwarding)

|     | R/I-Type       | LW      | SW    | Bxx | Jal       | Jalr           |

|-----|----------------|---------|-------|-----|-----------|----------------|

| IF  |                |         |       |     |           |                |

| ID  |                |         |       |     | (produce) | (produce)      |

| EX  | use<br>produce | use     | use   | use | produce   | use<br>produce |

| MEM |                | produce | (use) |     |           |                |

| WB  |                |         |       |     |           |                |

Even with forwarding, RAW dependence on immediate preceding LW results in hazard

$$Stall = \{ [rs1_{|D} = rd_{EX} \&\& useRs1(IR_{|D}) \&\& rs1_{|D}! = 0 ] \mid | i.e., op_{EX} = LX$$

$$[rs2_{|D} = rd_{EX} \&\& useRs2(IR_{|D})] \&\& rs2_{|D}! = 0 ] \} \&\& MemRead_{EX}$$

#### Historical: MIPS Load "Delay Slot"

- R2000 defined LW with arch. latency of <u>1 inst</u>

- invalid for I<sub>2</sub> (in LW's delay slot) to ask for LW's result

- any dependence on LW at least distance 2

- Delay slot vs dynamic stalling

- fill with an independent instruction (no difference)

- if not, fill with a NOP (no difference)

- Can't lose on 5-stage . . . good idea?

#### Sample Assembly [P&H]

```

for (j=i-1; j>=0 \&\& v[j] > v[j+1]; j-=1) { ..... }

```

```

addi $s1, $s0, -1

slti $t0, $s1, 0

for2tst:

bne $t0, $zero, exit2

sll $t1, $s1, 2

add $t2, $a0, $t1

$t3, 0($t2)

lw

stall or

$t4, 4($t2)

lw

1 nop (MIPS)

$t0, $t4, $t3

slt

$t0, $zero, exit2

beq

addi $s1, $s1, -1

for2tst

```

exit2:

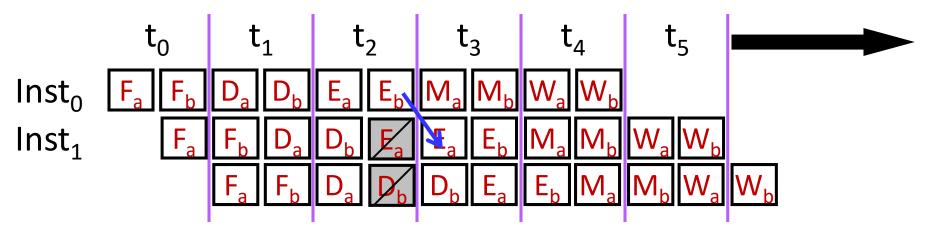

#### Why not very deep pipelines?

- With only 5 stages, still plenty of combinational logic between registers

- "Superpipelining" ⇒ increase pipelining such that even intrinsic operations (e.g. ALU, RF access, memory access) require multiple stages

- What's the problem? Inst<sub>0</sub>: addi  $x_1$ ,  $x_0$ , 0

Inst<sub>1</sub>: addi x2,  $\overline{x}$ 1, 0

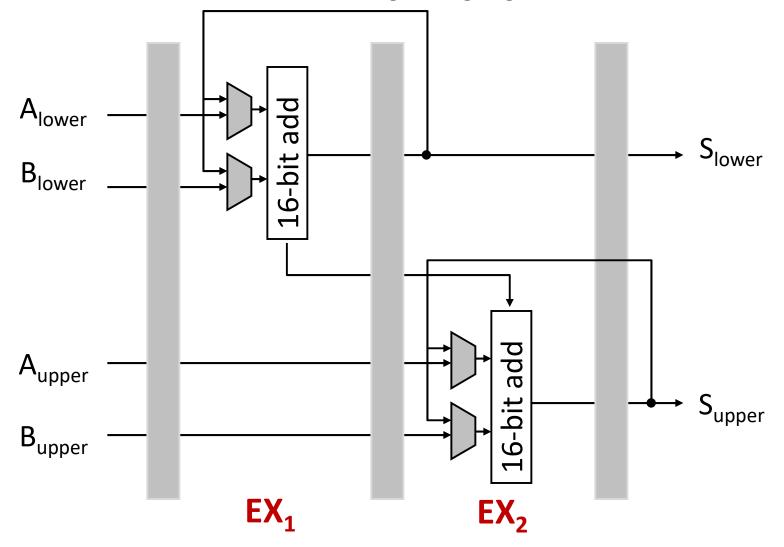

#### Aside: Intel P4's Superpipelined Adder

32-bit addition pipelined over 2 stages, BW=1/latency<sub>16-bit-add</sub>

No stall between back-to-back dependencies

#### **Terminology**

- Dependency

- property of program

- ordering requirement between instructions

- Pipeline Hazard:

- property of uarch when interacting with program

- (potential) violation of dependencies in program

- Hazard Resolution:

- static ⇒ schedule instructions at compile time to avoid hazards

- dynamic ⇒ detect hazard and adjust pipeline

operation Stall, Flush or Forward

## Dependencies and Pipelining (architecture vs. microarchitecture)

Sequential and atomic instruction semantics

Defines what is correct; doesn't say do it this way

True dependence between two instructions may only require ordering of certain sub-operations