|                |                                                                                                                                                                                                                                | CMU 18-447<br>S'09 L22-1<br>© 2009<br>J. C. Hoe |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Su             | 18-447 Lecture 22:<br>Virtual Memory:<br>rvey of Modern Systems                                                                                                                                                                |                                                 |

| Jui            | •                                                                                                                                                                                                                              |                                                 |

|                | James C. Hoe<br>Dept of ECE, CMU<br>April 15, 2009                                                                                                                                                                             |                                                 |

| Announcements: | Spring Carnival!!!<br>Final Thursday, May 7 5:30-8:30p.m Room TBA<br>Two Guest Lectures next Mon and Wed (not on final)<br>L23: multicore cache-coherence by Nikos Hardave<br>L24: advanced multicore design by Prof. Onur Mut |                                                 |

| Handouts:      | Assigned Reading "Virtual memory in contemporary<br>microprocessors." B. L Jacob and T. N. Mudge. IEEE<br>July/August 1998                                                                                                     | Micro,                                          |

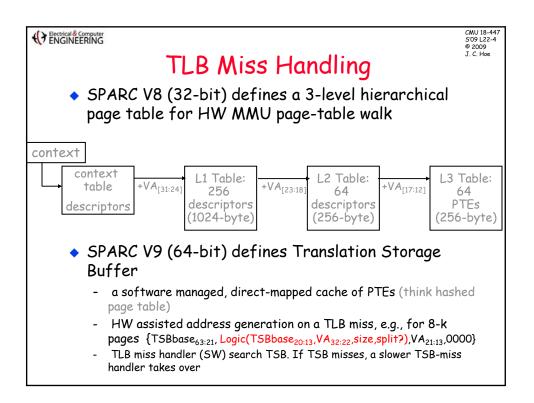

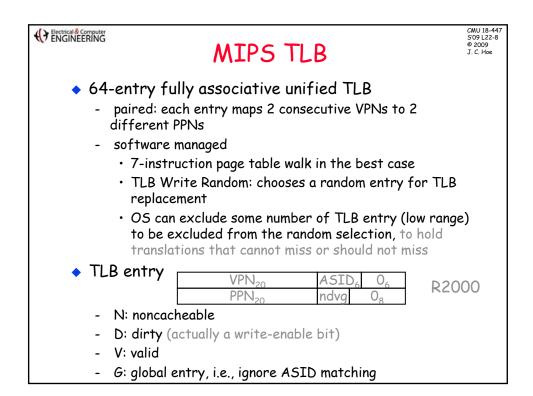

| Engineering UserTL | LB Miss Handling             |  |  |

|--------------------|------------------------------|--|--|

| mfc0 k0,tlbcxt     | # move the contents of TLB   |  |  |

|                    | # context register into k0   |  |  |

| mfc0 k1,epc        | # move PC of faulting load   |  |  |

|                    | # instruction into k1        |  |  |

| lw k0,0(k0)        | # load thru address that was |  |  |

|                    | # inTLB context register     |  |  |

| mtc0 k0,entry_lo   | # move the loaded value      |  |  |

|                    | # into the EntryLo register  |  |  |

| tlbwr              | # write entry into the TLB   |  |  |

|                    | # at a random slot number    |  |  |

| j <b>k</b> 1       | # jump to PC of faulting     |  |  |

| -                  | # load instruction to retry  |  |  |

| rfe                | # RESTORE FROM               |  |  |

|                    | # EXCEPTION                  |  |  |

Electrical & Computer

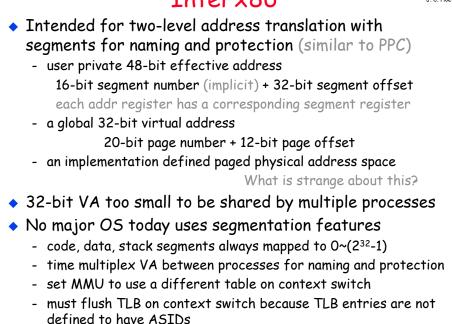

## Intel x86

CMU 18-447 5'09 L22-13 © 2009 J. C. Hoe