ENGINEERING

CMU 18-100 S'15 L24-1 © 2015

# 18-100 Lecture 24: Sequential Logic Design

James C. Hoe Dept of ECE, CMU April 21, 2015

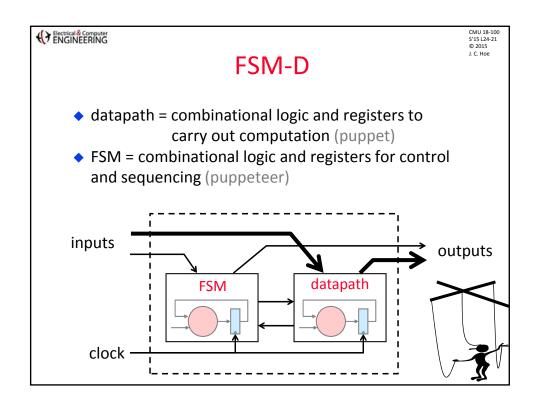

Today's Goal: Start thinking about stateful stuff

Announcements: Read Rizzoni 12.6

HW 9 due

Exam 3 on April 30

Final Exam, Fri., May 8, 8:30~11:30, GHC 4401 *Conflicts?*

Handouts: HW 10 (on Blackboard)

HW 9 solutions (on Blackboard later on)

Lab 12 (on Blackboard later on)

Electrical & Computer ENGINEERING

CMU 18-100 S'15 L24-3 © 2015 J. C. Hoe

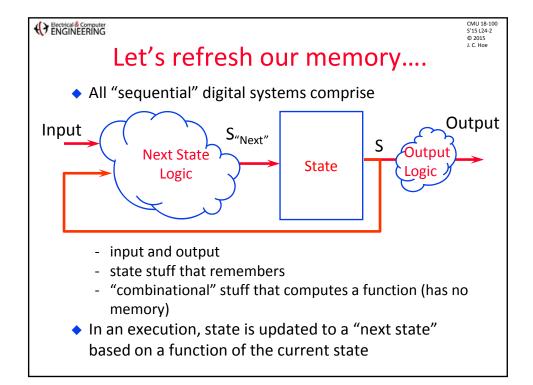

### Memory 101

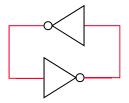

Pure combinational logic always go from a current input to a current output without any looping back

There is no notion of time, past or future

- To remember, must somehow incorporate previous values

- You mean like this?

Does it remember? What does it remember? (It is easier to see if you associate a small propagation delay with wires and gates)

Electrical & Computer ENGINEERING

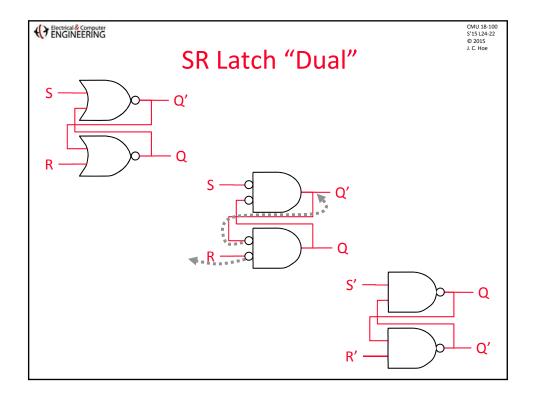

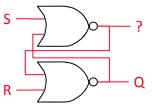

#### A Better Try: the SR Latch

- Keep in mind that

- X+0=X ⇒ (X+0)'=X'

- X+1=1  $\Rightarrow$  (X+1)'=0

- Hint: S stands for "set"; R for "reset"

- Consider

- S=0 and R=0: the NORs simply act like inverters in the feedback loop; Q is remembered

- S=1 and R=0: the top NOR's output is forced to 0; the bottom NOR inverts the feedback; Q is set to 1

- S=0 and R=1: the bottom NOR's output is forced to 0;

the top NOR inverts the feedback; Q is reset to 0

- S=1 and R=1: Just don't do it

After asserting S or R, the resulting Q is remembered when S and R are both deasserted again

If you feel brave try finding the "dual"

Electrical & Computer ENGINEERING

CMU 18-10 S'15 L24-9 © 2015

## Let's play with this a bit first

Electrical & Computer ENGINEERING

CMU 18-100 S'15 L24-10 © 2015 L.C. Hoe

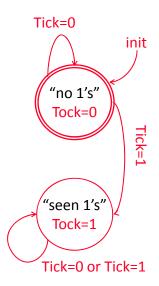

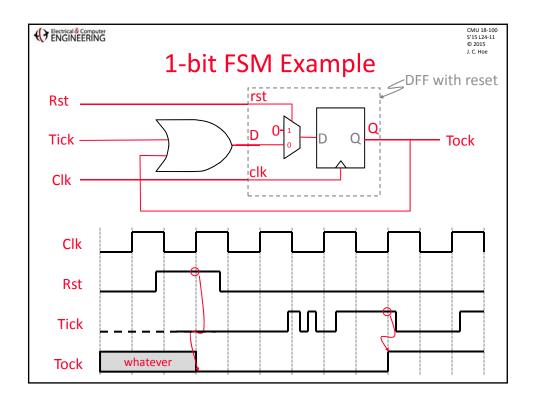

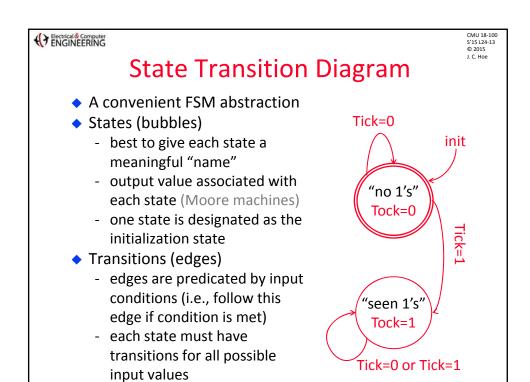

# 1-bit FSM Example

- ◆ Implied input: Reset, Clk

- Input

- 1-bit signal "Tick"

- you can vary its value over time, anytime you like, but only the values at the rising clock edges matter

- Output

- 1-bit signal "Tock"

- Tock should be 0 after reset

- Tock should become 1 and stay 1 after Tick has been 1 (as sampled on a rising clock edge)

- What are the two states?

- Tick has never been 1 since reset

- not the above

Electrical & Computer ENGINEERING

CMU 18-10 S'15 L24-15 © 2015 J. C. Hoe

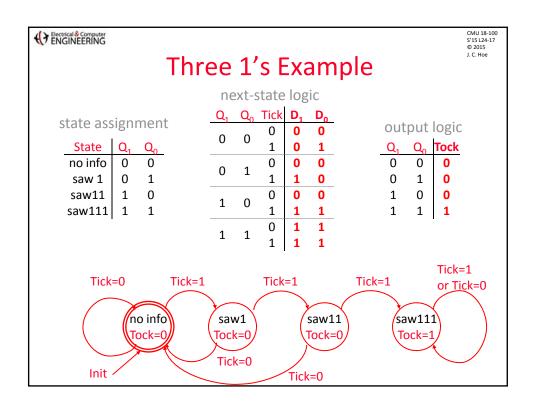

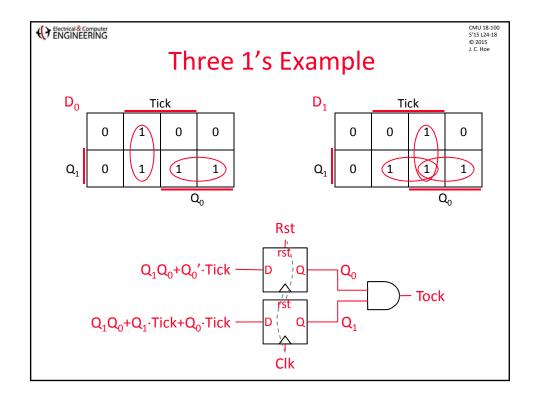

### Realizing an FSM

- State assignment

- require at least n= Ig<sub>2</sub>N bits Q<sub>n-1</sub>,...,Q<sub>0</sub> to encode an FSM with N states (each bit is a D flip-flop)

- assign each state to an unique encoding

- choice of encoding can affect the size of combinational next-state logic (don't worry about it in 18-100)

- Next-state logic

- computes the next state value D<sub>n-1</sub>,...,D<sub>0</sub> as a function of the FSM input and current state Q<sub>n-1</sub>,...,Q<sub>0</sub>

- "Moore-style" Output logic

- computes the FSM output as a function of current state Q<sub>n-1</sub>,...,Q<sub>0</sub>

# ⊕ ENGINEERING Tick-Tock Example

- 2 states, hence a 1-bit FSM

- "no 1's" when  $Q_0=0$

- "seen 1's" when  $Q_0=1$

- Next-state logic truth table

| $Q_0$ | Tick | $D_0$ |

|-------|------|-------|

| 0     | 0    | 0     |

| 0     | 1    | 1     |

| 1     | 0    | 1     |

| 1     | 1    | 1     |

Output logic truth table