CMU 18-100 S'15 L23-1 © 2015 J. C. Hoe

# 18-100 Lecture 23: Combinational Datapath

James C. Hoe Dept of ECE, CMU April 14, 2015

Today's Goal: Structured combinational digital circuits

Announcements: Read Rizzoni 12.4 and 12.5

Read Rizzoni 12.6 for next time

Exam 3 on April 30

Final Exam, Fri., May 8, 8:30~11:30, GHC 4401 Conflicts?

HW9 due Tuesday 4/21

No class on Thursday; no lab this week

Handouts:

Electrical & Computer ENGINEERING

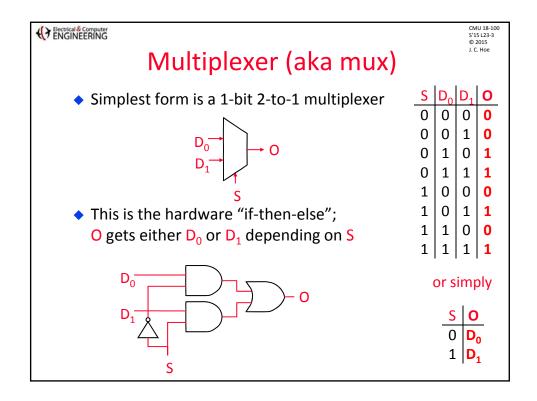

CMU 18-100 S'15 L23-2 © 2015 L.C. Hoe

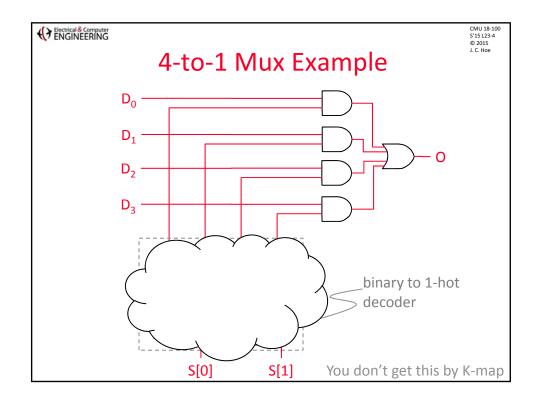

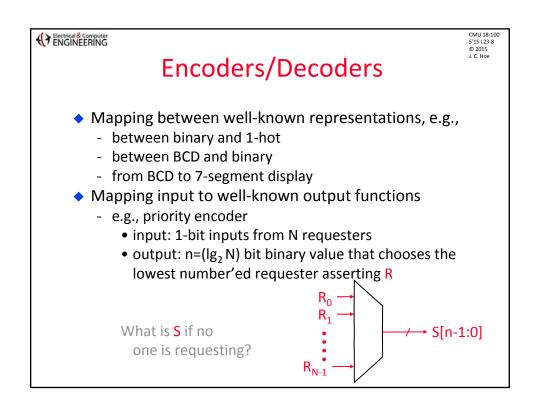

### **Combinational Logic Blocks**

- With K-map, you can build any combinational functions you want, but not everything should be build from K-map

- minimum SOP/POS ≠ globally "optimum"

- some functions have special structures to be taken advantage of

- some functions are so frequently used they have become conventions

- Major examples

- multiplexer

- demultiplexer

- encoder/decoder of various types

- arithmetic: adder, multiplier, etc

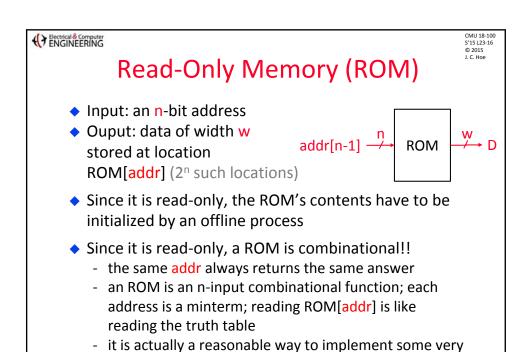

- read-only memory

Electrical & Computer ENGINEERING

CMU 18-100 S'15 L23-5 © 2015

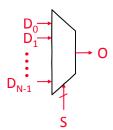

## **Multiplexer Generalizations**

- N-to-1 selection using

- S of  $\lg_2N$  bits as a binary number or

- S of N bits as a "one-hot" bit mask (this is called a decoded mux)

◆ D<sub>x</sub> and O could be a bundle of wires of width w (aka a bus), e.g., to carry a binary number

$$D_0[w-1:0] \xrightarrow{W} W O[w-1:0]$$

$$D_1[w-1:0] \xrightarrow{W} S$$

Electrical & Computer ENGINEERING

CMU 18-100 S'15 L23-6 © 2015 L.C. Hoe

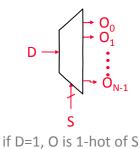

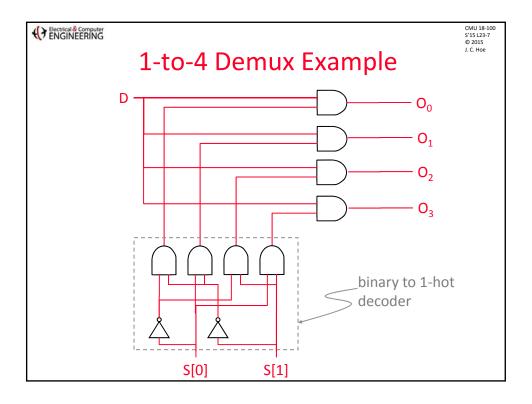

### Demultiplexer (aka demux)

• Example: 1-bit 1-to-2 demultiplexer

| S | D | <b>O</b> <sub>0</sub> | 0, |

|---|---|-----------------------|----|

| 0 | 0 | 0                     | 0  |

| 0 | 1 | 1                     | 0  |

| 1 | 0 | 0                     | 0  |

| 1 | 1 | 0                     | 1  |

or simply

$$\begin{array}{c|c} S & O_0 & O \\ \hline O & D & O \\ \hline 1 & O & D \end{array}$$

- Generalizable to 1-to-N demux'ing

- Does it also make sense to demux a bus?

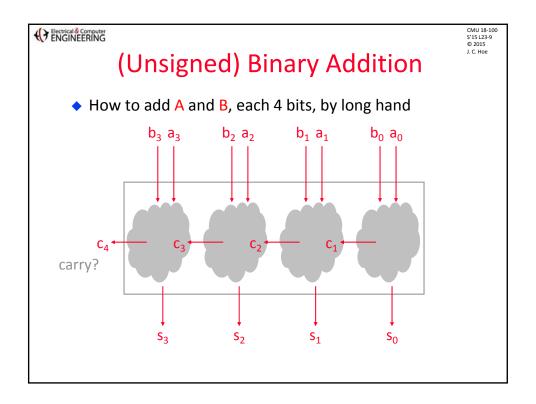

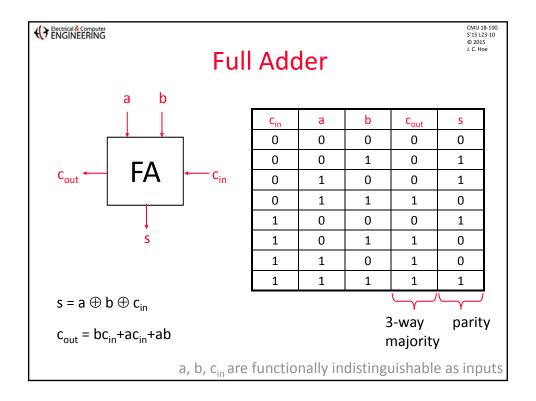

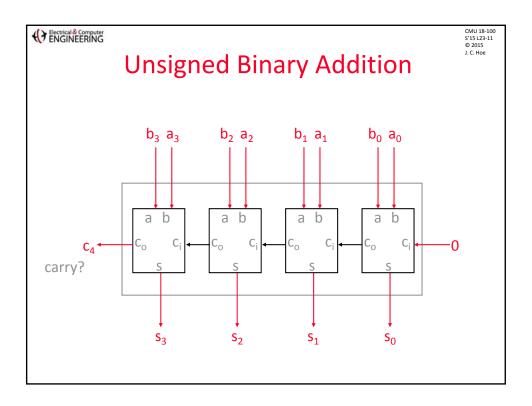

# Cost and Speed of an n-bit "Ripple-Carry" Adder • Cost is n x SizeOf( Full Adder ) • S and Cout do not change instantaneously when a and b are changed - longest delay (aka Critical Path Delay) is from ao, bo, or cin to sn-1 or cout - n x DelayOf( Full Adder ) - n x 2 gate delays (assuming 2-level SOP is used) by a 1 by a 2 by a 3 by a 3 by a 4 BTW, ripple-carry is adder design for babies . . . . Sn-1

irregular combinational functions

€ ENGINEERING

CAU 18-100

\$'15 123-18

© 2015

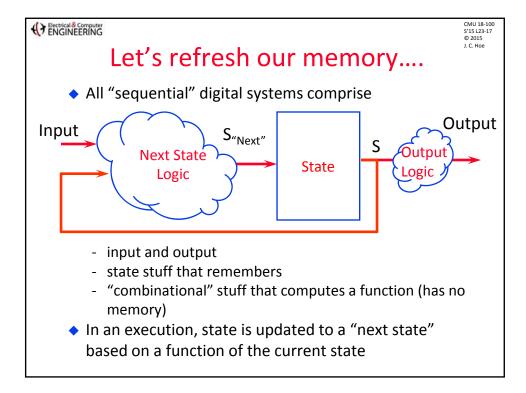

### Memory 101

Pure combinational logic always go from a current input to a current output without any looping back

There is no notion of time, past or future

- To remember, must somehow incorporate previous values

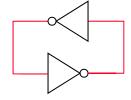

- You mean like this?

Does it remember? What does it remember? (It is easier to see if you associate a small propagation delay with wires and gates)