# 18-100 Lecture 19: Intro to AVR Assembly Programming

James C. Hoe Dept of ECE, CMU March 26, 2015

Today's Goal: Get ready for Lab 9

Announcements: HW#7 due today

Midterm 2 next Tuesday!!

Handouts: Lab 9 (on Blackboard)

Atmel 8-bit AVR ATmega8 Databook (on Blackboard)

Atmel 8-bit AVR Instruction Set Manual (on Blackboard)

Electrical & Computer ENGINEERING

CMU 18-100 S'15 L19-5 © 2015 J. C. Hoe

# ENIAC: "first" electronic digital computer (Eckert and Mauchly, 1946)

from The ENIAC Museum, http://www.seas.upenn.edu/~museum/

- 18,000 vacuum tubes

- 30 ton, 80 by 8.5 feet

- 1900 additions per second

- 20 10-decimal-digit words (100-word core by 1952)

- programmed by 3000 switches in the function table and plug-cables (became stored program in 1948)

Electrical & Computer ENGINEERING

CMU 18-10 S'15 L19-6 © 2015 J. C. Hoe

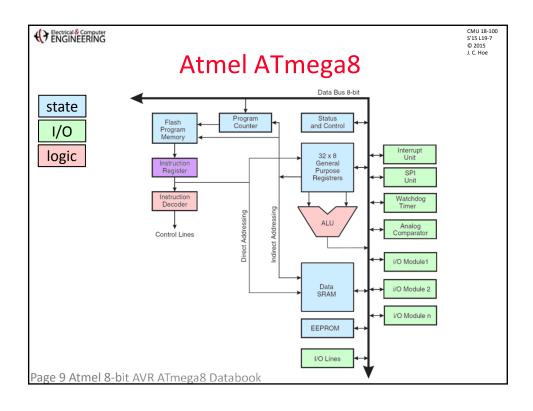

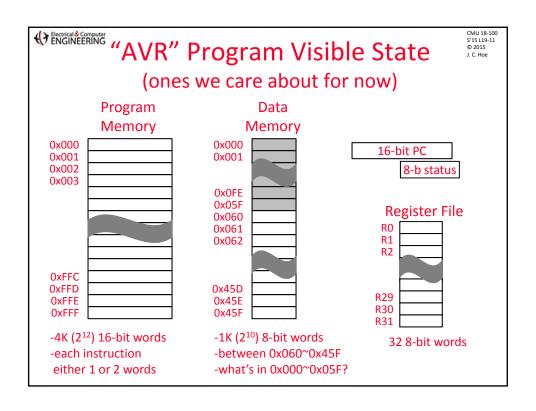

### Your Computer: Atmel ATmega8

[image from Wikipedia]

- ◆ ~\$3.00 each

- may be ~10K gates

- clock up to 16MHz

- 1KB Data SRAM (8-bit words)

- 8KB Program Memory (Flash)

- BTW, a modern high-end CPU (e.g., Intel Xeon)

- billions of transistors (10+ cores)

- many GHz (approaching 100 GFLOPs/sec)

- 10s of MB in just caches

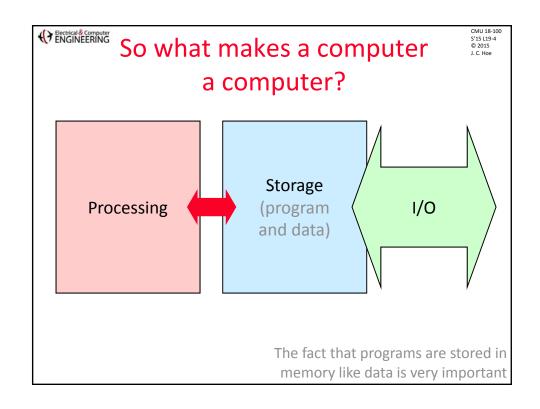

Stored Program Architecture

[Burks, Goldstein, von Neumann, 1946]

• By far the most common architectural paradigm

• Memory holds both program and data

- instructions and data in a linear memory array

- instructions can be modified just like data

• Sequential instruction processing

1. program counter (PC) identifies the current instruction

2. instruction is fetched from memory

3. instruction execution causes some state (e.g. memory)

to be updated as a specific function of current state

4. program counter is advanced (according to instruction)

5. repeat

#### Electrical & Computer ENGINEERING

#### CMU 18-10 S'15 L19-10 © 2015 J. C. Hoe

#### An Instruction Set Architecture

- Abstracting a processor/computer as

- program visible state

- memory, registers, program counters, etc.

- set of instructions to modified state; each prescribes

- which state elements are read as operands

- which state elements are updated and to what new values

- where is the next instruction

- Other details

- instruction-to-binary encoding

- data format and size

- how to interface with the outside world?

- protection and privileged operations

- software conventions

CMU 18-10 S'15 L19-13 © 2015

### **Other ALU Instructions**

| Mnemonics      | Operands                              | Description                              | Operation                           |  |

|----------------|---------------------------------------|------------------------------------------|-------------------------------------|--|

| ARITHMETIC AND | LOGIC INSTRUCTION                     | NS                                       | 757.1                               |  |

| ADD            | Rd, Rr Add two Registers Rd ← Rd + Rr |                                          | Rd ← Rd + Rr                        |  |

| ADC            | Rd, Rr                                | Add with Carry two Registers             | $Rd \leftarrow Rd + Rr + C$         |  |

| ADIW           | Rdl,K                                 | Add Immediate to Word                    | Rdh:Rdl ← Rdh:Rdl + K               |  |

| SUB            | Rd, Rr                                | Subtract two Registers                   | Rd ← Rd - Rr                        |  |

| SUBI           | Rd, K                                 | Subtract Constant from Register          | Rd ← Rd - K                         |  |

| SBC            | Rd, Rr                                | Subtract with Carry two Registers        | Rd ← Rd - Rr - C                    |  |

| SBCI           | Rd, K                                 | Subtract with Carry Constant from Reg.   | Rd ← Rd - K - C                     |  |

| SBIW           | Rdl,K                                 | Subtract Immediate from Word             | Rdh:Rdl ← Rdh:Rdl - K               |  |

| AND            | Rd, Rr                                | Logical AND Registers                    | Rd ← Rd • Rr                        |  |

| ANDI           | Rd, K                                 | Logical AND Register and Constant        | Rd ← Rd • K                         |  |

| OR             | Rd, Rr                                | Logical OR Registers                     | Rd ← Rd v Rr                        |  |

| ORI            | Rd, K                                 | Logical OR Register and Constant         | Rd ← Rd v K                         |  |

| EOR            | Rd, Rr                                | Exclusive OR Registers                   | $Rd \leftarrow Rd \oplus Rr$        |  |

| COM            | Rd                                    | One's Complement                         | $Rd \leftarrow 0xFF - Rd$           |  |

| NEG            | Rd                                    | Two's Complement                         | Rd ← 0x00 – Rd                      |  |

| SBR            | Rd.K                                  | Set Bit(s) in Register                   | Rd ← Rd v K                         |  |

| CBR            | Rd,K                                  | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \cdot (0xFF - K)$ |  |

| INC            | Rd                                    | Increment                                | Rd ← Rd + 1                         |  |

| DEC            | Rd                                    | Decrement                                | Rd ← Rd – 1                         |  |

| TST            | Rd                                    | Test for Zero or Minus                   | Rd ← Rd • Rd                        |  |

| CLR            | Rd                                    | Clear Register                           | Rd ← Rd ⊕ Rd                        |  |

| SER            | Rd                                    | Set Register                             | Rd ← 0xFF                           |  |

| MUL            | Rd, Rr                                | Multiply Unsigned                        | R1:R0 ← Rd x Rr                     |  |

| MULS           | Rd, Rr                                | Multiply Signed                          | R1:R0 ← Rd x Rr                     |  |

| MULSU          | Rd, Rr                                | Multiply Signed with Unsigned            | R1:R0 ← Rd x Rr                     |  |

| FMUL.          | Rd, Rr                                | Fractional Multiply Unsigned             | R1:R0 ← (Rd x Rr) << 1              |  |

| FMULS          | Rd, Rr                                | Fractional Multiply Signed               | R1:R0 ← (Rd x Rr) << 1              |  |

| FMULSU         | Rd. Rr                                | Fractional Multiply Signed with Unsigned | R1:R0 ← (Rd x Rr) << 1              |  |

Page 282 Atmel 8-bit AVR ATmega8 Databook

#### Electrical & Computer ENGINEERING

CMU 18-100 S'15 L19-14 © 2015

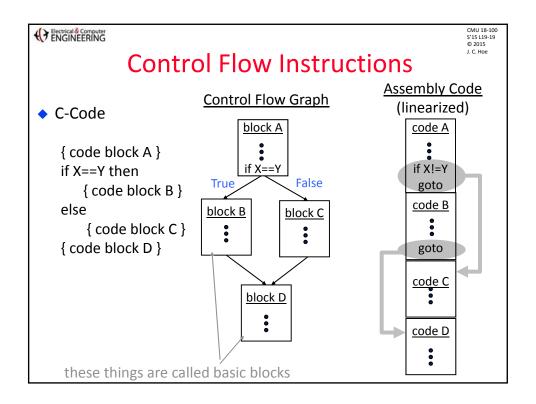

# **Assembly Programming 101**

- Break down high-level program constructs into a sequence of elemental operations

- E.g. High-level Code

```

f = (g + h) - (i + j)

```

- Assembly Code

- suppose g, h, i, j are in r15, r16, r17, r18 and do not need to be preserved

```

add r15, r16 ; r15 = g+h

add r17, r18 ; r17 = i+j

sub r15, r17 ; r15 = f

```

What if we do want to preserve r15~r18?

CMU 18-10 S'15 L19-15 © 2015 L.C. Hoe

#### **General Instruction Classes**

- Arithmetic and logical operations

- fetch operands from specified locations

- compute a result as a function of the operands

- store result to a specified location

- update PC to the next sequential instruction

- Data movement operations

- fetch operands from specified locations

- store operand values to specified locations

- update PC to the next sequential instruction

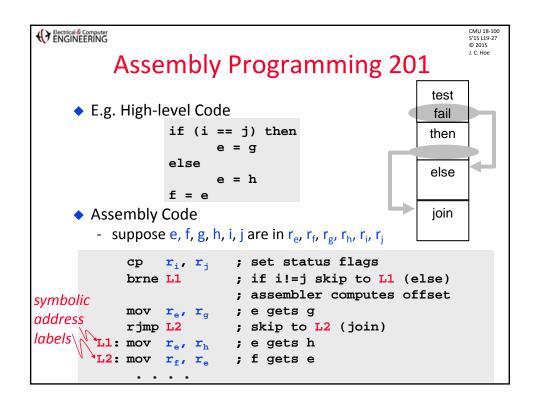

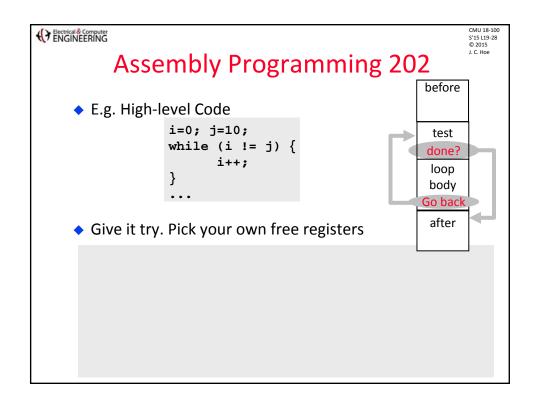

- Control flow operations

Page 20 Atmel 8-bit AVR Instruction Set Manual

- fetch operands from specified locations

- compute a branch condition and a target address

- if "branch condition is true" then PC ← target address

else  $PC \leftarrow$  next seq. instruction

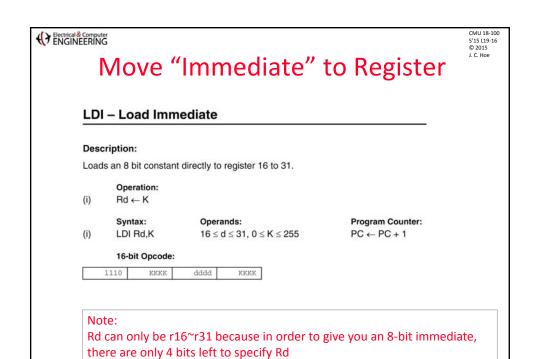

# Move Register to Register (Copy)

#### MOV - Copy Register

#### Description:

This instruction makes a copy of one register into another. The source register Rr is left unchanged, while the destination register Rd is loaded with a copy of Rr.

#### Operation:

Rd ← Rr

MOV Rd,Rr

Operands:  $0 \le d \le 31, \ 0 \le r \le 31$  **Program Counter:**

PC ← PC + 1

16-bit Opcode:

11rd dddd rrrr

> We wait until next time to see "load" (i.e., move memory to register) and "store" (i.e., move register to memory)

Page 101 Atmel 8-bit AVR Instruction Set Manual

Electrical & Computer ENGINEERING

## **Assembly Programming 102**

- Break down high-level program constructs into a sequence of elemental operations

- E.g. High-level Code

f = (g + h) - (i + j)

- Assembly Code

- suppose g, h, i, j are in r15, r16, r17, r18 and should be preserved; put result f in r19; assume r20 is "free"

CMU 18-100 S'15 L19-21 © 2015 J. C. Hoe

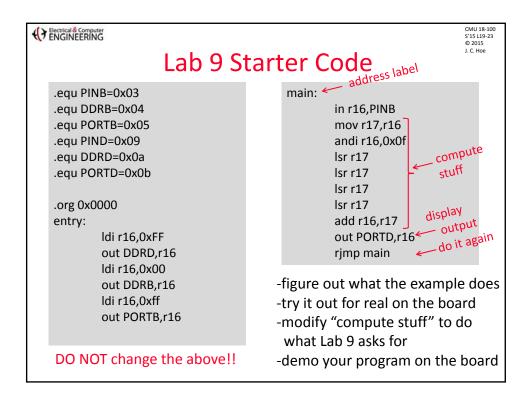

## That is enough for Lab 9

Extrical & Computer S13 L19-24 © 2015

Now back to the regularly scheduled program

Electrical & Computer ENGINEERING

CMU 18-100 S'15 L19-29 © 2015

### **Useful ALU Instructions**

◆ ADD Rd, Rr — Add registers Rd←Rd+Rr ADC Rd, Rr — Add registers w. carry Rd←Rd+Rr+C ◆ SUB Rd, Rr — Subtract registers Rd←Rd-Rr ◆ AND Rd, Rr — AND registers Rd←Rd•Rr ◆ OR Rd, Rr — OR registers Rd←Rd|Rr ◆ INC Rd Increment register Rd←Rd+1 DEC Rd Decrement register Rd←Rd-1 Left shift register ◆ LSL Rd Rd←Rd<<1 ◆ LSR Rd Right shift register Rd←Rd>>1 Right shift register Rd←Rd>>1 ASR Rd (sign-extend) ◆ ADIW Rd, k — 16-bit add register-R(d+1):Rd=R(d+1):Rd+k immediate

Electrical & Computer ENGINEERING

## Useful Data Movement Instructions

CMU 18-100 S'15 L19-30 © 2015 J. C. Hoe

| <ul><li>LDI</li></ul> | Rd,K | <ul> <li>Load Immediate</li> </ul>          | Rd←K   |

|-----------------------|------|---------------------------------------------|--------|

| ♦ LDS                 | Rd,k | <ul><li>Load from SRAM</li></ul>            | Rd←(k) |

| ◆ LD                  | Rd,X | <ul> <li>Load register indirect</li> </ul>  | Rd←(X) |

| ◆ STS                 | k,Rr | <ul> <li>Store data to SRAM</li> </ul>      | (k)←Rr |

| ST                    | X,Rr | <ul> <li>Store register indirect</li> </ul> | (X)←Rr |

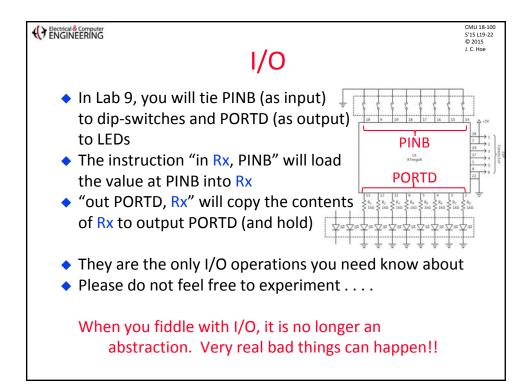

| ◆ IN                  | Rd,P | <ul> <li>Read from port</li> </ul>          | Rd←P   |

| <ul><li>OUT</li></ul> | P,Rr | <ul><li>Write to port</li></ul>             | P←Rr   |

Electrical & Computer ENGINEERING

CMU 18-100 S'15 L19-31 © 2015

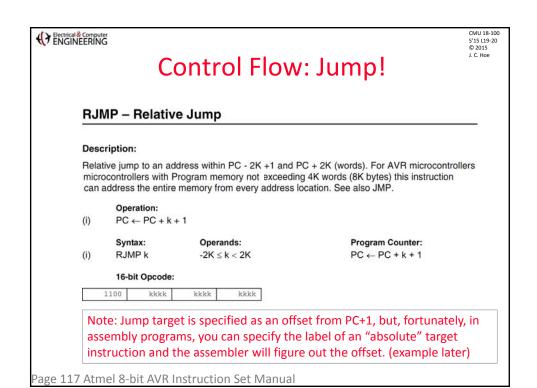

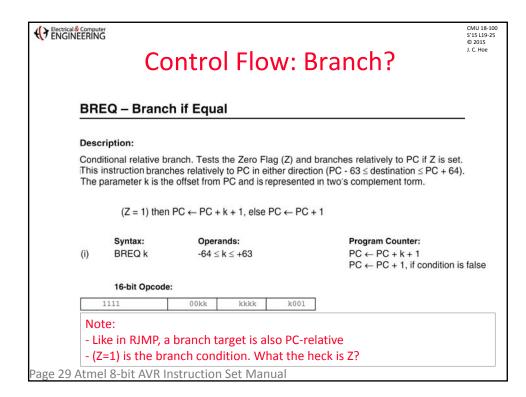

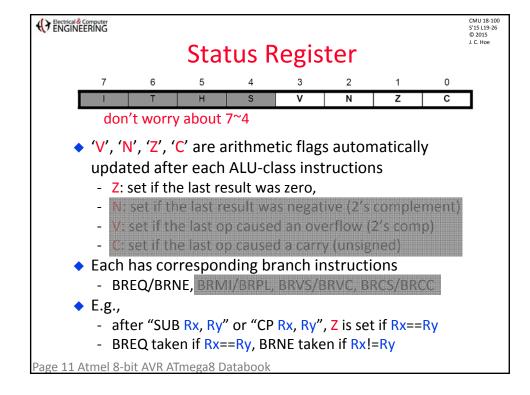

### **Useful Control Flow Instructions**

- ◆ RJMP k Jump to k, where k is a memory address (label)

- ◆ CP Rd,Rr Subtract Rd by Rr and set status flag but does not update Rd

- ◆ BREQ k Branch to k if Z is set

(branch if Rd==Rr following CP Rd, Rr)

- ◆ BRNE k Branch to k if Z is clear (branch if Rd!=Rr following CP Rd, Rr)

- ◆ BRMI k Branch to k if S is set

(branch if Rd<Rr following CP Rd, Rr)</p>

- ◆ BRPL k Branch to k if S is clear (branch if Rd>=Rr following CP Rd, Rr)