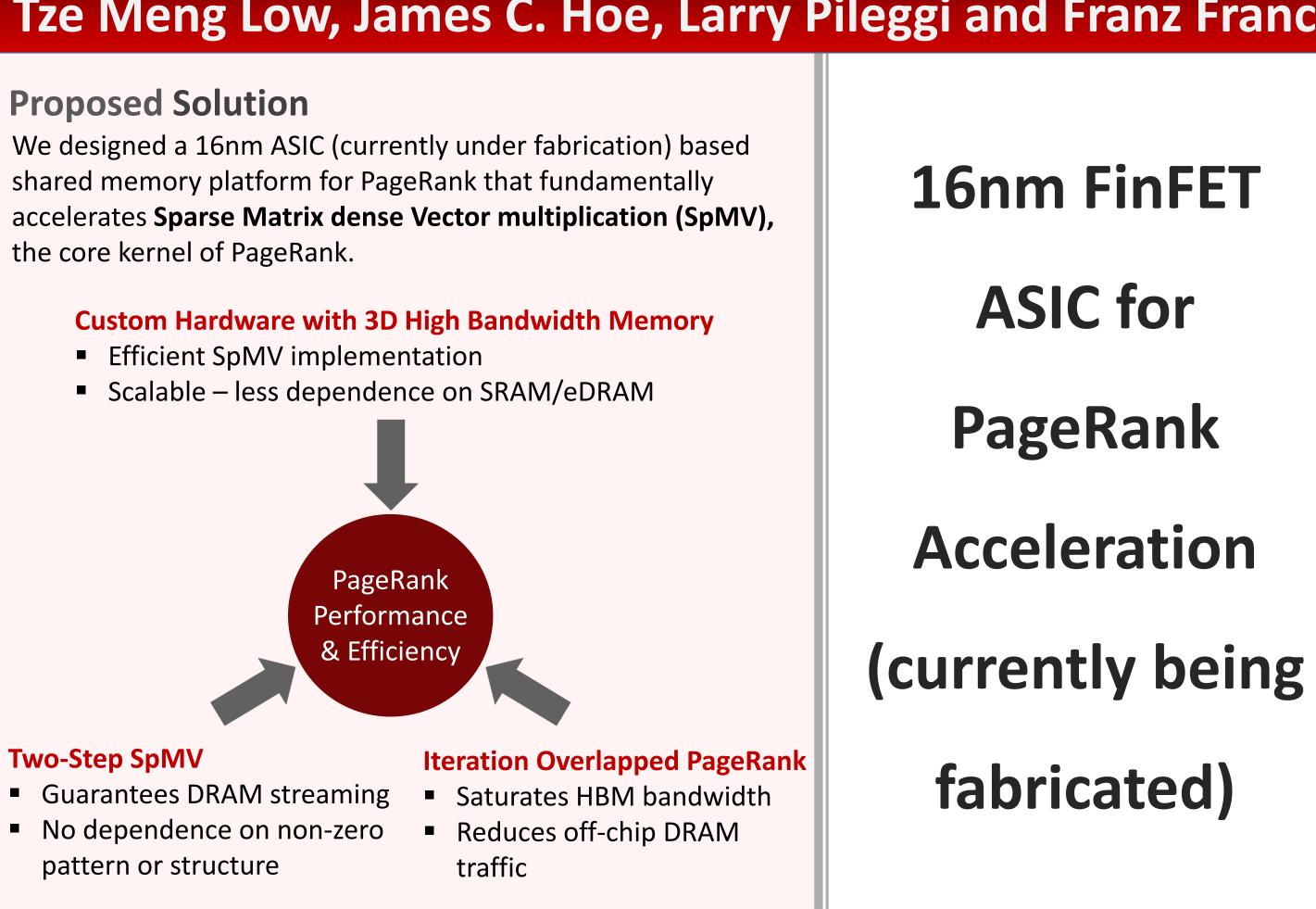

# PageRank Acceleration for Large Graphs with Scalable Hardware and Two-Step SpMV

# Fazle Sadi, Joe Sweeney, Scott McMillan, Tze Meng Low, James C. Hoe, Larry Pileggi and Franz Franchetti

Google

0.5 TB/s

# **Research Problem**

PageRank is a widely used iterative algorithm that ranks the vertices of a graph according to their relative importances. However, it suffers from poor performance and efficiency due to notorious memory access behavior. More importantly, when graphs become bigger and sparser, PageRank applications are inhibited as most solutions profoundly rely on large random access fast memory, which is not easily scalable.

PageRank vector:  $\mathbf{x}_i = \alpha \mathbf{x}_i^T \mathbf{A} + (1 - \alpha) \mathbf{x}_i^T \frac{ee^T}{N}$

# **Target Graphs**

- Very large (~billion nodes)

- Highly sparse (average degree < 10)</li>

- No exploitable non-zero pattern

# Key Goals

- Streaming DRAM access

- Full utilization of streaming bandwidth

- Off-chip DRAM traffic reduction

- Low requirement of fast on-chip memory (scalability)

# **Background on SpMV**

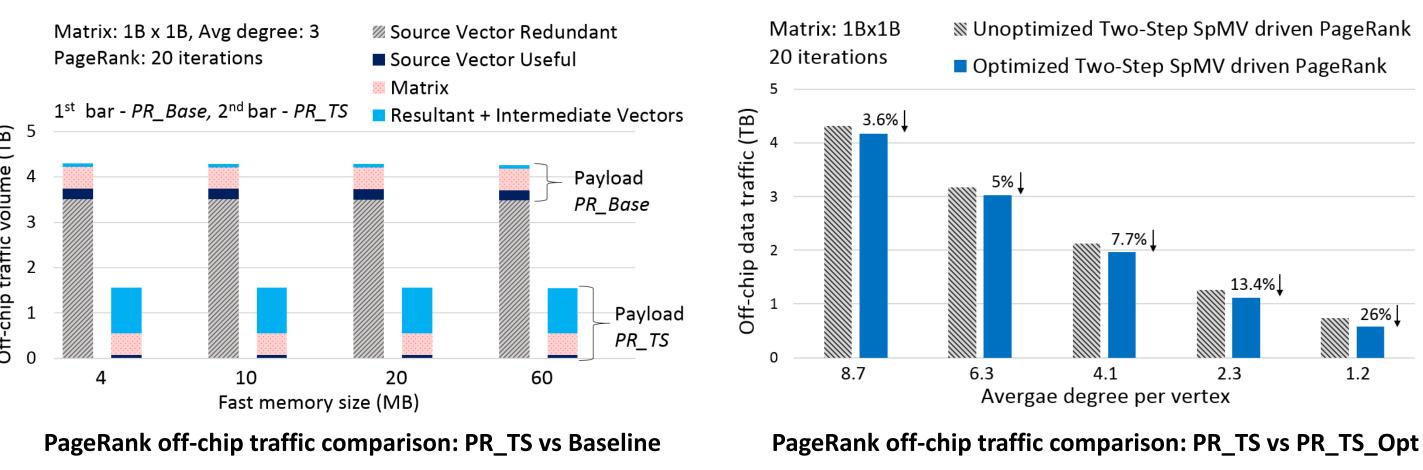

SpMV, the core operation of PageRank, requires random access to dense vector which is too large for the last level cache. This results in random access to DRAM, affecting performance and efficiency in many ways. Below is a comparison of required vs redundant data transfer and dram page openings of baseline SpMV on a example problem.

Example: 80M x 80M matrix, 3 NNZ per row, 1KB DRAM page, 64B cache block, double precision data

|                       | Redundant |     |     |  |

|-----------------------|-----------|-----|-----|--|

| Data Volume - 19GB    | 37%       |     | 63% |  |

| Number of Page Opened | - 20M     | 16% | 84% |  |

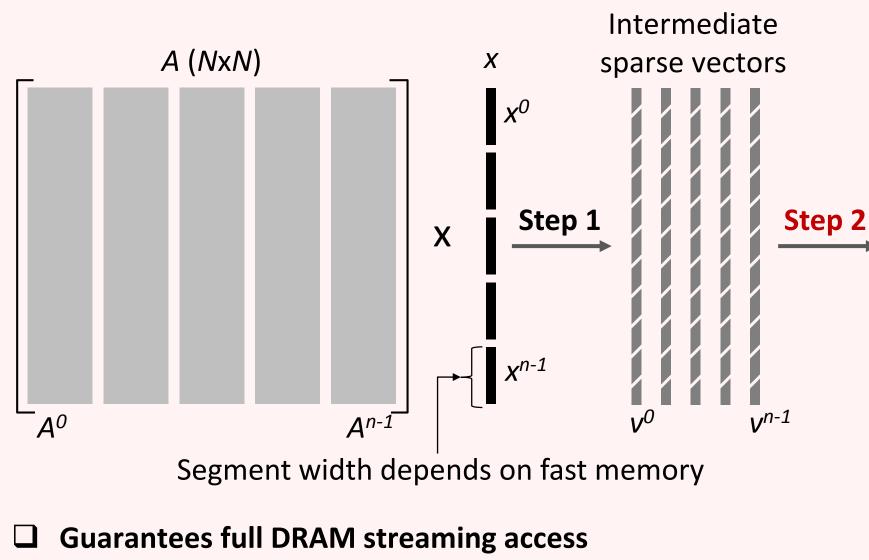

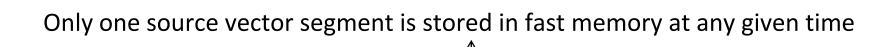

# Two-Step SpMV Algorithm

This algorithm conducts SpMV in two separate steps. It requires column blocking of the matrix and segmentation of the source vector

Reduces off-chip traffic and Enables high bandwidth utilization **Requires custom hardware for efficient multi-way merge**

# Less Dependence on SRAM - More Scalable

| Solution                 | Fast memory<br>(MB) | Max. nodes<br>reported |

|--------------------------|---------------------|------------------------|

| FPGA [3]                 | 8.4                 | 2.3M                   |

| ASIC [4]                 | 32                  | 8M                     |

| CPU (single socket ) [5] | 20                  | 95M                    |

| CPU (single socket ) [6] | 50                  | <b>118M</b>            |

| PR_TS_Opt (proposed)     | 11                  | <b>2</b> B             |

| PR_TS (proposed)         | 11                  | <b>4</b> B             |

# **Two-Step SpMV** pattern or structure

# PageRank using Two-Step SpMV (PR\_TS)

Two-Step SpMV is conducted independently in each iteration of PageRank **Q** Resultant vector of one iteration is the source vector of the next, communicated via DRAM **□** Either Step1 or Step2 is conducted at any given time, keeping other part of the circuit inactive

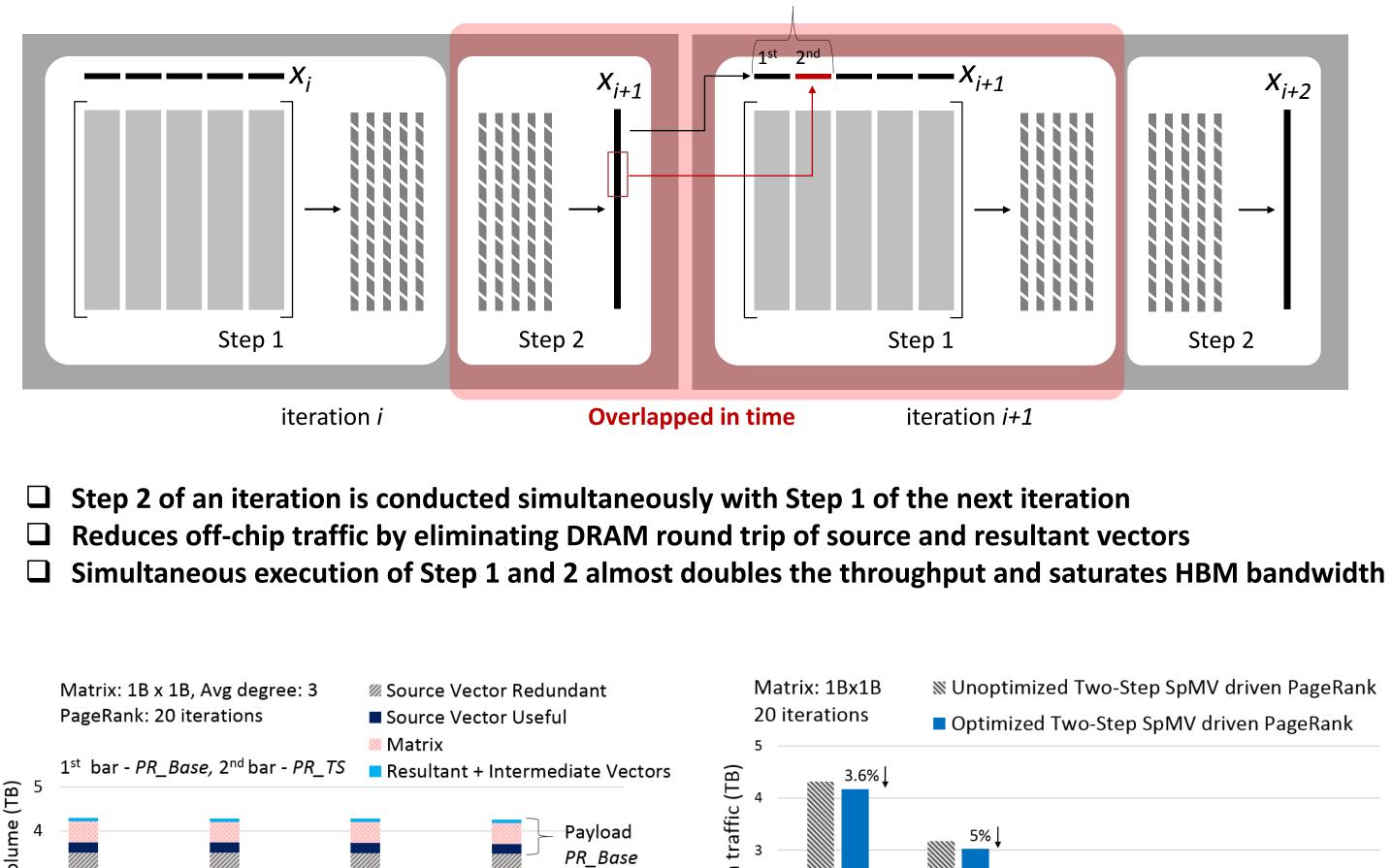

# **Optimized PageRank by Iteration Overlap (PR\_TS\_Opt)**

Two source vector segment storages in fast memory are required: 1) for computation of Step1 in iteration *i*+1 and 2) for storing output of Step 2 in iteration *i*.

# Contact: fsadi@cmu.edu

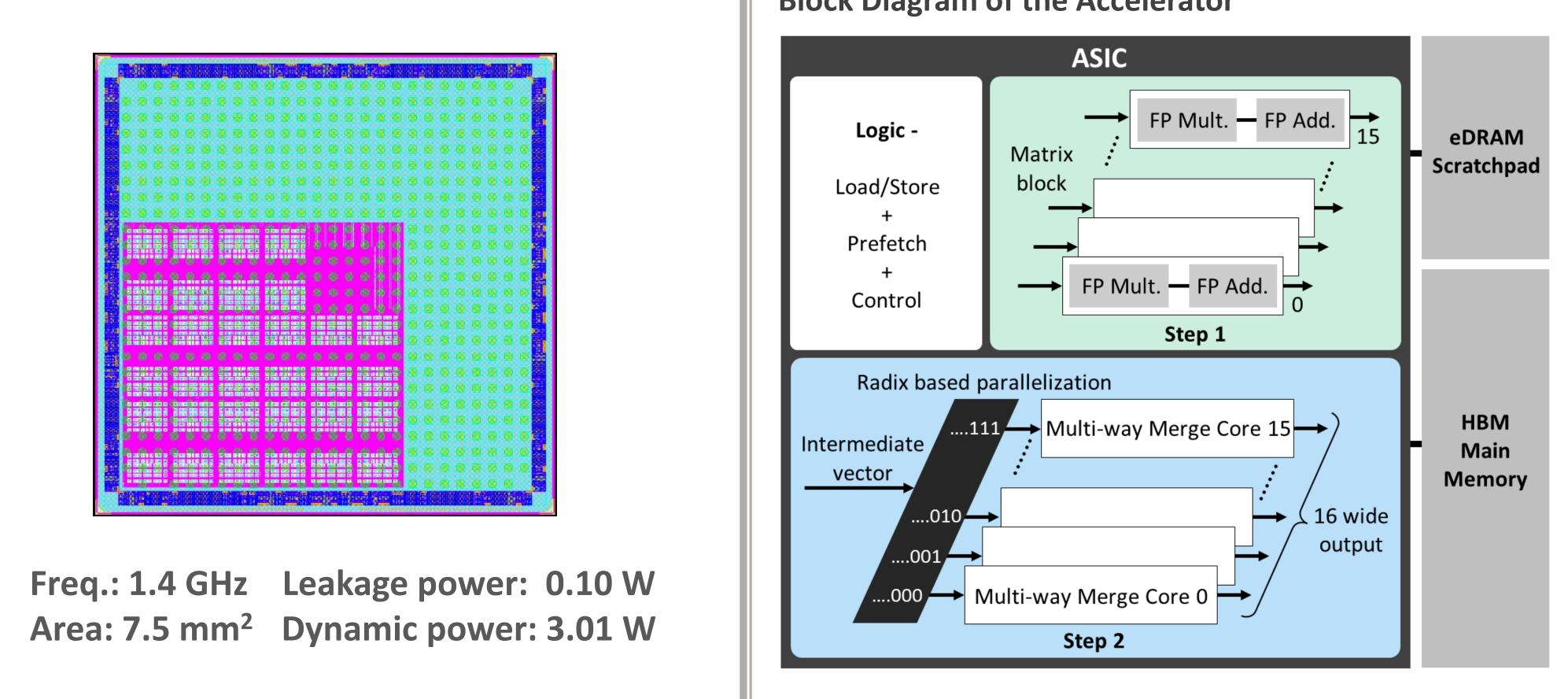

# **Experimental Results** Streaming speed PR\_TS 346 GB/s Src. vec. load (step 1) 512 GB/s 297 GB/s Partial SpMV (step 1) System's peak 432 GB/s streaming speed Merge (step 2) Streaming speed 729 GB/s PR\_TS\_Opt ■ Bmark1 ■ Bmark2 ◎ PR\_TS ■ PR\_TS\_Opt (s) 100 10 kr25 Twi-m PLD Web Twi-f SD1 Sy-.5B Sy-1B Sy-2B kr24 100 (%) 15 25 Ed kr24 kr25 Twi-m PLD Web Twi-f SD1 Sy-.5B Sy-1B Sy-2B kr24 Bmark1 – Single socket CPU implementation [5], Bmark2 – Dual socket CPU implementation [6] Graph kr24 kr25 Twi-m PLD Web # Nodes (M) 16.7 42.9 118 33.5 52.5 16.1 14.5 8.6 Avg. degree 31.3 37.4 268 1963 # Edges (M) 1047 623 1014 Acknowledgements 26% This work was supported in part by Defense Advanced Research Projects Agency (DARPA) contract HR0011-16-C-0038, "Circuit Realization At Faster Timescales (CRAFT)". This material is also based upon work funded and supported by the Department of Defense under Contract No. FA8702-15-D-0002 with Carnegie Mellon University for the operation of the Software

# **Carnegie Mellon University**

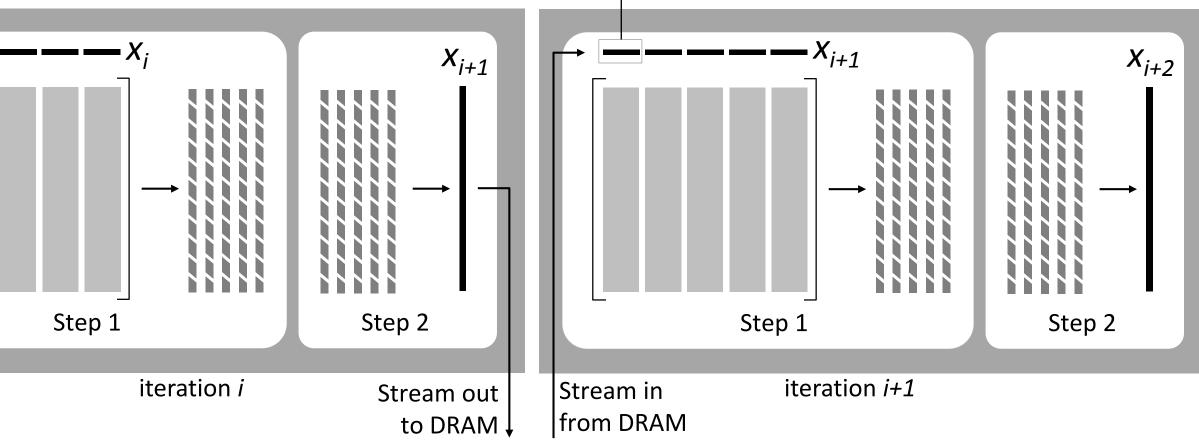

**Block Diagram of the Accelerator**

**Optimized Two-Step driven** PageRank (PR\_TS\_Opt) attains much higher throughput with the same silicon area and saturates HBM's extreme off-chip bandwidth .

| Twi-f | SD1  | Sy5B | Sy-1B | Sy-2B |

|-------|------|------|-------|-------|

| 61.6  | 94.9 | 500  | 1000  | 2000  |

| 23.8  | 20.4 | 3    | 2     | 1.1   |

| 1468  | 1936 | 1500 | 2000  | 2200  |

Engineering Institute, a federally funded research and development center [DM18-0845]. Additionally, this work was sponsored by DARPA contract HR0011-13-2-0007, "Power Efficiency Revolution for Embedded Computing Technologies (PERFECT)". The view, opinions, and/or findings contained in this material are those of the author(s) and should not be construed as an official Government position, policy, or decision, unless designated by other documentation.