# Efficient Pre-Silicon Validation and Post-Silicon Tuning of Self-Healing Analog/RF Integrated Circuits

Submitted in partial fulfillment of the requirements for

the degree of

**Doctor of Philosophy**

in

**Electrical and Computer Engineering**

Fa Wang

B.S., Automation, Tsinghua University

Carnegie Mellon University Pittsburgh, PA

December, 2015

#### **Abstract**

The advent of the nanoscale integrated circuit (IC) technology makes high performance analog and RF circuit increasingly susceptible to large-scale process variations. Process variations, including inter-die variations and local mismatches, significantly impact the parametric yield of analog/RF circuit, and must be properly handled at all levels of design hierarchy. Traditional approaches based on over-design are not sufficient to maintain high parametric yield, due to the large-scale process variations and aggressive design specifications at advanced technology nodes. In this context, the self-healing circuit has emerged as promising methodology to address the variability issue. In this thesis, we propose efficient pre-silicon validation and post-silicon tuning techniques, which are essential for the practical usage of self-healing methodology.

One important problem in self-healing methodology is to efficiently and accurately predict the parametric yield in pre-silicon. The main challenge of this problem is caused by multiple circuit states related to tuning knobs. Given that these circuit states closely interact with process variations, they must be properly modeled in order to accurately estimate the parametric yield. Towards this goal, we develop an efficient performance modeling algorithm, referred to Correlated Bayesian Model Fusion (C-BMF) that explores the correlation between circuit states. Next, based on the performance model, the self-healing behavior and the parametric yield can be efficiently and accurately predicted.

Another important problem in self-healing circuit is to efficiently perform post-silicon tuning. Towards this goal, indirect performance sensing methodology has recently attracted great attention. In the indirect performance sensing paradigm, the performance of interest (PoI) is not directly measured by onchip sensor, but is instead accurately predicted from an indirect sensor model. Such indirect sensor model takes a set of other performances as inputs, which are referred to as the performances of measurements (PoMs). The PoMs are selected such that they are highly correlated with PoI and are easy to measure. Due to the process shift associated with manufacturing lines, the indirect sensor model must be calibrated from

time to time. For the purpose of reducing the model calibration cost, we propose a Bayesian Model Fusion (BMF) algorithm that reuses the information collected in early stage of manufacturing. We further extend BMF to a Co-learning Bayesian Model Fusion (CL-BMF) algorithm that incorporates not only the early stage information, but also the current stage information that was not considered in the original modeling problem.

## Acknowledgement

First of all, I would like to express my deepest appreciation to my advisor, Prof. Xin Li for his guidance and persistent help on my Ph. D. study and research. He provided me with the important academic training in analytical, writing, presentation and learning skills. He continually and convincingly conveyed a spirit of adventure and passion.

This work would not be accomplished without the invaluable academic suggestions from my Ph. D. committee members. Not only did they carefully review my proposal and thesis, but also offered constructive insights on the research presented in this thesis. I would like to express my gratefulness to Prof. Shawn Blanton for kindly providing industrial connections, which inspires me to finish the cost analysis part of the thesis. I would like to thank Prof. Tamal Mukherjee for his instructions and helpful inputs regarding the side information selection of co-learning in the thesis. I would also like to thank Dr. Jean-Olivier Plouchart for all the active collaboration and inspirational discussions.

In addition, my sincere thankfulness goes to IBM and Intel. This work cannot be done without their cooperation and support. I would like to thank Alberto Valdes-Garcia and Bodhisatwa Sadhu from IBM for providing their self-healing circuit data and continued discussion and support. I would like to thank Chenjie Gu from Intel for meaningful exchanges of ideas on Bayesian Model Fusion algorithm development. I would also like to acknowledge the financial support for this work from DARPA HEALICS program, National Science Foundation and C2S2 Focus Center.

Last but not least, I would like to thank my group-mates and friends at Carnegie Mellon University for their friendship and academic inspirations. Many thanks also belong to my parents and my beloved for their continuous encouragement and unyielding support.

# **Table of Contents**

| Chapter 1 | Introduction                                              | 12 |

|-----------|-----------------------------------------------------------|----|

| 1.1       | Traditional Robust Design Techniques                      | 14 |

| 1.2       | On-Chip Self-Healing Methodology                          | 16 |

| 1.2.1     | Components of On-Chip Self-Healing                        | 17 |

| 1.2.2     | Design Flow of On-Chip Self-Healing                       | 18 |

| 1.3       | Pre-Silicon Validation of Self-Healing Circuit            | 19 |

| 1.4       | Post-Silicon Tuning of Self-Healing Circuit               | 23 |

| 1.5       | Cost Analysis                                             | 24 |

| 1.6       | Thesis Contributions                                      | 26 |

| 1.7       | Thesis Organization                                       | 28 |

| Chapter 2 | Efficient Pre-Silicon Validation via Performance Modeling | 30 |

| 2.1       | Motivation                                                | 30 |

| 2.2       | Prior Knowledge Definition                                | 32 |

| 2.3       | Maximum-A-Posteriori Estimation                           | 34 |

| 2.4       | Hyper-Parameter Inference                                 | 35 |

| 2.5       | Algorithm Summary                                         | 38 |

| 2.6       | Performance Modeling Results                              | 40 |

| 2.6.1     | Low-Noise Amplifier                                       | 40 |

| 2.6.2     | Down-conversion Mixer                                     | 42 |

| 2.7       | Parametric Yield Estimation of Self-Healing Circuits      | 43 |

| 2.8       | Yield Estimation Results                                  | 46 |

| 2.8.1     | Low-Noise Amplifier                                       | 47 |

| 2.8.2     | Down-Conversion Mixer                                              | 49 |

|-----------|--------------------------------------------------------------------|----|

| 2.9       | Summary                                                            | 51 |

| Chapter 3 | Efficient Post-Silicon Tuning via Indirect Performance Sensing     | 53 |

| 3.1       | Motivation                                                         | 53 |

| 3.2       | Indirect Performance Sensing                                       | 55 |

| 3.3       | Pre-Silicon Indirect Sensor Modeling via Sparse Regression         | 56 |

| 3.4       | Post-Silicon Indirect Sensor Calibration via Bayesian Model Fusion | 59 |

| 3.4.1     | Prior Knowledge Definition                                         | 60 |

| 3.4.2     | Maximum-A-Posteriori Estimation                                    | 62 |

| 3.5       | On-Chip Self-Healing Flow                                          | 65 |

| 3.6       | Case Study                                                         | 68 |

| 3.7       | Summary                                                            | 74 |

| Chapter 4 | Co-Learning Bayesian Model Fusion for Indirect Sensor Modeling     | 75 |

| 4.1       | Motivation                                                         | 75 |

| 4.2       | Performance Side Information for Co-Learning                       | 78 |

| 4.3       | Likelihood Model of Physical Samples                               | 80 |

| 4.4       | Likelihood Model of Pseudo Samples                                 | 82 |

| 4.5       | Bayesian Inference for Co-Learning                                 | 83 |

| 4.6       | Implementation Details                                             | 85 |

| 4.6.1     | Prior Definition                                                   | 85 |

| 4.6.2     | Cross-Validation                                                   | 87 |

| 4.6.3     | Side Information Selection                                         | 88 |

| 4.6.4     | Summary                                                            | 89 |

| 4.7       | Numerical Results                                                  | 89 |

| 4.7.1     | Low-Noise Amplifier                                                | 90 |

| 4.7.2     | Down-Conversion Mixer                                              | 93 |

| 4.8       | Summary                                                            | 95 |

| Chapter 5 | Cost Analysis of On-Chip Self-Healing                              | 96 |

| 5.1        | Motivation                   | 96  |

|------------|------------------------------|-----|

| 5.2        | Three Design Methodologies   | 97  |

| 5.3        | Cost per Good Chip           | 99  |

| 5.4        | Case Study                   | 105 |

| 5.5        | Summary                      | 108 |

| Chapter 6  | Thesis Summary & Future Work | 109 |

| 6.1        | Summary                      | 109 |

| 6.2        | Future Work                  | 111 |

| Bibliograp | ohy                          | 113 |

# **List of Figures**

| Figure 1-1. Robust analog/digital optimization algorithm flo | ow [7]15                                          |

|--------------------------------------------------------------|---------------------------------------------------|

| Figure 1-2. Challenges of robust circuit design is shown.    | With the scaling of IC technology, on one hand    |

| the process variations become larger, while                  | on the other hand the circuit specifications      |

| become more aggressive. As a result, the design              | n margin dramatically shrinks16                   |

| Figure 1-3. Three core components of on-chip self-healing    | are shown: tunable circuit block, sensing circuit |

| and controlling circuit. The three component                 | s are seamlessly integrated on-chip to achieve    |

| self-healing                                                 | 17                                                |

| Figure 1-4. Design flow of self-healing circuit is shown,    | which is consisted of four stages: (i) schematic  |

| design, (ii) layout design, and (iii) chip m                 | anufacturing, and (iv) post-silicon tuning and    |

| testing                                                      | 19                                                |

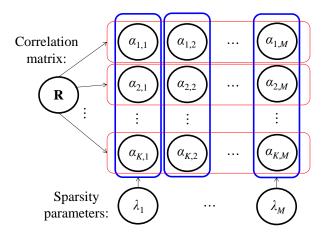

| Figure 2-1. The prior knowledge for model coefficients is il | lustrated33                                       |

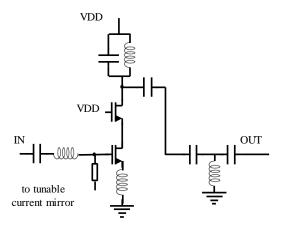

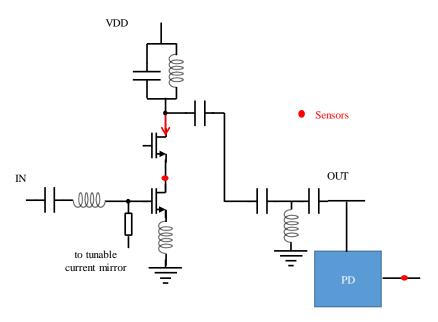

| Figure 2-2. The schematic of a tunable LNA designed in a c   | ommercial 32nm CMOS process is shown41            |

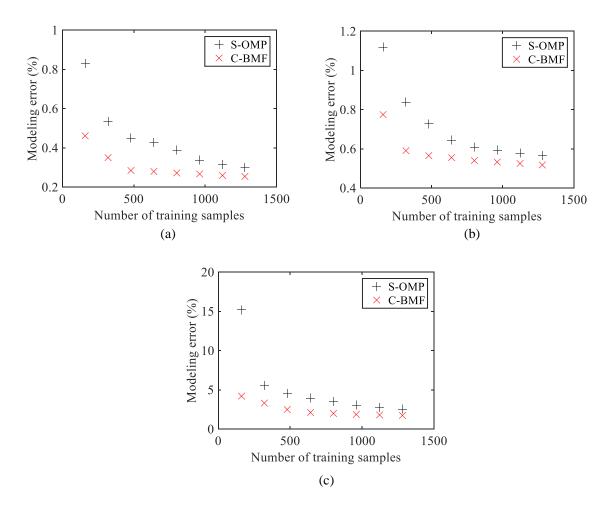

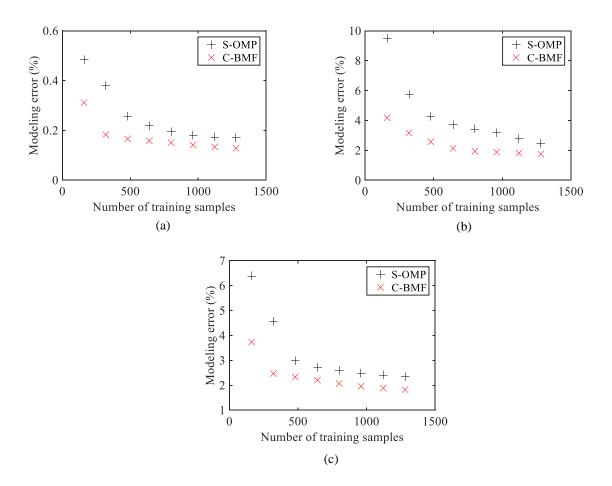

| Figure 2-3. The performance modeling error for NF, VG, a     | nd IIP3 are compared for (i) S-OMP and (ii) C-    |

| BMF method.                                                  | 41                                                |

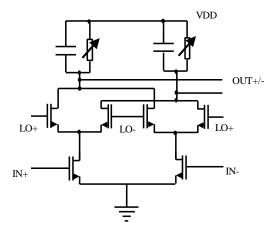

| Figure 2-4. The schematic of a tunable Mixer designed in a   | commercial 32nm CMOS process is shown42           |

| Figure 2-5. The performance modeling error for NF, VG, a     | nd I1dBCP are compared for (i) S-OMP and (ii)     |

| C-BMF method                                                 | 44                                                |

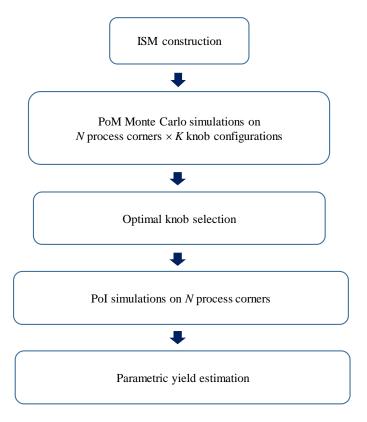

| Figure 2-6. Traditional parametric yield estimation flow of  | self-healing circuit46                            |

| Figure 2-7. Proposed parametric yield estimation flow of se  | f-healing circuit47                               |

| Figure 2-8. Schematic of a self-healing LNA                  | 48                                                |

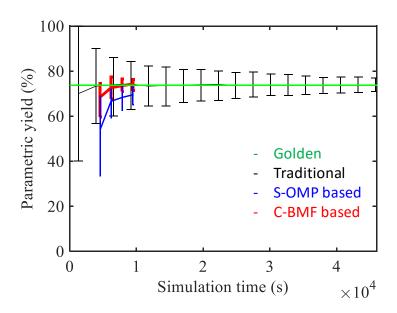

| Figure 2-9. Comparison of three parametric yield estimation  | n approaches: (i) Traditional, (ii) S-OMP based   |

| yield estimation, and (iii) C-BMF based yield                | estimation49                                      |

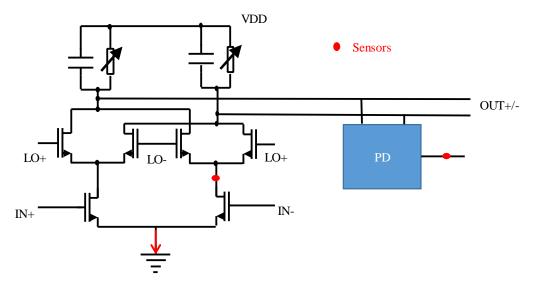

| Figure 2-10. Schematic of a self-healing down-conversion r   | nixer50                                           |

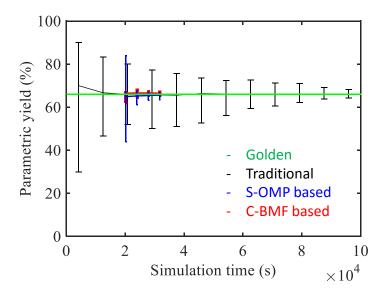

| Figure 2-11. Comparison of three parametric yield estimation approaches: (i) Traditional, (ii) S-OMP based               |

|--------------------------------------------------------------------------------------------------------------------------|

| yield estimation, and (iii) C-BMF based yield estimation                                                                 |

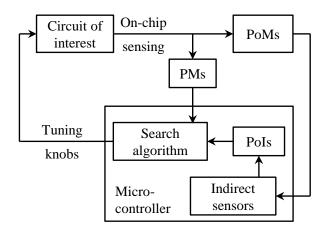

| Figure 3-1. A simplified block diagram describes the on-chip self-healing flow                                           |

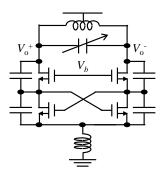

| Figure 3-2. A Simplified circuit schematic is shown for a Colpitts VCO                                                   |

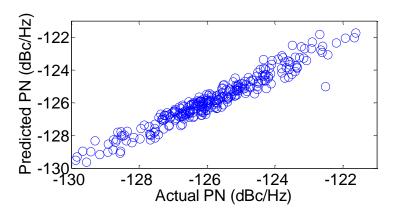

| Figure 3-3. Scatter plot is shown for the actual phase noise and the predicted phase noise based on the                  |

| simplified quadratic model                                                                                               |

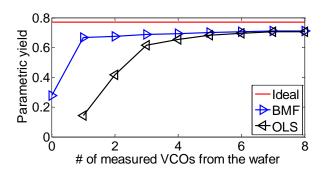

| Figure 3-4. Post-self-healing parametric yield of the wafer is shown as a function of the number of                      |

| measured VCOs from the wafer72                                                                                           |

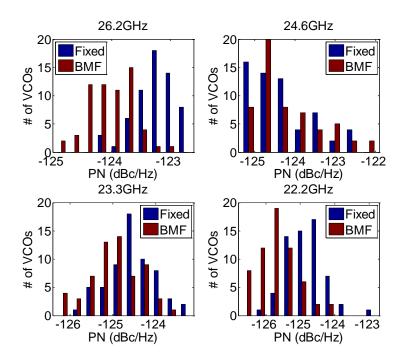

| Figure 3-5. Histogram of the measured phase noise values from all the VCOs on the wafer. Blue bars                       |

| represent the results from Fixed where bias code is 4, and red bars represent the results from                           |

| BMF where a single measured VCO is used from the wafer73                                                                 |

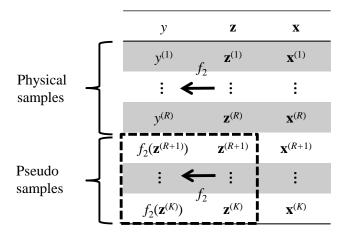

| Figure 4-1. The co-learning procedure is illustrated. The low-complexity model $f_2(\mathbf{z})$ is first fitted using a |

| small number of physical samples that are collected by simulation or measurement. Next, a                                |

| set of pseudo samples are generated for the PoI, as shown by the dashed box. Finally, the                                |

| high-complexity model $f_1(\mathbf{x})$ is fitted by using all the samples, including both the physical                  |

| samples and the pseudo samples79                                                                                         |

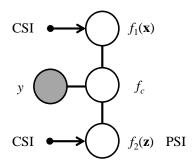

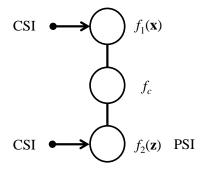

| Figure 4-2. A graphical model is shown to statistically model the likelihood of physical samples80                       |

| Figure 4-3. A graphical model is shown to statistically model the likelihood of pseudo samples82                         |

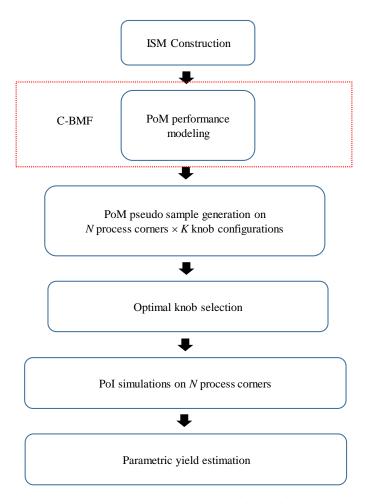

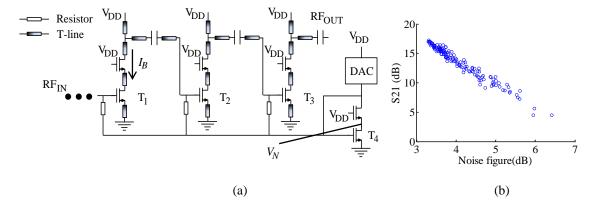

| Figure 4-4. The simplified circuit schematic is shown in (a) for a three-stage 60GHz low-noise amplifier                 |

| (LNA) designed in a commercial 32nm SOI CMOS process. The scatter plot of noise figure                                   |

| vs. S21 is shown in (b)90                                                                                                |

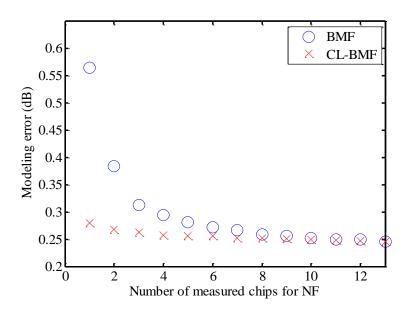

| Figure 4-5. The performance modeling error of noise figure (NF) is shown as a function of the number of                  |

| measured chips for NF92                                                                                                  |

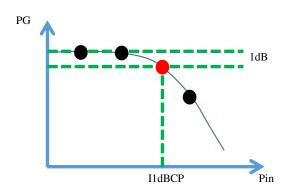

| Figure 4-6. I1dBCP measurement procedure is shown. In order to accurately extract I1dBCP, the input                      |

| power needs to be increased step by step until power gain is compressed by 1dB94                                         |

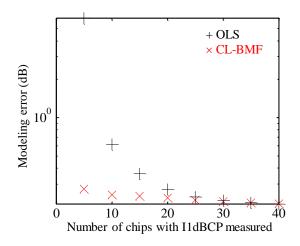

| Figure 4-7. Indirect sensor modeling error is compared for OLS and CL-BMF94                                              |

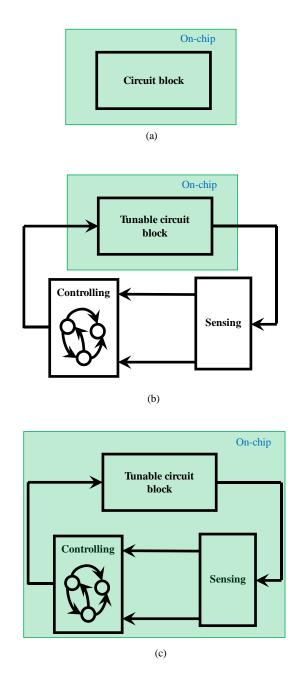

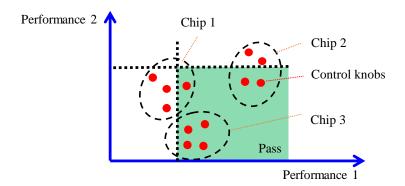

| Figure 5-1. Circuit components of three different design methodologies are shown: (a) traditional design                 |

| without tuning capacity (Traditional), (b) off-chip adaptive performance tuning (AT), and (c)                            |

| on-chip self-healing (OH)                                                                                 |

|-----------------------------------------------------------------------------------------------------------|

| Figure 5-2. Adaptive feature of tunable circuit block is shown. Each black dashed ellipsoid denotes one   |

| manufactured chip. Each red dot represents a particular knob configuration98                              |

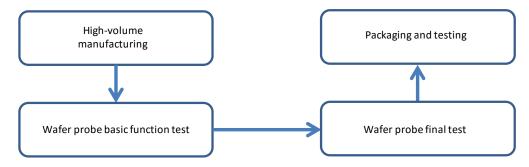

| Figure 5-3. The manufacturing and testing flow of traditional design is shown                             |

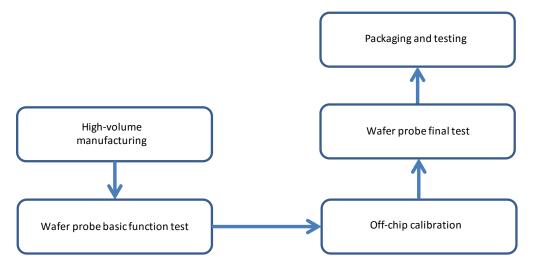

| Figure 5-4. The manufacturing and testing flow of off-chip adaptive performance tuning (AT) is shown. 100 |

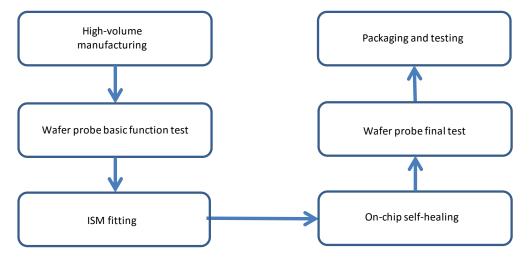

| Figure 5-5. The manufacturing and testing flow of on-chip self-healing (OH) is shown100                   |

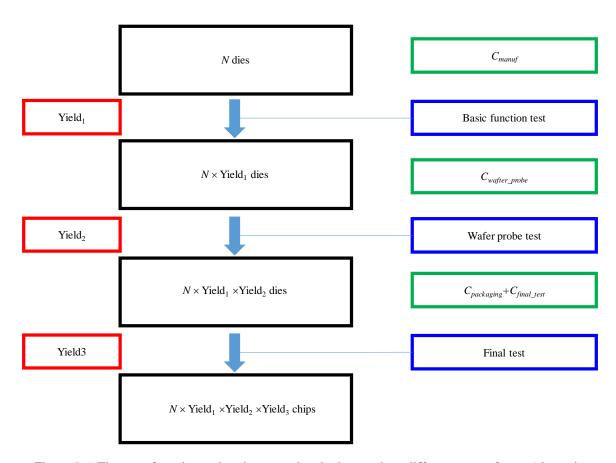

| Figure 5-6. The manufacturing and testing procedure is shown where different types of costs (shown in     |

| green box) are applied on different number of dies/chips (shown in black box) due to the chip             |

| drop after each test (shown in blue box)                                                                  |

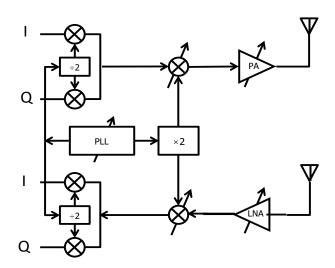

| Figure 5-7. A mmWave transceiver schematic is shown                                                       |

# **List of Tables**

| Table 2-1. Performance modeling error and cost for LNA                                | 42  |

|---------------------------------------------------------------------------------------|-----|

| Table 2-2. Performance modeling error and cost for down-conversion mixer              | 43  |

| Table 2-3. Confidence interval comparison between proposed and traditional approaches | 49  |

| Table 2-4. Confidence interval comparison between proposed and traditional approaches | 51  |

| Table 3-1. Frequencies and corresponding phase noise specifications                   | 70  |

| Table 3-2. PoMs and measurement sensors                                               | 70  |

| Table 3-3. PoI and PoMs of indirect phase noise sensor                                | 70  |

| Table 3-4. Basis functions selected for indirect phase noise sensor                   | 71  |

| Table 3-5. Parametric yield of the wafer by using a fixed bias voltage                | 71  |

| Table 3-6. Measurement cost and parametric yield by self-healing                      | 72  |

| Table 4-1. Side information for performance modeling of LNA                           | 91  |

| Table 4-2. Performance modeling error and cost for LNA                                | 92  |

| Table 4-3. Indirect sensor modeling cost of OLS and CL-BMF (normalized)               | 95  |

| Table 5-1. mmWave ATE parameters                                                      | 104 |

| Table 5-2. Manufacturing cost and packaging cost comparison of Traditional, AT and OH | 106 |

| Table 5-3. Parametric yield of circuit design based on Traditional, AT and OH.        | 106 |

## Chapter 1

## Introduction

In 1965, Gordon E. Moore made the projection that the number of transistors in a dense integrated circuit (IC) doubles approximately every two years, which is later known as Moore's law [1]. Moore's law proved accurate for several decades, and is used in the semiconductor industry to guide long-term planning. Behind Moore's law, reduced cost and improved performances are the main driving factors for continuous IC scaling.

In past few decades, numerous technology breakthroughs in IC technology contribute to sustain Moore's law including chemically-amplified photoresist [2], deep UV excimer laser photolithography [3], chemical mechanical planarization [4]. New technology nodes enabling smaller transistor feature size continuously being developed. Larger and larger circuit functions with superior performances are manufactured on a single semiconductor substrate. However in 2012, when technology node reaches 22nm, the growth rate began to decrease [5]. The key limiting factor is the yield loss, which is defined as the proportion of the number of fabricated chips that fail to meet performance specifications [6]. The yield loss directly degrades the profitability of the IC manufacturing, and thus must be properly handled in all stages of technology node development.

Process variations in analog/RF circuit is an important factor that causes yield loss [6]-[7]. Process variations, including inter-die variations and local mismatches, manifest themselves as the uncertainties associated with the geometrical and electrical parameters of semiconductor devices. Designing analog/RF circuit becomes increasingly challenging in advanced technology nodes. With the deep submicron IC technology scaling, the device-level process variations have become larger and larger, which are not easily mitigated by foundries. This lays a fundamental challenge on robust design techniques for analog/RF circuits.

However, traditional robust design techniques [8]-[32] are not sufficient to maintain high parametric yield with process variations. In this context, on-chip self-healing methodology has been proposed [41]-[53]. In self-healing circuit, tuning knobs (e.g. tunable current source) are employed which allow performance (e.g. voltage gain, power, etc.) flexibility. The key idea of on-chip self-healing is to actively measure and adaptively tune circuit performances in post-silicon on-chip. As such, for each manufactured chip, the knob configurations can be tuned to optimize the circuit performance for its particular process corner. The parametric yield of circuit can therefore be significantly improved.

The design flow of self-healing analog/RF IC will be discussed in detail in Section 1.2.2. Pre-silicon validation and post-silicon tuning are two important tasks in the design flow. In pre-silicon, the self-healing circuit design must be verified by parametric yield analysis before moving to the manufacturing process. Once the circuit is manufactured, post-silicon tuning is required to exploit the benefit of configurability and improve the parametric yield. The main challenge for both pre-silicon validation and post-silicon tuning is how to maintain low overhead in computation, hardware and testing cost so that self-healing methodology can be practically implemented.

In this thesis, we develop efficient pre-silicon validation and post-silicon tuning techniques for self-healing analog/RF IC. The core task of pre-silicon validation is the parametric yield estimation. We propose an efficient parametric yield estimation algorithm based on correlated performance modeling which considers the correlation among tuning knob configurations. The post-silicon tuning of self-healing circuit consists of two core tasks: (i) on-chip performance sensing, and (ii) on-chip performance tuning. In on-chip performance sensing, circuit performances are actively measured by on-chip sensors. Then in on-chip performance tuning, a set of on-chip tuning knobs (e.g. bias current) are adaptively adjusted in order to satisfy all performance specifications. While the on-chip performance tuning is also an important topic, we restrict our discussion to on-chip performance sensing in this thesis. We develop a novel indirect performance sensing technique to facilitate inexpensive-yet-accurate on-chip performance sensing. In the rest of this chapter, we will briefly review the background on traditional robust design techniques, on-chip self-healing methodology, pre-silicon validation of self-healing circuit, and post-silicon tuning of self-healing circuit, and then outline the overall structure of the thesis.

## 1.1 Traditional Robust Design Techniques

Traditionally, various design techniques have been proposed to handle the performance uncertainty of analog/RF IC. The traditional design techniques can be classified into two broad categories: (i) corner-based design optimization [8]-[24], and (ii) statistical design optimization [25]-[32].

In corner-based design optimization [8]-[24], the circuit is optimized at all process corners by combining the extreme values of all process parameters. However, the corner-based approach has two major issues. First, the performance corner in an analog circuit does not necessarily to be the process parameter corner. In other words, the extreme performance value may not occur when all process parameters reach extreme values. In fact, the actual performance corner is topology dependent and performance dependent [7]. Second, the total number of the combinations of the process corners exponentially grow with the number of process parameters. In an advanced technology node, the total number of process parameters can easily reach 1000. In such case, the total number of corner combinations will become astronomical, and the corner-based approach would be impractical.

In statistical design optimization [25]-[36], the statistical distribution of the circuit performance is first analyzed. Then the circuit design is optimized such that an only sufficient and necessary margin is chosen. As such, the design is robust with respect to process variations, and meanwhile the over-design is minimized. Statistical design optimization has three categories: (i) direct yield estimation [25]-[28], (ii) design centering [29]-[32], and (iii) worst-case optimization [33]-[36]. The direct yield estimation approach [25]-[28] essentially traverses the design space and estimate parametric yield associated with each design point. The yield is usually estimated by transistor-level Monte Carlo simulations. Eventually the design point with the maximum yield is selected. However, since the simulation based yield estimation can be very expensive, the direct yield estimation based design optimization is not very efficient. The design centering approach [29]-[32] is based on the geometrical insight in the parameter space, which aims to find the optimal design point that has the maximum distance from all boundaries posed by performance constraints. In design centering approach, the robustness of the circuit is measured by the volume of the ellipsoid that maximally inscribed or minimally circumscribed the boundaries. However, since design-centering does not directly optimize parametric yield, the optimized design point might not provide the maximum yield.

The worst-case optimization approach [33]-[36] achieves robust circuit design by optimizing the worst case circuit performances considering process variations. The worse-cast performance values can be defined as a particular percentile point (e.g. 99%) of the performance cumulative distribution function. However, worst-case optimization has the limitation that it could only guarantee good optimized design with a single performance. In the case of multiple performance specifications, it will ignore the performance correlation and thus cannot provide an accurate yield estimation, rendering sub-optimal design point.

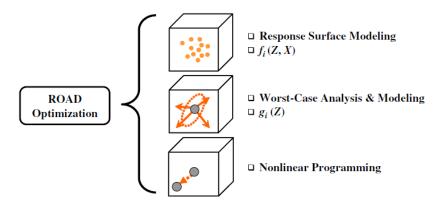

In this context, the robust analog/digital optimization algorithm (ROAD) has been proposed [35]-[36]. ROAD approach is consisted of one initialization step and three core steps. In the initialization step, a coarse initial design is found by performance centering algorithm [37]. Then, a number of transistor-level simulations are run and the performance model in terms of both design variable and process parameters is fitted. After this, worst-case performance is analyzed and the worst-case performance model is fitted in terms of design variables. Such worst-case performance model is then used to optimize circuit performance via nonlinear programming.

Figure 1-1. Robust analog/digital optimization algorithm flow [7].

With the scaling of IC technology, robust circuit design has become more and more challenging, if not impossible. The reasons are two-folds here. On one hand, process variations have become larger and larger with the transistors continuously scaling to deep submicron. On the other hand, more and more aggressive specifications on speed, power and area are set to accommodate costumer demands. For example, with the world quickly moving into the Internet of Things (IoT) era, ultra-high speed

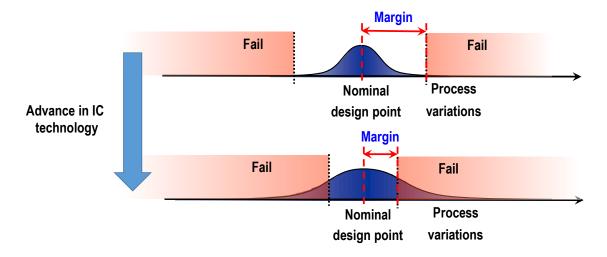

communication circuits with low power consumption are required [38]-[40]. In this context, robust circuit design becomes extremely difficult. Figure 1-2 illustrates the challenge. The advance in IC technology makes the performance distribution becoming increasingly scattered. As such, the performance specification keeps pushing to squeeze the feasible design region. Even if the optimal robust design point can be found, the trend of the parametric yield decrease is inevitable for the traditional design methodology. To address this fundamental challenge, on-chip self-healing methodology has been proposed, which will be explained in Section 1.2 in detail.

Figure 1-2. Challenges of robust circuit design is shown. With the scaling of IC technology, on one hand the process variations become larger, while on the other hand the circuit specifications become more aggressive. As a result, the design margin dramatically shrinks.

### 1.2 On-Chip Self-Healing Methodology

On-chip self-healing methodology [41]-[46], [49]-[53], [58]-[60] has emerged as a promising avenue to address the aforementioned challenges. In self-healing circuit, tuning knobs (e.g. tunable current source) are employed which allow performance (e.g. voltage gain, power, etc.) flexibility. The key idea of on-chip self-healing is to actively measure and adaptively tune circuit performances in post-silicon on-chip. Compared to the post-manufacturing calibration work in [54]-[57], on-chip self-healing provides more flexibility. The performance tuning of on-chip self-healing is not restricted to be in the testing site, but can

be done anywhere. This provides additional tuning capacity when the environmental condition and/or the circuit condition changes in field.

In this sub-section, we provide an overview of on-chip self-healing methodology. In Section 1.2.1, we introduce essential components of self-healing circuit. In Section 1.2.2, we discuss the design flow of self-healing circuits.

#### 1.2.1 Components of On-Chip Self-Healing

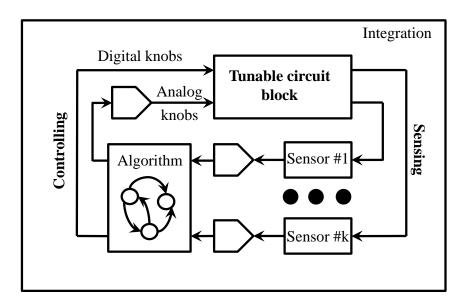

Figure 1-3. Three core components of on-chip self-healing are shown: tunable circuit block, sensing circuit and controlling circuit. The three components are seamlessly integrated on-chip to achieve self-healing.

Figure 1-3 shows three core components of the on-chip self-healing circuit [51], which need be seamlessly integrated on-chip:

employed on-chip to allow flexibility in circuit performances (e.g. noise figure, gain, nonlinearity, etc.). The tunable circuit block can either be a single circuit component (e.g. low-noise amplifier) or a system consisted of multiple circuit components (e.g. the receiver path in a RF transceiver). The tunable circuit block serves as the main body of the self-healing circuit and usually consumes the major portion of area. The control knobs need to be carefully designed in the tunable circuit such that the tuning ranges of the circuit performances of interest are large enough to cover the process and

environmental condition variations. Different from traditional circuit block without control knobs, the tunable circuit block possesses multiple 'states' enabled by control knobs. Therefore, tunable circuit block has the potential of adaptively selecting the optimal state that suits best to a particular process corner or environmental condition. Such potential will be realized through the integration with sensing and controlling circuitry.

- Sensing circuit: Sensing circuit (e.g. voltage sensor, temperature sensor, frequency counter, etc.) is the circuit component that is able to capture the performance metrics of tunable circuit block. The design of sensing circuit is an important task in the self-healing design. The accuracy-cost trade-off must be carefully analyzed and optimized in order to achieve accurate performance sensing while not causing large over-head. For example, it is not reasonable to always design high accuracy sensing circuit, because they usually consume large circuit area and the yield impact may not high.

- Controlling circuit: Controlling circuit is a decision-making circuit component that obtains tunable circuit performance information from sensing circuit and optimally determines the tuning knob configuration for tunable circuit block. In our work, controlling circuit is consisted of microcontroller, I/O, SRAM [51]-[53]. The self-healing algorithm (e.g. exhaustive search) can be loaded in the controlling circuit and the self-healing operation procedure is performed exactly as directed by the self-healing algorithm. The self-healing algorithm can either be a component-level algorithm focusing on the healing of a particular circuit component (e.g. LNA) or a system-level algorithm targeting at system-level performance metrics (e.g. noise figure of a receiver path).

The eventual goal of the on-chip self-healing is to actively sense important circuit performances and adaptively tune the knob configurations in order to improve overall circuit performance (e.g. improving parametric yield, reducing power consumption, etc.).

### 1.2.2 Design Flow of On-Chip Self-Healing

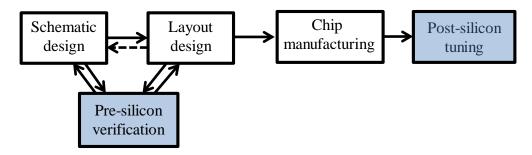

Similar to traditional circuit without tuning knobs, self-healing circuit design also needs to go through several important design stages. The design flow of self-healing circuit is summarized in Figure 1-4. The flow spans four stages: (i) schematic design, (ii) layout design, (iii) chip manufacturing, and (iv) post-silicon tuning and testing. At each stage, simulation or measurement data are collected to tune and/or

validate the self-healing system in Figure 1-3.

The design starts from the schematic design where the topology, transistor sizing and other important design parameters are selected. Then the parasitics, routing and transistor placement are considered in the layout design. If the design fails to meet the performance specifications at any of the presilicon stage, the circuit design will be improved until the specifications are met. Once the design is fully verified in the pre-silicon stage, the chip will be manufactured. The post-silicon tuning is then done to improve the circuit performances in order to increase parametric yield or reduce power consumption. The post-silicon tuning involves close interaction between tunable circuit block, sensing, controlling circuitry, as well as the automatic testing equipment (ATE).

Figure 1-4. Design flow of self-healing circuit is shown, which is consisted of four stages: (i) schematic design, (ii) layout design, and (iii) chip manufacturing, and (iv) post-silicon tuning.

To reduce the overall cost per good chip, efficient analysis, design, validation and tuning methodology are required. In this thesis, we focus on three important problems related to self-healing circuit: pre-silicon validation, post-silicon tuning (as shown in the highlighted blocks in Figure 1-4) and cost analysis.

### 1.3 Pre-Silicon Validation of Self-Healing Circuit

In this section, we review the background of the pre-silicon validation of self-healing circuit. The goal of the pre-silicon validation is to verify the parametric yield considering the self-healing effect in pre-silicon. Parametric yield estimation is a fundamental task for analog/RF circuit and has been extensively studied in the literature [61]-[67]. The traditional parametric yield estimation can be classified into four broad categories: (i) Monte Carlo based approach [61]-[63], (ii) statistical blockade [64]-[66], (iii)

Bayesian inference based approach [67], and (iv) performance model based approach [68]-[69],

The Monte Carlo based approach is to repeatedly draw random samples from process parameter distributions and evaluate circuit performance of interest by circuit simulations (e.g. transistor-level simulations in Cadence). In the direct Monte Carlo approach [61], the pre-silicon parametric yield is estimated by calculating the portion of the number of simulated instances that pass all performance specifications  $N_{pass}$  out of the total number of simulated instances  $N_{total}$ :

$$Yield = \frac{N_{pass}}{N_{total}}. (1.1)$$

Direct Monte Carlo approach is easy to implement and is not dependent on the dimensionality of the process parameters, because it directly operates in the performance space. However, the well-known limitation of the Monte Carlo approach is that it is very time consuming, since no structural insight is used. The Quasi-Monte Carlo method [63] is an extension of direct Monte Carlo. The key idea is to assign a sequence of deterministic Monte Carlo samples in parameter space to improve the convergence rate. This approach aims to uniformly sample the whole parameter space, which is able to better capture the low probability region and thus yield more efficient estimation. The Quasi-Monte Carlo approach is efficient when the parameter space is low-dimensional. However, as a trade-off, it suffers from the curse of dimensionality because it relies on the parameter space. The accuracy of Quasi-Monte Carlo can be even worse than direct Monte Carlo in high-dimensionality case. For self-healing circuits in advanced technology node, since the number of process parameters is high and a large number of knob configurations need to be simulated, the simulation cost of Monte Carlo approach would be very high. Therefore, Monte-Carlo approach is not suitable for pre-silicon validation task of self-healing circuit.

Statistical blockade [64]-[66] is proposed based on the observation that some Monte Carlo samples are not likely to fail, therefore simulating them would have very limited benefit. In particular, a classifier is constructed to block the Monte Carlo samples that are deemed to pass or fail. As such, the whole parameter space is classified into two types of regions. One region contains the parameter values that we are certain about the outcome of the simulation (i.e. pass or fail in performance specifications), which are blocked out from running simulations. The other region contains parameter values whose simulation outcomes are not clear. By simulation the second region, the outcomes of uncertain points are determined and classifier can

be further refined. The main strength of statistical blockade is its efficiency in low failure rate application. In such application, the majority of samples would pass the specifications, therefore avoid simulating those points can provide significant efficiency improvement over Monte Carlo approach. However, in analog/RF circuit, the failure rate is usually not as low as the rare failure rate application, due to the over-design consideration. Furthermore, since statistical blockade operates in the parameter space, the dimensionality problem would affect its effectiveness. In advanced technology nodes, the number of process parameters are usually high (e.g. above 1000), and the cost of training and refining the classifier can be very expensive. As a result, the benefit of applying statistical blockade on self-healing analog/RF circuit is very limited.

In light of the correlation between design stages, a Bayesian inference based approach [67] is proposed. The key observation that motivates the approach is that the performance probability distribution can be very similar in different design stages. For example, the performance cumulative distribution function (CDF) of the read path delay of SRAM in the schematic stage can be very similar to the CDF in post-layout stage. Such correlation can be explored among any stages in the design flow where the two stages follow a sequential order. The stage that appears earlier in the design flow is considered as the early stage while the stage appears later is considered as late stage. Mathematically, a Bayesian inference approach is proposed which encodes the early stage information into a prior distribution. The prior distribution is then combined with very few samples collected in the late stage (either by simulation or silicon measurements) through Bayesian inference [61]. The Bayesian inference would provide a posterior distribution that can be translated into the performance distribution in the late stage. Although Bayesian inference based approach is promising, it relies on the existence and accuracy of the early-stage model. In the case where an early-stage performance distribution does not exist or not reliable, the parametric yield estimation can be very expensive.

The performance modeling based approach [68]-[69] is consisted of two steps. First, performance model is constructed based on a number of simulation samples of the circuit. Performance model is a statistical model where circuit-level performance (e.g. phase noise) is approximated as an analytical function (e.g. polynomial) of device-level variations (e.g.  $\Delta V_{TH}$ ). As such, the circuit-level performance variations are linked to the process parameters variations. Next, based on the performance model, the probability distribution is predicted. Since the performance model usually has a special form (e.g. linear or

quadratic polynomials), the associated probability distribution is also structured. The statistical parameters (e.g. mean, variance, or high-order moments) can then be efficiently determined from performance model and the parametric yield can be estimated.

One key observation about the self-healing circuit is that the performances associated with different states are highly structured. In other words, the underlying statistical link between process parameters and circuit performances among different states are highly correlated. The performance modeling approach directly build model based on process parameters and therefore has the potential to captures such structure.

Performance modeling is the task to find model coefficients associated with performance model. It serves as a core component in the modeling, analyzing and optimization throughout the analog/RF circuit design flow. The performance modeling techniques have been extensively studied in the literature [70]-[79]. The state-of-the-art performance modeling technique is the sparse regression [74]-[80]. Sparse regression approach is motivated by the observation that only a small number of process variables contributes to the performance variation. Based on this assumption, sparse regression aims to find a small number of important basis functions and simply the model template. As such, only a small number of model coefficients that relates to important basis functions need to be solved. The modeling efficiency can be significantly improved by using sparse regression.

For self-healing circuit, this fundamental modeling problem can be extremely difficult with the following characteristics:

- High-dimensional variation space: A large number of device-level random variables must be used to model the process variations associated with a self-healing analog/RF system at advanced technology nodes. For example, a self-healing low-noise amplifier designed in a commercial 32nm process carries over 1000 device-level random variables.

- Large number of knob configurations: To maximize tuning range and resolution, a large number of

knob configurations (i.e. 'states') should be designed. This, however, significantly increases the

complexity of performance modeling, since a unique performance model is required to accurately

capture the variability at each state.

- Correlated knob configurations: Since different states are associated with the same self-healing circuit,

the performance models of the different states are correlated. In particular, the model template and

model coefficients are expected to be similar among these states.

It is important to note that most traditional approaches [74]-[80] are not fully equipped for performance modeling of self-healing circuits. Taking sparse regression [74]-[77] as an example, the sparsity of model coefficients is explored to improve efficiency. However, no correlation is considered between different states. In other words, performance modeling is done for each state independently and the performance modeling cost would quickly become intractable as the number of states increases. Several other performance modeling methods (e.g., simultaneous orthogonal matching pursuit [78], multi-mode multi-corner sparse regression [79], group lasso [80], etc.) have been proposed to exploit the aforementioned correlation information. However, these methods only take into account the shared model template among different states and they ignore the correlation of coefficient magnitude. In this regard, there is a strong need to develop an efficient performance modeling approach, which serves as a starting point of pre-silicon validation.

#### 1.4 Post-Silicon Tuning of Self-Healing Circuit

Post-silicon tuning is another important step in the self-healing circuit design flow. The goal of post-silicon tuning is to find the optimal tuning knob configuration that gives desired circuit performances. Two important tasks need to be achieved to enable post-silicon tuning through on-chip self-healing: (i) on-chip performance sensing, and (ii) on-chip performance tuning. While the on-chip performance tuning is also an important topic [81]-[82], we restrict our discussion to on-chip performance sensing in this thesis.

To practically implement on-chip performance sensing, a large number of performance metrics must be measured accurately and inexpensively by on-chip sensors. Such a measurement task is not trivial because many analog and RF performance metrics (e.g. phase noise) cannot be easily measured by on-chip sensors [41]-[42]. For this reason, alternate test methodology, also called indirect performance sensing, has recently attracted great attention [43], [47], [50]-[51], where performance of interest (PoI) is not directly measured by an on-chip sensor. Instead, it is accurately predicted from a set of other performance metrics, referred to as the performance of measurement (PoMs) that are highly correlated with PoI and are easy to measure. Towards this goal, indirect sensor modeling is a critical task where the objective is to build a mathematical model to capture the correlation between PoI and PoMs so that PoI can be accurately

predicted from PoMs. The indirect sensor models, once trained, can be stored on an on-chip microcontroller and direct the control knob tuning in the controlling phase.

To provide a fully on-chip indirect performance sensing solution with low overhead, two important challenges must be addressed:

- High cost in on-chip hardware: The storage, computation and sensor inputs of indirect sensor models all require on-chip hardware resources. A complex model with many PoMs and model coefficients, though accurate, consumes massive hardware resources and thus introduce large overhead in self-healing [51].

- High cost in repeated calibration: Due to the process shift associated with manufacturing lines, the indirect sensor models must be repeatedly calibrated from time to time. During each calibration, PoMs and PoI need to be measured from a set of training chips, and then used for model regression. Such calibration procedure can lead to large overhead in self-healing if done inefficiently.

The aforementioned two challenges pose a strong need of developing an efficient on-chip indirect performance sensing methodology.

It should be noted that neural network [61] has been adopted as indirect sensor model in the on-chip self-healing work in [58]-[60]. Compared to the polynomial indirect sensor model in the proposed methodology, neural network model is able to achieve higher prediction accuracy when the polynomial model is insufficient to capture the performance variability. However, neural network consumes huge on-chip resources [58]-[60] and therefore has larger overhead than the proposed methodology. Such overhead can be a critical concern in the applications with limited on-chip resources (e.g. spy transmitter).

#### 1.5 Cost Analysis

The design methodology of analog/RF circuits can be classified into three categories: (i) traditional design without tuning capacity (Traditional) [8]-[32], (ii) off-chip adaptive performance tuning (AT) [47]-[48], and (iii) on-chip self-healing (OH) [41]-[46], [49]-[53]. The Traditional method does not include tunable control knobs in the circuit design. For both AT and OH, tunable control knobs are designed to improve parametric yield. The performance calibration in AT is done off-chip, which relies on ATE measurements for all knob configurations. On the other hand, the performance calibration of OH is done

on-chip, which relies on microcontroller loaded with indirect sensor model. Although the three design methods have been proposed for many years, their trade-off has not been extensively studied in the literature. It is important for circuit designs to understand the critical cost factors when selecting an optimal design method. Toward this goal, we perform a cost analysis for Traditional, AT and OH. In this thesis, we limit the application to the mmWave transceiver product.

Cost per good chip is an important criterion that measures the profitability of product [99]. The cost per good chip essentially quantifies the overall capital investment in the manufacturing, testing and packaging cost throughout the good chip generation process. The manufacturing cost is the cost of fabricating a particular chip. It includes the material, equipment, maintenance, consumables and utilities cost during the manufacturing process. In this thesis for comparison purpose, we assume that given a particular manufacturing process (e.g. 32nm), the manufacturing cost per good chip is proportional to the die area of the circuit. In other words, if the circuit design has larger area, the manufacturing cost would be higher. In this regard, the OH approach would have the highest manufacturing cost among the three approaches, due to the overhead in controlling and sensing circuit. The Traditional approach, on the other hand, has the lowest manufacturing cost because it does not have either controlling or sensing circuit. In this thesis, we further assume that the packaging cost is approximately the same as the manufacturing cost [98].

The testing cost includes the cost of performing post-silicon performance tuning as well as validating the pass/fail of a particular die [91]-[99]. To combat the variability issue, tuning knobs are employed in the circuit blocks to allow flexibility. Once the circuits are manufactured, the control knobs must be adaptively tuned to maximally exploit the benefit of configurability. This procedure can be done either off-chip (i.e. AT) or on-chip (i.e. SH). AT essentially measure the performances for all knob configurations directly using ATE, while SH measure a small number of performances to fit an indirect sensor model and then tune the knob configurations using microcontroller on chip. Once the knob configuration is selected for each chip, AT and OH can be treated similarly as Traditional. In particular, the circuit performances are first verified through wafer probe test. Then the die is packaged and the final specification test is done for the packaged chips. It should be noted that for mmWave product, the packaging cost is very high, therefore there is a strong need to test the circuit in wafer probe level before

packaging. Given that ATE with mmWave measurement capability is usually very expensive, the testing cost is directly proportional to the total testing time using ATE. The Traditional approach would have smallest testing time, because it does not require any performance tuning. The AT approach, on the other hand, has the largest testing time, because all knob configurations need to be tested.

Compared to the Traditional approach, OH is able to achieve better parametric yield. However, the hardware cost overhead and testing cost overhead will be high. Compared to AT, OH will achieve lower parametric yield due to limited accuracy in on-chip performance sensors. However, the testing cost, especially the performance tuning cost, will be lower. Therefore, it is not clear which approach would provide lowest cost per good chip. In this regard, there is a strong need to perform a cost analysis considering important cost factors for Traditional, AT and OH approaches.

#### 1.6 Thesis Contributions

In this thesis, we propose an efficient pre-silicon validation flow, efficient post-silicon tuning flow and a cost analysis for on-chip self-healing. The major technical contributions of this thesis are:

We propose an efficient pre-silicon validation flow via performance modeling. In particular, we propose to build performance model of self-healing circuits based on Correlated Bayesian Model Fusion (C-BMF) algorithm. The proposed C-BMF method is motived by the fact that performance models associated with different states are correlated. Our key idea is to encode the correlation information for both model template and coefficient magnitude among different states by using a unified prior distribution. The prior distribution is then combined with a few simulation samples via Bayesian inference to efficiently determine the unknown model coefficients. Furthermore, we propose efficient and robust hyper-parameter inference technique to solve a large number of hyper-parameters involved in C-BMF. It consists of two major steps: (i) estimating the hyper-parameters to obtain an initial guess using a heuristic approach, and (ii) optimizing the hyper-parameter values using an expectation-maximization algorithm [61]. The performance model coefficients can then be determined based on the inferred hyper-parameters. Moreover, an efficient pre-silicon validation approach is proposed where the correlated performance modeling algorithm serves as a core component. Instead of simulating all the knob configurations from all chips, we generate pseudo samples based on

performance model. As such, the parametric yield estimation cost can be significantly reduced.

- We propose an efficient post-silicon tuning flow via indirect performance sensing. In particular, we propose a Bayesian Model Fusion (BMF) based indirect sensor model calibration technique. The key idea of BMF is to combine the old (i.e., before process shift) indirect sensor model with very few new (i.e., after process shift) measurement data to generate a new model that is aligned with the new process condition. Mathematically, the old model is encoded as prior knowledge, and a Bayesian inference is derived to optimally fit the new model by maximum-a-posteriori (MAP) estimation. As such, the indirect sensor model can be efficiently calibrated. As an extension of BMF, we further propose a novel indirect sensor modeling algorithm that is referred to as Co-Learning Bayesian Model Fusion (CL-BMF). CL-BMF takes advantage of the additional information collected from measurements to reduce the performance modeling cost. Different from the BMF which focus on the prior information of model coefficients (i.e. the coefficient side information) only, CL-BMF takes advantage of another new form of prior knowledge: the performance side information (PSI). In particular, CL-BMF combines the coefficient side information (CSI), the PSI and a small number of training samples through Bayesian inference based on a graphical model. Furthermore, a PSI selection technique is proposed to select most important performances to provide PSI. As a result, the indirect sensor model calibration cost can be further reduced.

- Due to the overhead involved in the on-chip self-healing, it is not clear to circuit designers whether the on-chip self-healing would really benefit the final cost of product. In this regard, we present a cost analysis on a mmWave self-healing transceiver to compare three different circuit designs methodologies: (i) traditional circuit design without tunable component, (ii) tunable circuit with off-chip performance calibration, and (iii) on-chip self-healing circuit. The cost per good chip is calculated which quantifies the overall capital investment in the manufacturing, testing and packaging cost throughout the good chip generation process for each design approach. The cost analysis can provide a guideline to circuit designer on whether or not to apply on-chip self-healing for a particular application.

It is important to note that the proposed C-BMF, BMF and CL-BMF algorithms are derived from rigorous statistical theory, and can be generally applied to other applications such as fast statistical analysis of rare failure events [62], probability distribution estimation [67], etc.

#### 1.7 Thesis Organization

In this section, we briefly summarize the thesis organization. The thesis is composed of three core components: efficient pre-silicon validation, efficient post-silicon tuning and cost analysis.

In Chapter 2, we first develop a Correlated Bayesian Model Fusion (C-BMF) algorithm to efficient fit performance model for self-healing circuit via Bayesian inference. In the Bayesian inference, a large number of hyper-parameters need to be determined. Towards this goal, we further propose an efficient and robust hyper-parameter inference approach, which consists of two major steps: (i) estimating the hyper-parameters to obtain an initial guess using a heuristic approach, and (ii) optimizing the hyper-parameter values using an expectation-maximization algorithm. The proposed performance modeling approach is validated in two circuit examples designed in a commercial 32nm CMOS process. We further present the parametric yield estimation flow for self-healing circuit based on performance model. Instead of simulating all the knob configurations from all chips, we generate pseudo samples using performance model of self-healing circuit. As such, the parametric yield estimation cost can be significantly reduced. The efficacy of the proposed parametric yield estimation algorithm is validated by simulation data collected from two circuit examples designed in a commercial 32nm CMOS process.

In Chapter 3, we address the problem of efficient post-silicon tuning. Towards this goal, we propose a novel indirect performance sensing technique for on-chip self-healing of analog and RF circuits. In particular, we propose to use sparse regression to identify a set of important basis functions so that the overhead of on-chip self-healing can be minimized. We further propose an efficient indirect sensor model calibration approach based on Bayesian Model Fusion (BMF). In BMF algorithm, we encode the early stage information in the prior distribution. The prior distribution is then combined with a few samples in the late stage via Bayesian inference. As a result, the indirect sensor model can be updated with low cost. Experiments on silicon measurement data demonstrate that the efficacy of the proposed indirect performance sensing

The BMF algorithm essentially takes advantage of the side information of model coefficients (i.e. CSI) to facilitate the efficient indirect sensor model calibration. In Chapter 4, we extend BMF algorithm to further consider another type of side information: the PSI. CL-BMF optimally combines the following

information: (i) the CSI, (ii) the PSI, and (iii) a small number of training samples. Bayesian inference is constructed and represented as a graphical model, where the CSI and the PSI are encoded by the prior distribution and the likelihood function respectively. From the Bayesian inference, the unknown model coefficients can be accurately determined by maximizing the posterior distribution. Furthermore, a PSI selection technique is also proposed to select most important performances to provide PSI. As is demonstrated by our circuit examples designed in a commercial 32nm SOI CMOS process, the proposed CL-BMF method achieves significant cost reduction over other indirect sensor modeling techniques.

In Chapter 5, we present a cost analysis on a mmWave self-healing transceiver. The manufacturing cost, testing cost and packaging cost are taken into consideration to analyze the cost per good chip. In this cost analysis, three different circuit design methodologies are compared: (i) traditional circuit design without tunable component, (ii) tunable circuit with off-chip performance calibration, and (iii) proposed on-chip self-healing circuit. Based on our cost analysis for this particular example, the cost per good chip of self-healing circuit is significantly less than the other two circuit design methods.

Chapter 6 concludes the thesis with a high-level summary of the work, and discusses several future potential directions of research related to this work.

## **Chapter 2**

### **Efficient Pre-Silicon Validation via Performance**

## **Modeling**

#### 2.1 Motivation

One key observation about the self-healing analog/RF IC is that the performances associated with different states (i.e. knob configurations) are highly structured. In other words, the underlying statistical link between process parameters and circuit performances among different states are highly correlated. The performance modeling approach directly build model based on process parameters and therefore has the potential to captures such structure. In this regard, we propose the pre-silicon validation approach that is consisted of two steps: (i) performance modeling of self-healing circuits, and (ii) parametric yield estimation based on performance model. In the proposed flow, the main challenge is the performance modeling step. Once the performance model is obtained, the parametric yield can be estimated straightforwardly. Furthermore, the performance model, once obtained, can be applied to other important applications for self-healing circuit such as corner extraction [84] and design optimization [25]-[36].

To start with, we mathematically formulate the performance modeling problem for self-healing circuits. Given a self-healing analog/RF circuit (e.g. a down-conversion mixer) with totally K states (i.e. knob configurations), the performance model of the k-th state can be represented by an analytical function (e.g., polynomial) of device-level variations (e.g.,  $\Delta V_{TH}$ ):

$$y_k \approx f_k(\mathbf{x}) = \sum_{m=1}^{M} \alpha_{k,m} \cdot b_m(\mathbf{x}) \quad (k = 1, 2, \dots, K)$$

(2.1)

where  $\{y_k; k = 1, 2, \dots, K\}$  contains the performance of interest (PoIs) associated with the K states,  $\mathbf{x}$  is a vector representing the device-level variations,  $f_k(\mathbf{x})$  denotes the performance model of interest which

establishes a mapping from  $\mathbf{x}$  to  $y_k$ ,  $\{\alpha_{k,m}; m = 1, 2, ..., M\}$  contains the model coefficients of  $f_k(\mathbf{x})$ ,  $\{b_m(\mathbf{x}); m = 1, 2, ..., M\}$  contains the basis functions (e.g., linear or quadratic polynomials), and M denotes the total number of basis functions. Without loss of generality, we assume that the same set of basis functions  $\{b_m(\mathbf{x}); m = 1, 2, ..., M\}$  are shared among all the states.

In order to determine the performance models in (1), we need to find the model coefficients  $\{\alpha_{k,m}; k = 1, 2, ..., K; m = 1, 2, ..., M\}$ . Towards this goal, the traditional least-squares fitting method first collects a number of sampling points of  $\mathbf{x}$  and  $\{y_k; k = 1, 2, ..., K\}$  for all K states, and then solves the model coefficients from the following optimization problems:

$$\min_{\boldsymbol{\alpha}_{k}} \quad \left\| \mathbf{y}_{k} - \mathbf{B}_{k} \cdot \boldsymbol{\alpha}_{k} \right\|_{2}^{2} \quad \left( k = 1, 2, \dots, K \right)$$

(2.2)

where

$$\mathbf{B}_{k} = \begin{bmatrix} b_{1}\left(\mathbf{x}_{k}^{(1)}\right) & b_{2}\left(\mathbf{x}_{k}^{(1)}\right) & \cdots & b_{M}\left(\mathbf{x}_{k}^{(1)}\right) \\ b_{1}\left(\mathbf{x}_{k}^{(2)}\right) & b_{2}\left(\mathbf{x}_{k}^{(2)}\right) & \cdots & b_{M}\left(\mathbf{x}_{k}^{(2)}\right) \\ \vdots & \vdots & \vdots & \vdots \\ b_{1}\left(\mathbf{x}_{k}^{(N)}\right) & b_{2}\left(\mathbf{x}_{k}^{(N)}\right) & \cdots & b_{M}\left(\mathbf{x}_{k}^{(N)}\right) \end{bmatrix} \quad (k = 1, 2, \dots, K)$$

$$(2.3)$$

$$\boldsymbol{\alpha}_{k} = \begin{bmatrix} \alpha_{k,1} & \alpha_{k,2} & \cdots & \alpha_{k,M} \end{bmatrix}^{T} \quad (k = 1, 2, \dots, K)$$

(2.4)

$$\mathbf{y}_{k} = \begin{bmatrix} y_{k}^{(1)} & y_{k}^{(2)} & \cdots & y_{k}^{(N)} \end{bmatrix}^{T} \quad (k = 1, 2, \dots, K).$$

(2.5)

In (2.3)-(2.5),  $\mathbf{x}_k^{(n)}$  is the value of  $\mathbf{x}$  at the *n*-th sampling point of the *k*-th state,  $y_k^{(n)}$  is the value of  $y_k$  at the *n*-th sampling point,  $\|\bullet\|_2$  stands for the L<sub>2</sub>-norm of a vector, and *N* represents the total number of sampling points collected for each state. Here we assume that the same number of samples is collected for each state, since we consider all states to be equally important. To avoid over-fitting, the number of sampling points (i.e., *N*) must be substantially greater than the number of unknown coefficients (i.e., *M*).

To reduce the number of samples required for performance modeling, the simultaneous orthogonal matching pursuit (S-OMP) algorithm [78] has been proposed in the literature. The key idea of S-OMP is to explore the sparse property and the correlation of model template between different states. As an extension of the orthogonal matching pursuit (OMP) algorithm [75], S-OMP naturally inherits the assumption of sparse regression. In other words, S-OMP exploits the fact that only a small number of basis functions in  $\{b_m(\mathbf{x}); m = 1, 2, ..., M\}$  are important and, hence, should be used to approximate  $\{y_k; k = 1, 2, ..., K\}$ . More

importantly, S-OMP also explores the correlation of model template among  $\{y_k; k = 1, 2, \dots, K\}$ . In particular, S-OMP assumes that different states possess the same set of important basis functions. This is usually a valid assumption in practice, because different states are associated with the same self-healing circuit.

While S-OMP has been successfully applied to many practical applications (e.g. wafer spatial pattern analysis [78]), it is possible to explore other correlation information between states to further improve the efficiency of performance modeling for self-healing circuits. There is a strong need to develop a novel performance modeling approach that takes advantage of the correlation of coefficient magnitude. Once such performance model is built, the performance variation of self-healing circuits can be efficiently predicted, and thus the parametric yield can be estimated.

### 2.2 Prior Knowledge Definition

To start with, we consider the performance models of K states in a self-healing circuit as defined in (2.1). We rewrite their model coefficients in a concatenated form as:

$$\boldsymbol{\alpha} = \begin{bmatrix} \boldsymbol{\beta}_1^T & \boldsymbol{\beta}_2^T & \cdots & \boldsymbol{\beta}_M^T \end{bmatrix}^T$$

(2.6)

where

$$\boldsymbol{\beta}_{m} = \begin{bmatrix} \alpha_{1,m} & \alpha_{2,m} & \cdots & \alpha_{K,m} \end{bmatrix}^{T} \quad (m = 1, 2 \cdots, M)$$

(2.7)

$\{\alpha_{k,m}; k=1, 2, ..., K; m=1, 2, ..., M\}$  are the model coefficients defined in (2.1), and  $\alpha$  is the combined column vector with size of  $M \cdot K$ . In (2.6), the model coefficients are organized such that the coefficients associated with the m-th basis function are grouped together in  $\beta_m$  (m=1, 2, ..., M). Since the model coefficients in  $\beta_m$  are related to the same basis function, we assume that they are statistically correlated and define their prior distribution as:

$$pdf\left(\boldsymbol{\beta}_{m}\right) \sim N\left(\mathbf{0}, \lambda_{m} \cdot \mathbf{R}_{m}\right) \quad \left(m = 1, 2, \dots, M\right). \tag{2.8}$$

In (2.8),  $\{\lambda_m; m = 1, 2, ..., M\}$  are the hyper-parameters that control the sparsity of the basis functions, and  $\{\mathbf{R}_m; m = 1, 2, ..., M\}$  are the positive definite matrices that quantify the correlation among model coefficients.

Studying (2.8) yields several important observations. First, the sparse property is naturally encoded in  $\{\lambda_m; m=1, 2, ..., M\}$ . To understand this, we consider the m-th basis function where  $\lambda_m$  is zero. In this case, the variance of the zero-mean Gaussian distribution in (2.8) is also zero. As such, the coefficients  $\beta_m$  can only take zero values based on their prior distribution, thereby implying the sparsity of  $\beta_m$ . Second, the correlation of model template is also encoded by the mathematical representation in (2.8). In particular, all the model coefficients in  $\beta_m$  share the same sparse pattern, because their prior distribution is controlled by the same hyper-parameter  $\lambda_m$ . Third, but most importantly, the correlation of coefficient magnitude is also encoded by this prior definition, as long as the covariance metrics  $\{\mathbf{R}_m; m=1, 2, ..., M\}$  are not diagonal. Here we further assume that:

$$\mathbf{R}_1 = \mathbf{R}_2 = \cdots \mathbf{R}_M = \mathbf{R} \tag{2.9}$$

in order to reduce the number of hyper-parameters and avoid overfitting.

Figure 2-1. The prior knowledge for model coefficients is illustrated.

As shown in (2.1), the prior knowledge of sparsity and correlation is encoded by the hyperparameters. To complete the definition of prior distribution for all model coefficients in  $\alpha$ , we further assume that  $\beta_i$  and  $\beta_j$  are statistically independent for any  $i \neq j$ . Therefore, the joint distribution can be represented as:

$$pdf\left(\mathbf{\alpha}\right) \sim N(\mathbf{0}, \mathbf{A}) \tag{2.10}$$

where

$$\mathbf{A} = \begin{bmatrix} \lambda_1 \cdot \mathbf{R} & & \\ & \ddots & \\ & & \lambda_M \cdot \mathbf{R} \end{bmatrix}$$

(2.11)

The independence assumption in (2.10)-(2.11) simply indicates that we do not know any correlation information between different basis functions as our prior knowledge. Such correlation will be learned from sampling points, when the posterior distribution is calculated from Bayesian inference in Section 2.3.

#### 2.3 Maximum-A-Posteriori Estimation

Once the prior distribution  $pdf(\mathbf{\alpha})$  is defined in (2.10)-(2.11), we will combine  $pdf(\mathbf{\alpha})$  with a number of samples collected from K states  $\{(\mathbf{x}_k^{(n)}, y_k^{(n)}); n = 1, 2, ..., N; k = 1, 2, ..., K\}$  to solve the model coefficients  $\mathbf{\alpha}$  by maximum-a-posteriori (MAP) estimation. According to Bayes' theorem, the posterior distribution is proportional to the prior distribution  $pdf(\mathbf{\alpha})$  multiplied by the likelihood function, which can be represented as [61]:

$$pdf(\mathbf{\alpha} \mid \mathbf{y}) \propto pdf(\mathbf{\alpha}) \cdot pdf(\mathbf{y} \mid \mathbf{\alpha}). \tag{2.12}$$

In (2.12),  $pdf(\mathbf{y}|\mathbf{\alpha})$  is the likelihood function, where

$$\mathbf{y} = \begin{bmatrix} y_1^{(1)} & \cdots & y_K^{(1)} & y_1^{(2)} & \cdots & y_K^{(2)} & y_1^{(N)} & \cdots & y_K^{(N)} \end{bmatrix}^T$$

(2.13)

is a vector containing  $N \cdot K$  sampling points collected from K states. The likelihood function  $pdf(\mathbf{y}|\alpha)$  represents the probability of observing these samples given the model coefficients  $\alpha$ .

To derive the likelihood function, we assume that the error associated with the performance model  $f_k(\mathbf{x})$  follows a zero-mean Gaussian distribution. We therefore rewrite (2.1) as:

$$y_{k} = \sum_{m=1}^{M} \alpha_{k,m} \cdot b_{m}(\mathbf{x}) + \varepsilon \quad (k = 1, 2, \dots, K)$$

(2.14)

where  $\varepsilon$  represents the modeling error with the following distribution:

$$pdf\left(\varepsilon\right) = \frac{1}{\sqrt{2\pi} \cdot \sigma_0} \cdot \exp\left(-\frac{\varepsilon^2}{2 \cdot \sigma_0^2}\right) \sim N\left(0, \sigma_0^2\right). \tag{2.15}$$

In (2.15) the standard deviation  $\sigma_0$  controls the magnitude of the modeling error. Combining (2.14)-(2.15) yields the probability of observing a particular sampling point  $(\mathbf{x}_k^{(n)}, y_k^{(n)})$ :

$$pdf\left(y_{k}^{(n)}|\boldsymbol{\alpha}\right) \sim \frac{1}{\sqrt{2\pi} \cdot \sigma_{0}} \cdot \exp\left\{-\frac{1}{2 \cdot \sigma_{0}^{2}} \cdot \left[y_{k}^{(n)} - \sum_{m=1}^{M} \alpha_{k,m} \cdot b_{m}\left(\mathbf{x}_{k}^{(n)}\right)\right]^{2}\right\} \cdot \tag{2.16}$$

Given that all sampling points are independently generated, the joint likelihood function  $pdf(\mathbf{y}|\alpha)$  can be written as:

$$pdf\left(\mathbf{y}\,|\,\mathbf{\alpha},\sigma_{0}\right) \sim N\left(\mathbf{D}\mathbf{\alpha},\sigma_{0}^{2}\mathbf{I}\right) \tag{2.17}$$

where **D** is a matrix with  $N \cdot K$  rows and  $M \cdot K$  columns. The matrix **D** can be obtained by permuting the rows and columns of the following block diagonal matrix:

$$\begin{bmatrix} \mathbf{B}_1 & & \\ & \ddots & \\ & & \mathbf{B}_K \end{bmatrix} \tag{2.18}$$

where  $\{\mathbf{B}_k; k = 1, 2, \dots, K\}$  are defined in (2.3). Combining (2.10), (2.12) and (2.17), the posterior distribution can be calculated as [61]:

$$pdf\left(\boldsymbol{\alpha} \mid \mathbf{y}\right) \sim N\left(\boldsymbol{\mu}_{P}, \boldsymbol{\Sigma}_{p}\right) \tag{2.19}$$

where

$$\Sigma_{p} = \mathbf{A} - \mathbf{A} \mathbf{D}^{T} \left( \sigma_{0}^{2} \mathbf{I} + \mathbf{D} \mathbf{A} \mathbf{D}^{T} \right)^{-1} \mathbf{D} \mathbf{A}$$

(2.20)

$$\boldsymbol{\mu}_{P} = \sigma_{0}^{-2} \boldsymbol{\Sigma}_{p} \mathbf{D}^{T} \mathbf{y}. \tag{2.21}$$

The MAP solution of the model coefficients  $\alpha$  is:

$$\mathbf{\alpha} = \mathbf{\mu}_P = \sigma_0^{-2} \mathbf{\Sigma}_p \mathbf{D}^T \mathbf{y} \,. \tag{2.22}$$

While the proposed Bayesian inference has been illustrated, the hyper-parameters in the prior distribution (2.10) and the likelihood function (2.17) must be appropriately determined in order to solve the model coefficients  $\alpha$ . In the next section, we will further discuss a statistical inference to find the optimal hyper-parameter values.

### 2.4 Hyper-Parameter Inference

The hyper-parameters of our proposed Bayesian inference are defined in Section 2.2 and Section 2.3:  $\Omega = {\lambda_1, \lambda_2, ..., \lambda_M, \mathbf{R}, \sigma_0}$ . To determine these hyper-parameters, one possible approach is to apply

cross-validation [61] which has been successfully used for various applications [74]-[79]. However, the cross-validation approach is not applicable to our Bayesian inference here. It is well-known that the computational complexity of cross-validation exponentially grows with the number of hyper-parameters, and thus is only suitable to handle small-size problems. Our Bayesian inference involves a large number of hyper-parameters, since the number of basis functions (i.e., M) can easily reach several thousand due to the large number of device-level process parameters at an advanced technology node. Hence, an alternative approach must be developed to efficiently determine these hyper-parameters in  $\Omega$ .

Statistically, the hyper-parameters can be determined by maximizing the conditional probability of observing the data set, i.e., the marginal likelihood:

$$l(\Omega) = pdf(\mathbf{y} | \Omega) = \int pdf(\mathbf{y} | \mathbf{\alpha}, \Omega) pdf(\mathbf{\alpha} | \Omega) \cdot d\mathbf{\alpha}.$$

(2.23)

The integration in indicates that the effect of model coefficients  $\alpha$  is averaged out in the marginal likelihood. Given that the two terms in the integration depend on different sets of hyper-parameters in  $\Omega$ , we can rewrite (2.23) as:

$$l(\Omega) = \int pdf(\mathbf{y} \mid \mathbf{\alpha}, \sigma_0) pdf(\mathbf{\alpha} \mid \lambda_1, ..., \lambda_M, \mathbf{R}) \cdot d\mathbf{\alpha}.$$

(2.24)

By combining (2.10)-(2.11) and (2.17) and taking the negative logarithm for (2.24), we have:

$$L(\Omega) = \mathbf{y}^{T} \left(\sigma_{0}^{2} \mathbf{I} + \mathbf{D} \mathbf{A} \mathbf{D}^{T}\right)^{-1} \mathbf{y} + \log \left|\sigma_{0}^{2} \mathbf{I} + \mathbf{D} \mathbf{A} \mathbf{D}^{T}\right|.$$

(2.25)

The hyper-parameters can be found by minimizing the cost function in (2.25). However, minimizing (2.25) is not trivial, because the cost function is not convex. Here we adopt an expectation-maximization (EM) algorithm to address this challenge. In particular, instead of directly minimizing (2.25), the EM algorithm approaches a local optimum of (2.25) by iteratively performing two operations [61], [83], known as the expectation step and the maximization step respectively.

In the expectation step, we first calculate the posterior distribution  $pdf(\mathbf{a}|\mathbf{y}, \Omega^{(\text{old})})$  according to (2.19)-(2.21) based on  $\Omega^{(\text{old})}$ , where  $\Omega^{(\text{old})}$  denotes the hyper-parameters calculated in the last iteration. Next, we define the following quantity [61]:

$$Q(\Omega \mid \Omega^{(old)}) = \mathbf{E}_{\mathbf{a} \mid \mathbf{v}, \Omega^{(old)}} \left[ \log p(\mathbf{y}, \boldsymbol{\alpha} \mid \Omega^{(old)}) \right]$$

(2.26)

where the operator **E** represents the expectation of the log probability function with respect to the posterior distribution  $pdf(\mathbf{a}|\mathbf{y}, \Omega^{(\text{old})})$ . Note that the expected value in (2.26) depends on the mean vector  $\mathbf{\mu}_p$  and the

covariance matrix  $\Sigma_p$  of the posterior distribution in (2.19).

In the maximization step, we try to find  $\Omega$  such that:

$$\Omega = \arg\max_{\Omega} Q\left(\Omega \mid \Omega^{(old)}\right). \tag{2.27}$$

The optimal solution of  $\Omega$  corresponds to:

$$\frac{\partial}{\partial \Omega} Q(\Omega \mid \Omega^{(old)}) = 0. \tag{2.28}$$