# Parasitic-Aware Common-Centroid FinFET Placement and Routing for Current-Ratio Matching

PO-HSUN WU, National Cheng Kung University MARK PO-HUNG LIN, National Chung Cheng University XIN LI, Carnegie Mellon University TSUNG-YI HO, National Tsing Hua University

The FinFET technology is regarded as a better alternative for modern high-performance and low-power integrated-circuit design due to more effective channel control and lower power consumption. However, the gate-misalignment problem resulting from process variation and the parasitic resistance resulting from interconnecting wires based on the FinFET technology becomes even more severe compared with the conventional planar CMOS technology. Such gate misalignment and unwanted parasitic resistance may increase the threshold voltage and decrease the drain current of transistors. When applying the FinFET technology to analog circuit design, the variation of drain currents can destroy current-ratio matching among transistors and degrade circuit performance. In this article, we present the first FinFET placement and routing algorithms for layout generation of a common-centroid FinFET array to precisely match the current ratios among transistors. Experimental results show that the proposed matching-driven FinFET placement and routing algorithms can obtain the best current-ratio matching compared with the state-of-the-art common-centroid placer

CCS Concepts: ● Hardware → Physical synthesis; Full-custom circuits;

Additional Key Words and Phrases: Analog placement, routing, FinFET, gate misalignment, parasitic resistance, common centroid, current-ratio matching

#### **ACM Reference Format:**

Po-Hsun Wu, Mark Po-Hung Lin, Xin Li, and Tsung-Yi Ho. 2016. Parasitic-aware common-centroid FinFET placement and routing for current-ratio matching. ACM Trans. Des. Autom. Electron. Syst. 21, 3, Article 39 (April 2016), 22 pages.

DOI: http://dx.doi.org/10.1145/2856031

#### 1. INTRODUCTION

In modern system-on-chip (SoC) design, the voltage of a transistor has been aggressively operated from the traditional super-threshold region to the sub/near-threshold region to effectively reduce power consumption of integrated circuits [Dreslinski et al.

A preliminary version of this article was presented at 2015 ACM International Symposium on Physical Design (ISPD) [Wu et al. 2015]. This work was partially supported by the Ministry of Science and Technology of Taiwan, under Grant No's. MOST 102-2221-E-194-065-MY2, MOST 103-2917-I-006-086, and MOST 104-2628-E-194-001-MY3.

Authors' addresses: P.-H. Wu, Department of Computer Science and Information Engineering, National Cheng Kung University, 1 University Rd., Tainan 701, Taiwan; email: devilangel@eda.csie.ncku.edu.tw; M. P.-H. Lin (contact author), Department of Electrical Engineering and AIM-HI, National Chung Cheng University, 168 University Rd., Minxiong, Chiayi 621, Taiwan; email: marklin@ccu.edu.tw; X. Li, Department of Electrical and Computer Engineering, Carnegie Mellon University, 2123 Hamerschlag Hall, 5000 Forbes Avenue, Pittsburgh, PA 15213; email: xinli@cmu.edu; T.-Y. Ho, Department of Computer Science, National Tsing Hua University, 101, Sec. 2, Kuang-Fu Rd., Hsinchu 300, Taiwan; email: tyho@cs.nthu.edu.tw.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© 2016 ACM 1084-4309/2016/04-ART39 \$15.00

DOI: http://dx.doi.org/10.1145/2856031

39:2 P.-H. Wu et al.

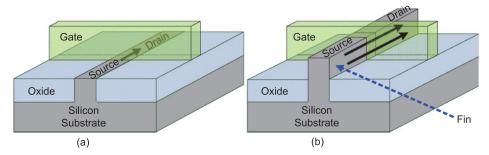

Fig. 1. Structural comparison between MOSFET and FinFET [Intel 2011]. (a) An example of planar MOSFET. (b) An example of 3-D FinFET.

2010]. When MOSFET operates in the on state, it forms a conductive channel in the silicon region under the gate electrode, as shown in Figure 1(a). As the conventional planar CMOS technology scales down to the 22nm node and beyond, the conductive channel becomes shorter and more challenging to effectively control short-channel effects (SCEs) [ITRS 2012]. Consequently, high-leakage current and threshold voltage variation will significantly affect the circuit performance, power dissipation, and reliability of circuits.

To overcome the difficulty of planar CMOS scaling, several new device technologies have been developed as alternatives to the bulk-silicon MOSFET structure for improved reliability. Among these device technologies, the three-dimensional (3-D) aspect of the Fin Field Effect Transistor (FinFET) has been regarded as one of the most promising technologies to substitute for the bulk-silicon MOSFET for ultimate scaling [Chiarella et al. 2010]. When the FinFET operates in the on state, it forms a conductive channel wrapped by a vertical silicon "fin," as in Figure 1(b). With the wraparound gate structure, FinFETs can better control the drain-source channel to alleviate SCEs and reduce random dopant fluctuations by near-intrinsic channel doping [Rasouli et al. 2009]; hence, both leakage current and threshold voltage variation can be significantly reduced [Chiarella et al. 2010]. With these advantages, it has been suggested to design the analog integrated circuits with FinFETs for greater improvement of power, performance, and chip area [Wambacq et al. 2007].

Although the FinFET technology can effectively minimize the impact from SCEs and benefit power, performance, and chip area of integrated circuits, some lithography-induced process variations and layout-induced parasitic effects become even more severe.

# 1.1. Current Mismatch Due to Gate Misalignment

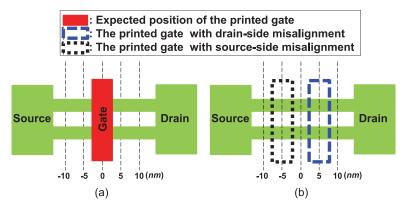

Due to the gate misalignment, the position of the printed gate of a FinFET may deviate from the expected position after a set of lithography processes, which increases the threshold voltage and decreases the drain current of the FinFET [Valin et al. 2012; Fulde et al. 2007; Sarangia et al. 2013]. Figure 2 shows an example of gate misalignment. Ideally, the gate of a FinFET is expected to be located at the center between source and drain, as shown in Figure 2(a). However, the printed gate is usually misaligned due to process variation, as shown in Figure 2(b). According to Valin et al. [2012], the misaligned distance can be as large as 5nm either to the source side or the drain side for a 10nm process technology. Sarangia et al. [2013] reported that the threshold voltage of a FinFET,  $V_{th}$ , is more sensitive with source-side misalignment than with drain-side misalignment. In the worst case, when the gate is misaligned to the drain side of a FinFET by 5nm,  $V_{th}$  is increased by 0.01V. On the other hand, when

Fig. 2. An example of gate misalignment of a FinFET [Valin et al. 2012]. (a) An ideal FinFET without gate misalignment. (b) A real FinFET with either drain-side or source-side gate misalignment.

the gate is misaligned to the source side of a FinFET by 5nm,  $V_{th}$  is increased by 0.05V. This increment can significantly degrade the drain current of the FinFET by 40% with a supply voltage of 1V.

As most of the analog building blocks, such as current mirrors and differential pairs, require highly matched drain current, any current variation due to gate misalignment may destroy current-ratio matching and degrade circuit performance. Consequently, it is essential to consider the existence of gate misalignment during the layout design of these building blocks. It should be noted that, during IC fabrication, the direction and distance of gate misalignment of different FinFETs on the same chip are usually the same. What designers need to do is to carefully arrange the orientations of all FinFETs within a current mirror or a differential pair such that the ratio of the drain current among different transistors in a current mirror or a differential pair can be perfectly matched [Fulde et al. 2007].

# 1.2. Current Mismatch Due to Parasitic Resistance

In addition to gate misalignment, based on the FinFET technology, the parasitic resistance of interconnecting wires becomes nonnegligible [Subramanian et al. 2006]. It gradually dominates the performance, signal integrity, and reliability of circuit designs [Baldi et al. 2001]. Without carefully considering parasitic resistance in analog IC layouts, the drain current of a transistor can be dramatically changed. As mentioned in Section 1.1, most of the analog building blocks, such as current mirrors and differential pairs, are very sensitive to the current variation or current mismatch; any current variation due to parasitic resistance can also destroy current-ratio matching and degrade circuit performance. Therefore, it is also necessary to consider the existence of routing-induced parasitic resistance during the layout design of these building blocks.

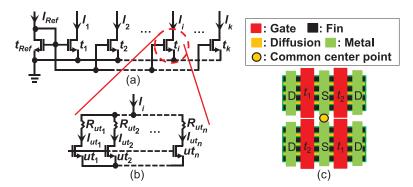

A current mirror with one reference transistor,  $t_{Ref}$ , and k scaled transistors,  $t_1$ ,  $t_2, \ldots, t_k$ , as shown in Figure 3(a), is to produce a set of constant replicated currents,  $I_1$ ,  $I_2, \ldots, I_k$ , flowing through  $t_1, t_2, \ldots, t_k$ , regardless of its loading by copying the reference current,  $I_{Ref}$ , flowing through  $t_{Ref}$ . If the size, or the channel width, of a scaled transistor,  $t_i$ , is n times larger than that of  $t_{Ref}$ ,  $I_i$  is scaled by a factor of n with respect to  $I_{Ref}$ . To reduce transistor mismatch due to process variation, each transistor is decomposed into several unit transistors, as shown in Figure 3(b). The unit transistors are then placed symmetrically with respect to a common center point, as shown in Figure 3(c).

39:4 P.-H. Wu et al.

Fig. 3. (a) A current mirror with one reference transistor and k scaled transistors. (b) Transistor decomposition reducing the impact from process variation, but increasing parasitic resistance. (c) An example common-centroid FinFET placement of a current mirror with one reference transistor,  $t_1$ , and one scaled transistor,  $t_2$ , where  $t_1$  and  $t_2$  are decomposed into two unit transistors, respectively.

In Figure 3(a), as the source terminals of different transistors in a current mirror are fully connected, the routing wires connecting the source terminals of different transistors are short enough; hence, the respective parasitic resistance is negligible. However, when generating a layout of a great number of unit transistors with the commoncentroid constraint, some unit transistors belonging to the same transistor,  $t_i$ , may be placed far away from each other. There exists a nonnegligible parasitic resistance,  $R_{ut_j}$ , corresponding to the routing wires connecting the drain terminal of a unit transistor,  $ut_j$ , and the drain terminals of other unit transistors, as shown in Figure 3(b). Consequently, it is essential to match the interconnecting wirelength during commoncentroid FinFET placement and routing for better current-ratio matching such that the current mismatch due to the existence of parasitic resistance is reduced.

#### 1.3. Previous Works

To generate a matched layout of the transistors in a current mirror or a differential pair, all the previous works [Ma et al. 2011; Lin et al. 2011; Xiao and Young 2009; Lin et al. 2009, 2007; Long et al. 2005; Ma et al. 2007; Yan et al. 2006; Zhang et al. 2010] presented various common-centroid placement and routing approaches for planar MOSFETs with the considerations of coincidence, symmetry, dispersion, and compactness [Hastings. 2006]. None of the previous works considered the impact of gate misalignment arising from the FinFET technology and the matching of parasitic resistance during commoncentroid placement and routing. Although Long et al. [2005] mentioned the chirality condition of transistors within a common-centroid structure, this chirality condition cannot achieve the best current-ratio matching with the impact of gate misalignment.

Other recent works [Huang et al. 2013; Lin et al. 2012b; Ho et al. 2013; Li et al. 2014; Lin et al. 2012a, 2013, 2014] focused on the optimization of common-centroid capacitor placement and routing, but the capacitors in these works are still not associated with the FinFET technology and none considered the impact of parasitic resistance during common-centroid placement and routing.

As a result, a common-centroid layout having the best current-ratio matching with the existence of gate misalignment and parasitic resistance cannot be successfully generated by existing approaches.

# 1.4. Our Contributions

The contributions of this article are summarized as follows:

- —We propose the *first* common-centroid FinFET placement and routing formulation that simultaneously considers the impact of gate misalignment and parasitic resistance, together with all conventional common-centroid rules, including coincidence, symmetry, dispersion, and compactness, for next-generation analog design.

- —We derive a new quality metric to evaluate current-ratio matching among transistors in a current mirror with the existence of gate misalignment and parasitic resistance within a common-centroid FinFET array.

- —Based on the derived quality metric and the spatial correlation model, we present novel parasitic-aware FinFET placement and routing algorithms to optimize current-ratio matching while maximizing the dispersion degree of a common-centroid FinFET array.

- —Our experimental results show that the proposed approach can achieve much better current-ratio matching among transistors in a current mirror with the existence of gate misalignment and parasitic resistance while maintaining high dispersion degree.

The rest of this article is organized as follows: Section 2 reviews the spatial correlation model for evaluating the dispersion degree of a common-centroid FinFET placement. Section 3 demonstrates the current mismatch resulting from the impact of gate misalignment and parasitic resistance. Section 4 details the proposed common-centroid FinFET placement and routing algorithms. Section 5 contains the experimental results. We present our conclusions in Section 6.

#### 2. EVALUATION OF DISPERSION DEGREE WITH SPATIAL CORRELATION MODEL

When generating the common-centroid placement of a current mirror, it is necessary to optimize the matching quality among the reference transistor and all the other scaled transistors for accurate scaling factors. According to Lin et al. [2012b], the transistor mismatch occurring due to process variation can be divided into two categories: systematic mismatch and random mismatch. To reduce systematic mismatch, each transistor is decomposed into several unit transistors that are placed symmetrically with respect to a common center point, as shown in Figure 3(c). On the other hand, random mismatch is mainly related to statistical fluctuations in processing conditions or material properties. As these fluctuations are in random mechanisms, all unit transistors of each transistor should be evenly distributed throughout a common-centroid placement to exhibit the highest degree of dispersion [Razavi 2000].

Luo et al. [2008] proposed a spatial correlation model to measure the overall correlation coefficient, or the dispersion degree,  $\rho$ , of a common-centroid placement. For n transistors,  $\rho$  equals the summation of all correlation coefficients of a pair of transistors, which is defined in Equation (1).

$$\rho = \sum_{i=1}^{n-1} \sum_{j=i+1}^{n} \sigma_{ij},\tag{1}$$

where  $\sigma_{ij}$  is the correlation coefficient of two transistors,  $t_i$  and  $t_j$ . By assuming that  $t_i$  consists of  $n_i$  unit transistors and  $t_j$  consists of  $n_j$  unit transistors,  $\sigma_{ij}$  can be calculated based on Equation (2).

$$\sigma_{ij} = \frac{\sum_{a=1}^{n_i} \sum_{b=1}^{n_j} \rho_{ab}}{\sqrt{X_i \times X_j}},\tag{2}$$

where  $\rho_{ab}$  is the correlation coefficient of two unit transistors, and  $X_k = n_k + 2 \times \sum_{a=1}^{n_k-1} \sum_{b=a+1}^{n_k} \rho_{ab}$ . Assume that a set of unit transistors of all transistors are arranged in a matrix with  $N_r$  rows and  $N_c$  columns. Given two unit transistors,  $ut_i$  and  $ut_j$ ,

39:6 P.-H. Wu et al.

located at the entries in the  $r_i^{th}$  row and  $c_i^{th}$  column and the  $r_j^{th}$  row and  $c_j^{th}$  column, respectively, their correlation coefficient,  $\rho_{ij}$ , is defined in Equation (3).

$$\rho_{ij} = \rho_u^{\sqrt{(r_i - r_j)^2 \times l_r^2 + (c_i - c_j)^2 \times l_c^2}},\tag{3}$$

where  $0 < \rho_u < 1$ , and  $l_r$  ( $l_c$ ) is the center-to-center distance between vertically (horizontally) adjacent transistors.

Based on the correlation model, the larger the  $\rho$ , the better dispersion degree of a common-centroid placement.

# 3. CURRENT MISMATCH RESULTING FROM GATE MISALIGNMENT AND PARASITIC RESISTANCE

As mentioned in Section 1, the issues of gate misalignment and parasitic resistance based on the FinFET technology may have high impact on the drain currents of different transistors in a current mirror. In addition to evaluating the dispersion degree of a common-centroid placement based on the spatial correlation model, it is also necessary to study how to evaluate the matching quality of drain currents with the existence of gate misalignment and parasitic resistance.

In Section 3.1, we first derive the quality metric for evaluating the current mismatch of a current mirror within a common-centroid FinFET array with the existence of gate misalignment and parasitic resistance. In Section 3.2, we present a case study to show the importance of determining the orientation of each transistor and considering the matching of parasitic resistance during common-centroid FinFET placement and routing for minimizing the impact of gate misalignment and parasitic resistance.

# 3.1. Evaluation of Current Mismatch

To copy the reference current to other scaled transistors, the scaled transistor must be operated in the saturation region [Razavi 2000]. According to Subramanian et al. [2006], the drain current of a unit transistor,  $ut_i$ , in the saturation region with the existence of parasitic resistance at the drain terminal is defined by Equation (4).

$$I_{ut_i} = \frac{\frac{\mu \times C_{ox} \times W_{ut}}{2 \times L_{ut}} \times (V_{GS} - V_{th})^2}{1 + \frac{\mu \times C_{ox} \times W_{ut}}{L_{ut}} \times (V_{GS} - V_{th}) \times R_{ut_i}} = \frac{f_1(V_{th})}{1 + f_2(V_{th}) \times R_{ut_i}},$$

(4)

where  $R_{ut_i}$  represents the parasitic resistance corresponding to the wires connecting the drain terminal of  $ut_i$  and the drain terminal of other unit transistors belonging to the same transistor. We adopt the 10nm FinFET technology with 1V supply voltage. The process parameters, as listed in Table I, can be obtained from ITRS [2012] and Liu et al. [1998].

As the impact of gate misalignment may increase  $V_{th}$  of transistors,  $I_{ut_i}$  can be written as functions of  $V_{th}$ . With the consideration of gate misalignment, the threshold voltage of the unit transistors with drain-side misalignment is denoted as  $V_{th}^d$  and the threshold voltage of the unit transistors with source-side misalignment is denoted as  $V_{th}^s$ . Based on Equation (4), if a transistor,  $t_i$ , containing  $n^d$  unit transistors with drain-side gate misalignment and  $n^s$  unit transistors with source-side misalignment, where  $n = n^d + n^s$ , the drain current,  $I_i$ , with the existence of gate misalignment and parasitic resistance

| Parameter             | Value                        | Description                     |

|-----------------------|------------------------------|---------------------------------|

| μ                     | $0.03 \frac{m}{V \cdot s}$   | Carrier mobility                |

| $C_{ox}$              | $3.453$ E-02 $\frac{F}{m^2}$ | Capacitance of gate oxide       |

| $L_{ut} (W_{ut})$     | 30nm (75nm)                  | Channel length (width) of a     |

|                       |                              | unit transistor                 |

| $V_{GS}$              | 1V                           | Voltage difference between      |

|                       |                              | gate and source terminals       |

| $V_{th}$              | 0.15V                        | Threshold voltage               |

| $V_{th}^d (V_{th}^s)$ | 0.151V (0.155V)              | Threshold voltage with drain-   |

|                       |                              | side (source-side) misalignment |

| $R_s$                 | $0.07 \frac{\Omega}{nm}$     | Sheet resistance                |

Table I. Parameters of the 10*nm* FinFET Process Technology [ITRS 2012; Liu et al. 1998]

can be expressed by Equation (5).

$$I_{i} = I_{ut_{1}}^{d} + \dots + I_{ut_{j}}^{d} + I_{ut_{j+1}}^{s} + \dots + I_{ut_{n}}^{s}$$

$$= \left(\frac{1}{1 + f_{2}(V_{th}^{d}) \times R_{ut_{1}}} + \dots + \frac{1}{1 + f_{2}(V_{th}^{d}) \times R_{ut_{j}}}\right) \times f_{1}(V_{th}^{d})$$

$$+ \left(\frac{1}{1 + f_{2}(V_{th}^{s}) \times R_{ut_{j+1}}} + \dots + \frac{1}{1 + f_{2}(V_{th}^{s}) \times R_{ut_{n}}}\right) \times f_{1}(V_{th}^{s}),$$

(5)

where  $V^d_{th}$  ( $V^s_{th}$ ) denotes the respective threshold voltage of  $ut_i$  with the drain (source)-side misalignment, and  $I^d_{ut_i}$  ( $I^s_{ut_i}$ ) is the resulting drain current of  $ut_i$  with  $V^d_{th}$  ( $V^s_{th}$ ). We apply Taylor series expansion to Equation (5) since all parameters, including

We apply Taylor series expansion to Equation (5) since all parameters, including  $\mu$ ,  $C_{ox}$ , and  $\frac{W_{ut}}{L_{ut}}$ , in the function,  $f_2$ , are small constants based on Table I, and  $R_{ut_i}$  is also less than 1  $\Omega$ . Consequently, we have the following approximations:  $\frac{1}{1+f_2(V_{th}^d)\times R_{ut_i}}\approx 1-f_2(V_{th}^d)\times R_{ut_i}$ , and  $\frac{1}{1+f_2(V_{th}^d)\times R_{ut_i}}$  can be approximated similarly. As a result,  $I_i$  can be transformed into Equation (6).

$$I_{i} = (n^{d} - f_{2}(V_{th}^{d}) \times (R_{ut_{1}} + \dots + R_{ut_{j}})) \times f_{1}(V_{th}^{d}) + (n^{s} - f_{2}(V_{th}^{s}) \times (R_{ut_{j+1}} + \dots + R_{ut_{n}})) \times f_{1}(V_{th}^{s}) = (n^{d} - f_{2}(V_{th}^{d}) \times R_{i}^{d}) \times f_{1}(V_{th}^{d}) + (n^{s} - f_{2}(V_{th}^{s}) \times R_{i}^{s}) \times f_{1}(V_{th}^{s}),$$

$$(6)$$

where  $R_i^d$   $(R_i^s) = L_i^d$   $(L_i^s) \times R_s$ .  $L_i^d$   $(L_i^s)$  is total wirelength of the interconnection among the drain (source) terminals of  $ut_i$  and those of other unit transistors, and  $R_i^d$   $(R_i^s)$  is the parasitic resistance corresponding to  $L_i^d$   $(L_i^s)$ .

Based on Equation (6) and the current mirror, as seen in Figure 3, we want to

Based on Equation (6) and the current mirror, as seen in Figure 3, we want to optimize the current-ratio matching among different transistors in the current mirror. The objective of optimizing current-ratio matching is shown in Equation (7).

$$I_{1}: I_{2}: \dots: I_{k} = n_{1}: n_{2}: \dots: n_{k}$$

$$= (n_{1}^{d} - f_{2}(V_{th}^{d}) \times R_{1}^{d}) \times f_{1}(V_{th}^{d}) + (n_{1}^{s} - f_{2}(V_{th}^{s}) \times R_{1}^{s}) \times f_{1}(V_{th}^{s})$$

$$: (n_{2}^{d} - f_{2}(V_{th}^{d}) \times R_{2}^{d}) \times f_{1}(V_{th}^{d}) + (n_{2}^{s} - f_{2}(V_{th}^{s}) \times R_{2}^{s}) \times f_{1}(V_{th}^{s})$$

$$: \dots: (n_{k}^{d} - f_{2}(V_{th}^{d}) \times R_{k}^{d}) \times f_{1}(V_{th}^{d}) + (n_{k}^{s} - f_{2}(V_{th}^{s}) \times R_{k}^{s}) \times f_{1}(V_{th}^{s})$$

$$: \dots: (n_{k}^{d} - f_{2}(V_{th}^{d}) \times R_{k}^{d}) \times f_{1}(V_{th}^{d}) + (n_{k}^{s} - f_{2}(V_{th}^{s}) \times R_{k}^{s}) \times f_{1}(V_{th}^{s})$$

$$: \dots: (n_{k}^{d} - f_{2}(V_{th}^{d}) \times R_{k}^{d}) \times f_{1}(V_{th}^{d}) + (n_{k}^{s} - f_{2}(V_{th}^{s}) \times R_{k}^{s}) \times f_{1}(V_{th}^{s})$$

39:8 P.-H. Wu et al.

By applying the multiplication property and substituting  $n_i$  with  $n_i^d + n_i^s$ , we can obtain Equations (8) and (9), respectively,

$$\frac{1}{n_{i}} \times \left( \left( n_{i}^{d} - f_{2}(V_{th}^{d}) \times R_{i}^{d} \right) \times f_{1}(V_{th}^{d}) + \left( n_{i}^{s} - f_{2}(V_{th}^{s}) \times R_{i}^{s} \right) \times f_{1}(V_{th}^{s}) \right) \\

= \frac{1}{n_{j}} \times \left( \left( n_{j}^{d} - f_{2}(V_{th}^{d}) \times R_{j}^{d} \right) \times f_{1}(V_{th}^{d}) + \left( n_{j}^{s} - f_{2}(V_{th}^{s}) \times R_{j}^{s} \right) \times f_{1}(V_{th}^{s}) \right), \\

\forall i, j, 1 \leq i \leq k-1, 2 \leq j \leq k.$$

(8)

$$\epsilon_{i-j} = \epsilon_{i-j}^{G} + \epsilon_{i-j}^{P} = \frac{\alpha \times \left(n_{i}^{d} \times n_{j}^{s} - n_{j}^{d} \times n_{i}^{s}\right)}{n_{i} \times n_{j}} + \left(\frac{\beta \times \left(R_{j}^{d} \times n_{i} - R_{i}^{d} \times n_{j}\right)}{n_{i} \times n_{j}} + \frac{\gamma \times \left(R_{j}^{s} \times n_{i} - R_{i}^{s} \times n_{j}\right)}{n_{i} \times n_{j}}\right),$$

$$\forall i, j, 1 < i < k - 1, 2 < j < k.$$

$$(9)$$

In Equation (9),  $\epsilon_{i-j}$  denotes the current mismatch between  $t_i$  and  $t_j$ , and  $\epsilon_{i-j}^G$  ( $\epsilon_{i-j}^P$ ) is the current mismatch resulting from the impact of gate misalignment (parasitic resistance).  $\alpha = f_1(V_{th}^d) - f_1(V_{th}^s)$ ,  $\beta = f_1(V_{th}^d) \times f_2(V_{th}^d)$ , and  $\gamma = f_1(V_{th}^s) \times f_2(V_{th}^s)$ . If the resulting current ratio equals the expected current ratio (i.e., no current mismatch),  $\epsilon_{i-j}$  equals 0. Consequently, the overall current mismatch among different transistors in a current mirror is obtained by summing up all  $\epsilon_{i-j}$ , as seen in Equation (10).

$$\epsilon = \epsilon^{G} + \epsilon^{P}

= \sum_{i=1}^{k-1} \sum_{j=i+1}^{k} \frac{\left(f_{1}(V_{th}^{d}) - f_{1}(V_{th}^{s})\right) \times \left(n_{i}^{d} \times n_{j}^{s} - n_{j}^{d} \times n_{i}^{s}\right)}{n_{i} \times n_{j}}

+ \sum_{i=1}^{k-1} \sum_{j=i+1}^{k} \left(\frac{f_{1}(V_{th}^{d}) \times f_{2}(V_{th}^{d}) \times \left(R_{j}^{d} \times n_{i} - R_{i}^{d} \times n_{j}\right)}{n_{i} \times n_{j}}

+ \frac{f_{1}(V_{th}^{s}) \times f_{2}(V_{th}^{s}) \times \left(R_{j}^{s} \times n_{i} - R_{i}^{s} \times n_{j}\right)}{n_{i} \times n_{j}}\right).$$

(10)

# 3.2. A Case Study

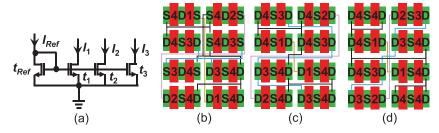

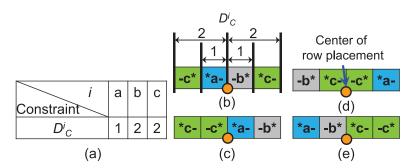

We conduct a case study, as demonstrated in Figure 4, for the following purposes: (1) comparing different common-centroid arrays with and without considering gate misalignment and parasitic resistance, (2) evaluating the resulting current mismatch and dispersion degree of each common-centroid array, and (3) justifying the correctness of Equation (10) based on the drain current model in Equation (4).

The current mirror in Figure 4(a) consists of one reference transistor and three scaled transistors. The reference current,  $I_{Ref}$ , flows through the reference transistor,  $t_{Ref}$ , and the replicated currents,  $I_1$ ,  $I_2$ , and  $I_3$ , are copied from  $I_{Ref}$  to other scaled transistors,  $t_1$ ,  $t_2$ , and  $t_3$  with different scaling factors. The scaling factors, or the number of unit transistors of  $t_{Ref}$ ,  $t_1$ ,  $t_2$ , and  $t_3$ , are 2, 2, 4, and 8, respectively; thus, the expected current ratio,  $I_{Ref}$ :  $I_1$ :  $I_2$ :  $I_3$ , is 1:1:2:4. Figures 4(b)–(d) give three different common-centroid FinFET layouts of Figure 4(a) without and with considering gate misalignment and parasitic resistance, in which the indices of the unit transistors of  $t_{Ref}$ ,  $t_1$ ,  $t_2$ , and  $t_3$  are represented by 1, 2, 3, and 4, respectively.

Fig. 4. Comparisons of different common-centroid FinFET arrays. (a) A current mirror with the ideal current ratio,  $I_{Ref}:I_1:I_2:I_3=1:1:2:4$ . (b) The FinFET placement and routing without considering gate misalignment and parasitic resistance. (c) The FinFET placement and routing considering only gate misalignment. (d) The FinFET placement and routing considering both gate misalignment and parasitic resistance.

Table II. Comparisons of the Simulated Current Ratios, Current Mismatch  $(\epsilon^G \text{ and } \epsilon^P)$ , and Dispersion Degree  $(\rho)$  for the Resulting Common-Centroid Layouts in Figures 4(b)–(d)

| Cases       | Simulated current ratio                                                        | $\epsilon^G$ | $\epsilon^P$ | ρ     |

|-------------|--------------------------------------------------------------------------------|--------------|--------------|-------|

| Figure 4(b) | 1:0.9971:2.2044:4.3048                                                         | 0.192        | 0.004        | 5.733 |

|             | $L_1^s: L_2^s: L_3^s: L_4^s = 4:6:0:4$                                         |              |              |       |

|             | $L_1^{d}: L_2^{d}: L_3^{d}: L_4^{d} = 0:0:8:13$                                |              |              |       |

| Figure 4(c) | 1:0.994:1.994:3.997                                                            | 0.000        | 0.010        | 5.749 |

|             | $L_1^s: L_2^s: L_3^s: L_4^s = 1:3:4:5$                                         |              |              |       |

|             | $L_1^{\tilde{d}}: L_2^{\tilde{d}}: L_3^{\tilde{d}}: L_4^{\tilde{d}} = 1:3:4:5$ |              |              |       |

| Figure 4(d) | 1:0.997:1.997:3.997                                                            | 0.000        | 0.004        | 5.762 |

|             | $L_1^s: L_2^s: L_3^s: L_4^s = 1:2:3:5$                                         |              |              |       |

|             | $L_1^{\tilde{d}}: L_2^{\tilde{d}}: L_3^{\tilde{d}}: L_4^{\tilde{d}} = 1:2:3:5$ |              |              |       |

For each common-centroid layout in Figure 4, we evaluate the dispersion degree and current mismatch based on Equations (1) and (10), and calculate the resulting drain current of each transistor with the consideration of parasitic resistance based on Equation (4). Without loss of generality, we assume that the printed gates of all unit transistors in each common-centroid placement are misaligned to the right side, which is also the worst-case process variation; thus, the printed gate of a unit transistor has either drain-side or source-side misalignment according to its orientation. As mentioned in Section 1.1, in the worst case,  $V_{th}$  is increased by 0.01V (0.05V) with drain-side (source-side) misalignment based on a 10mm FinFET technology with 1V supply voltage. We also adopt these settings to adjust the threshold voltage of each unit transistor when calculating the drain current of each transistor.

Table II reports the simulated current ratio, current mismatch ( $\epsilon^G$  and  $\epsilon^P$ ), and dispersion degree ( $\rho$ ) for all common-centroid layouts in Figures 4(b)–(d). According to the Table II, the common-centroid layout in Figure 4(b) without considering both gate misalignment and parasitic resistance results in the worst current mismatch,  $\epsilon (= \epsilon^G + \epsilon^P)$ . The common-centroid layout in Figure 4(c), with the only consideration of gate misalignment and without considering the impact of parasitic resistance, results in the best  $\epsilon^G$ , but the worst  $\epsilon^P$ . With the consideration of both gate misalignment and parasitic resistance, the common-centroid layout in Figure 4(d) achieves the best  $\epsilon^G$  and  $\epsilon^P$ , thus the best current-ratio matching. Consequently, it is very important to consider both gate misalignment and parasitic resistance when designing the layout of a common-centroid FinFET array.

39:10 P.-H. Wu et al.

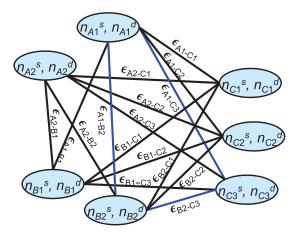

Fig. 5. An example minimum-weight-clique formulation for a current mirror with three transistors, A, B, and C. Each transistor has 2, 2, and 3 possible configurations of unit transistors' orientations, respectively.

### 4. COMMON-CENTROID FINFET PLACEMENT AND ROUTING ALGORITHMS

Based on the evaluation metrics of dispersion degree and current mismatch in Equations (1) and (10), we propose the generation of an optimized common-centroid FinFET layout considering the impact of gate misalignment and parasitic resistance while maximizing the dispersion degree. Our approach starts with the determination of unit transistors' orientations while minimizing the current mismatch resulting from the gate misalignment (Section 4.1). Based on the determined unit transistors' orientations, we then generate an initial common-centroid FinFET placement by maximizing diffusion sharing and dispersion degree among unit transistors in the same row while restricting the placement range (Section 4.2) such that the current mismatch due to the impact of parasitic resistance is reduced. Once the placement of each row is obtained, we further refine the placement by maximizing the dispersion degree among unit transistors in different rows (Section 4.3). Finally, we perform parasitic-aware routing to generate the routing topology of each net while improving the current-ratio matching among different transistors (Section 4.4).

#### 4.1. Determination of Unit Transistor Orientations

In order to reduce the current mismatch due to gate misalignment, the unit transistors' orientations must be properly determined. We formulate the problem as finding the minimum-weight clique [Cormen et al. 2001] in an undirected graph to simultaneously determine the unit transistors' orientations. Each vertex in the graph represents one configuration of the unit transistors' orientations of a transistor,  $t_i$ , which has  $n_i^s$  unit transistors with source-side misalignment and  $n_i^d$  unit transistors with drain-side misalignment, respectively. There exists an edge between two vertices if the vertices correspond to two different transistors,  $t_i$  and  $t_j$ . The edge weight,  $\epsilon_{i-j}^G$ , which can be calculated by Equation (9), denotes the current mismatch between  $t_i$  and  $t_j$  based on the configurations of unit transistors' orientations represented by the vertices.

Solving the minimum-weight-clique problem in a graph is known as an NP-complete problem. We apply the heuristic [Östergård 2001] using the branch-and-bound algorithm. We enumerate all possible configurations (i.e., a k-finger FinFET has k+1 configurations whose orientations are the combination of source-side misalignment and drain-side misalignment) of unit transistor orientations for each transistor in the graph. Figure 5 shows a minimum-weight-clique formulation for a current mirror with

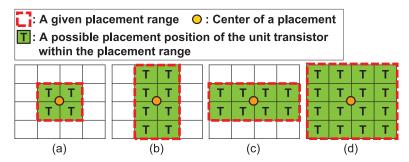

Fig. 6. A set of four probable placement range constraints within a  $4\times 4$  array for placing the unit transistors of  $t_i$ . (a)  $\{D_C^i, D_R^i\} = \{1, 1\}$ . (b)  $\{D_C^i, D_R^i\} = \{1, 2\}$ . (c)  $\{D_C^i, D_R^i\} = \{2, 1\}$ . (d)  $\{D_C^i, D_R^i\} = \{2, 2\}$ .

three transistors, A, B, and C, in which each transistor has 2, 2, and 3 possible configurations of unit transistors' orientations, respectively. By finding the minimum-weight clique in the undirected graph, the best configuration of unit transistors' orientations for each transistor can be determined such that the minimum current mismatch due to gate misalignment,  $\epsilon^G$ , can be achieved.

# 4.2. Common-Centroid FinFET Placement Algorithm Considering Parasitic Resistance and Dispersion

Given the determined unit transistors' orientations, we want to generate an  $N_r$ -row and  $N_c$ -column common-centroid FinFET placement while maintaining unit transistors' orientations, minimizing current mismatch due to parasitic resistance, and maximizing the dispersion degree. Since the orientations of all unit transistors have been determined, the current mismatch of a common-centroid FinFET array is thus dominated by  $\epsilon^P$ . We need to find an optimal placement leading to matched parasitic resistance after routing.

To achieve this goal, we introduce a placement range constraint for each transistor to restrict the placement region of the corresponding unit transistors within an allowable distance, which is defined in the following:

Definition 1. The **placement range constraint** for a transistor,  $t_i$ , is a 2-tuple combination, denoted by  $\{D_C^i, D_R^i\}$ , which restricts the location of a unit transistor of  $t_i$  within the distance of  $D_C^i$  ( $D_R^i$ ) in x-direction (y-direction) from the center of an  $N_r$ -row and  $N_c$ -column unit transistor array.

We determine  $\{D_C^i, D_R^i\}$  of each transistor,  $t_i$ , in a current mirror by minimizing the current mismatch  $\epsilon_{(i)-(j)}$  between any two transistors,  $t_i$  and  $t_j$ . For a transistor,  $t_i$ , we first create a placement region with the range from the  $(\lceil \frac{(N_c+1)}{2} + D_C^i \rceil)^{th}$  column to the  $(\lfloor \frac{(N_c+1)}{2} + D_C^i \rfloor)^{th}$  column and from the  $(\lceil \frac{(N_r+1)}{2} - D_R^i \rceil)^{th}$  row to the  $(\lfloor \frac{(N_r+1)}{2} + D_R^i \rfloor)^{th}$  row, respectively. By iteratively enumerating all possible combinations of  $\{D_C^i, D_R^i\}$ , where  $1 \leq D_C^i \leq \frac{N_c}{2}$  and  $1 \leq D_R^i \leq \frac{N_r}{2}$ , a set of probable placement range constraints,  $\{1, 1\}, \ldots, \{1, \lfloor \frac{(N_r)}{2} \rfloor\}, \{2, 1\}, \ldots, \{\lfloor \frac{(N_c)}{2} \rfloor, \lfloor \frac{(N_r)}{2} \rfloor\}$ , can be derived. Figure 6 gives an example of four probable placement range constraints within a

Figure 6 gives an example of four probable placement range constraints within a  $4\times4$  array for placing the unit transistors of  $t_i$ . By connecting the unit transistors of the reference transistor,  $t_{Ref}$ , with the minimum wirelength, we can optimize the wirelength of the scaled transistors,  $t_i$ , to maximize the matching of parasitic resistance between  $t_{Ref}$  and  $t_i$ . For each derived  $\{D_C^i, D_R^i\}$ , we estimate the resulting wirelength of a net connecting all drain terminals of the unit transistors of  $t_i$  within the possible placement region. Based on the estimated wirelength and Equation (11), which is

39:12 P.-H. Wu et al.

derived from Equation (9), we can obtain the current mismatch between  $t_i$  and  $t_{Ref}$ . We finally choose the best placement range constraint for  $t_i$ , resulting in the minimum current mismatch according to Equation (11).

$$\epsilon_{(Ref)-(i)} = \frac{\left(f_1(V_{th}^d) - f_1(V_{th}^s)\right) \times \left(n_{Ref}^d \times n_i^s - n_i^d \times n_{Ref}^s\right)}{n_{Ref} \times n_i} + \frac{f_1(V_{th}^d) \times f_2(V_{th}^d) \times \left(R_i^d \times n_{Ref} - R_{Ref}^d \times n_i\right)}{n_{Ref} \times n_i} + \frac{f_1(V_{th}^s) \times f_2(V_{th}^s) \times \left(R_i^s \times n_{Ref} - R_{Ref}^s \times n_i\right)}{n_{Ref} \times n_i}.$$

$$(11)$$

Once the placement range constraints of all transistors are obtained, we then perform common-centroid placement according to the optimized placement range constraints. The procedure of our placement algorithm consists of three major steps:

4.2.1. Row Assignment. Given a set of  $n_i$  unit transistors of a transistor,  $t_i$ , based on its placement range constraint, we evenly distribute  $\frac{n_i}{2\times(\lceil\frac{(N_r)}{2}\rceil-\lceil\frac{(N_r+1)}{2}-D_R^i\rceil+1)}$  unit transistors into each row between  $(\lceil\frac{(N_r+1)}{2}-D_R^i\rceil)^{th}$  and  $\lceil\frac{(N_r)}{2}\rceil^{th}$  such that the dispersion degree of a common-centroid FinFET placement can be maximized in the subsequent steps. If  $\frac{n_i}{2}<(\lceil\frac{(N_r)}{2}\rceil-\lceil\frac{(N_r+1)}{2}-D_R^i\rceil+1)$ , we randomly assign the unit transistors into the rows between  $(\lceil\frac{(N_r+1)}{2}-D_R^i\rceil)^{th}$  and  $\lceil\frac{(N_r)}{2}\rceil^{th}$ . During the row assignment, the placement range constraints of each transistor should also be considered.

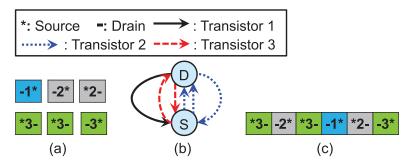

4.2.2. Detailed Placement. Once all unit transistors are assigned to different rows, we generate the detailed placement of each row by searching Euler paths, while maximizing the dispersion and diffusion sharing [Naiknaware and Fiez 1999]. We construct the diffusion graph of the subcircuit in each row; then, we find the Euler paths on the diffusion graph [Naiknaware and Fiez 1999]. However, the diffusion graph that we used in this article is different from Naiknaware and Fiez [1999]. As described in Section 4.1, we have determined the unit transistors' orientations. To avoid degrading the current mismatch, the unit transistors' orientations cannot be changed during the search of the Euler path. Therefore, the constructed diffusion graph is a directed graph instead of an undirected graph used in Naiknaware and Fiez [1999], in which the number of directed edges originating from source node (S) to drain node (D) equals the number of unit transistors with drain-side misalignment, and vice versa.

According to the spatial correlation model in Section 2, to effectively maximize the dispersion degree of a common-centroid FinFET placement, all unit transistors belonging to the same transistor should be properly separated while the unit transistors belonging to different transistors should be as close as possible. For clear presentation, we define different kinds of unit transistors in Definition 2.

*Definition* 2. Two unit transistors are called **unrelated transistors** (**related transistors**), if they belong to different transistors,  $t_i$  and  $t_j$  (the same transistor,  $t_i$ ).

To effectively maximize the dispersion degree of a common-centroid FinFET placement, we set a maximum separation (minimum separation) constraint, as defined in Definition 3, for two unrelated transistors (related transistors) to constrain the selection of edge during finding the Euler paths such that the dispersion degree can be effectively maximized.

Definition 3. A maximum separation constraint (minimum separation constraint) is the maximum (minimum) allowable distance between two neighboring

Fig. 7. An example of constructing the diffusion graph. (a) A set of unit transistors with fixed orientation. (b) The corresponding diffusion graph of (a). (c) The generated row placement by searching the diffusion graph in (b).

unrelated transistors (related transistors) when finding the Euler paths, which is denoted by  $D_{max.sep}$  ( $D_{min.sep}$ ). The distance between two neighboring unit transistors refers to the number of unit transistors between the neighboring unit transistors.

During searching the Euler path, we choose only the edge satisfying both maximum and minimum separation constraints to properly distribute different unit transistors while maximizing the dispersion degree. To obtain a row placement leading to matched parasitic resistance after routing, we shall additionally verify the placement range constraint of each unit transistor during searching the corresponding Euler paths. Initially,  $D_{min.sep}$  is set to 0 and  $D_{max.sep}$  is set to the number of unit transistors in the row to start the procedure of searching the Euler paths. By iteratively increasing  $D_{min.sep}$  and decreasing  $D_{max.sep}$  during the procedure of searching the Euler path until an extra diffusion gap is required, the dispersion degree of the resulting row placement can be effectively maximized. After obtaining the Euler paths, the unit transistors on the same Euler path are merged with diffusion sharing.

Given a set of unit transistors with fixed orientation, as shown in Figure 7(a), a directed diffusion graph can be created, as given in Figure 7(b). Then, starting from the source node, as seen in Figure 7(b), an optimized row placement, as shown in Figure 7(c), can be obtained by iteratively searching the Euler paths with decreasing the maximum separation constraint and increasing the minimum separation constraint. In this example, the iteration stops when  $D_{max.sep} = 3$  and  $D_{min.sep} = 1$ , which does not incur an extra diffusion gap. Moreover, for simplification, we assume that the source terminals/drain terminals of different unit transistors can be merged. If the source terminals/drain terminals of some unit transistors cannot be merged, extra diffusion gaps are created and multiple Euler paths will be obtained.

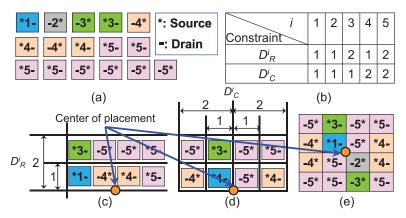

4.2.3. Symmetric Placement Generation. After obtaining the detailed placement of the first half of the rows with diffusion merging, we then generate the symmetric detailed placement of the second half of the rows in a reverse order. For the  $(N_r - i + 1)^{th}$  row in the second half of the rows, the unit transistors are reversely placed according to the  $i^{th}$  row in the first half of the rows. Figure 8 demonstrates the procedure of the overall common-centroid FinFET placement flow.

#### 4.3. Dispersion Degree Maximization Considering Parasitic Resistance

After obtaining the initial common-centroid FinFET placement with optimized diffusion sharing and dispersion degree of the unit transistors in each row, we further maximize the dispersion degree of unit transistors in different rows by adjusting the relative positions of different unit transistors among different rows. We perform

39:14 P.-H. Wu et al.

Fig. 8. An example of generating common-centroid FinFET placement with the consideration of parasitic resistance and dispersion. (a) A set of unit transistors with optimized orientations. (b) The placement range constraints of all transistors. (c) Row assignment of unit transistors, which maximizes dispersion degree and satisfies placement range constraints. (d) Detailed unit transistor placement, which maximizes diffusion sharing, optimizes minimum/maximum separation constraints, and satisfies placement range constraints. (e) Complete common-centroid FinFET placement.

Fig. 9. An example of placement rotation in a row. (a) A set of given placement range constraints. (b) An initial row placement. (c)–(e) Three derived row placements after placement rotation. Only the placement in (c) satisfies the placement range constraints in (a).

placement rotation for each row by iteratively moving the unit transistor at the end of the row to the beginning of the row. During placement rotation, only the rotated placements satisfying the placement range constraints are reserved.

Figure 9 gives an example of placement rotation. The placement range constraints and the initial placement of a row are given in Figures 9(a) and 9(b), respectively. By iteratively moving the unit transistor at the end of the row to the beginning of the row, we can derive three different placements of the row, as shown in Figures 9(c)–(e), respectively. The placements in Figures 9(d) and 9(e) violate the placement distance constraint,  $D_C^a = 1$ , because the distance from the location of the unit transistor, a, to the center of the row is 2. Only the derived placement in Figure 9(c) is reserved. It should be noted that the placement rotation changes only the column position of the unit transistors; thus, we need to verify only  $D_C^i$  for each unit transistor,  $ut_i$ .

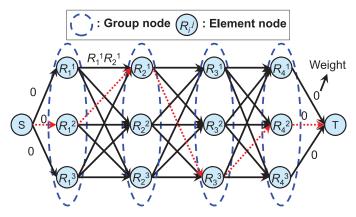

By performing the placement rotation for each row, a set of row placements satisfying placement range constraints can be derived. We then simultaneously select the best placements of all m rows with the largest dispersion degree of the unit transistors among different rows by applying the shortest path algorithm such that the optimal

Fig. 10. An example of the shortest-path (SP) formulation for a 4-row common-centroid FinFET placement.

common-centroid FinFET placement with the consideration of gate misalignment, parasitic resistance, and dispersion degree can be obtained.

The simultaneous selection of the best placement of different rows is formulated as the shortest-path (SP) problem. Initially, a source node (S) and a sink node (T) are created, respectively. For a respective row, a group node is created, in which a set of element nodes representing the possible row placements are contained in the group node. Once the group nodes and element nodes are created, we then add a set of directed edges from S to each element node in the group node corresponding to the first row, and a set of directed edges from each element node in the group node corresponding to the last row to T, for whichn the weight of these edges are all zero. For two adjacent rows, there is a directed edge from an element node in the group node corresponding to the  $i^{th}$  row to an element node in the group node corresponding to the  $i^{th}$  row to an element node in the group node corresponding to the  $i^{th}$  row to an element node in the group node corresponding to the  $i^{th}$  row to an element node in the group node corresponding to the  $i^{th}$  row, where  $1 \le i < m$ . The weight of each edge is calculated based on Equation (1), which indicates the dispersion degree. By finding the SP from S to T, the best placement of each row can be determined and the dispersion degree of the whole common-centroid FinFET placement can be further maximized.

Figure 10 shows an example of the SP formulation for a 4-row common-centroid Fin-FET placement. Each row has three possible row placements after placement rotation. After solving the SP problem, the  $2^{nd}$ ,  $1^{st}$ ,  $3^{rd}$ , and  $2^{nd}$  placements of the  $1^{st}$ ,  $2^{nd}$ ,  $3^{rd}$ , and  $4^{th}$  rows are selected to achieve the best common-centroid FinFET placement with the maximum dispersion degree.

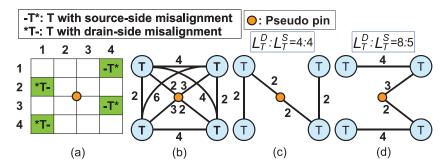

# 4.4. Parasitic-Aware Routing

Once the optimized common-centroid FinFET placement is obtained, we perform parasitic-aware routing to connect the drain terminals of the unit transistors of each transistor while optimizing the routing wirelength to maximize the matching of parasitic resistance.

We first connect the unit transistors of the reference transistor,  $t_{Ref}$ , with the minimum wirelength. To connect the unit transistors of a scaled transistor,  $t_i$ , while maximizing the matching of parasitic resistance between  $t_{Ref}$  and  $t_i$ , we construct a complete graph for the unit transistors of  $t_i$  and find the minimum spanning tree (MST) [Cormen et al. 2001], where the weights of the edges are calculated by half-perimeter wirelength. By choosing the edges based on the nondecreasing order of the routing wirelength, we iteratively exchange the edges contained in the complete graph but not in the MST with the edges contained in the MST to further adjust the routing topology to

39:16 P.-H. Wu et al.

Fig. 11. An example of parasitic-aware routing for current-ratio matching. (a) A set of unit transistors with fixed orientation and positions. (b) The corresponding complete graph of (a). (c) The minimum spanning tree of (b). (d) The routing topology resulting in minimum current mismatch.

|          | T                              |

|----------|--------------------------------|

| Circuits | # of unit transistors          |

| CM1      | 1, 1                           |

| CM2      | 1, 1, 2                        |

| CM3      | 1, 1, 2, 4                     |

| CM4      | 1, 1, 2, 4, 8                  |

| CM5      | 1, 1, 2, 4, 8, 16              |

| CM6      | 1, 1, 2, 4, 8, 16, 32          |

| CM7      | 1, 1, 2, 4, 8, 16, 32, 64      |

| CM8      | 1, 1, 2, 4, 8, 16, 32, 64, 128 |

Table III. The Benchmark Circuits

maximize the matching of parasitic resistance. The best wirelength of  $t_i$  with the minimum  $\epsilon_{(Ref)-(i)}$  in Equation (11) between  $t_{Ref}$  and  $t_i$  is chosen. By applying this topology refinement procedure for each scaled transistor, a common-centroid FinFET placement and routing with optimized matching of parasitic resistance can be generated.

Figure 11 demonstrates an example of the proposed parasitic-aware routing procedure for current-ratio matching. Given a set of unit transistors, T, with fixed orientations and positions, as seen in Figure 11(a), the corresponding complete graph can be constructed, as shown in Figure 11(b). Figure 11(c) shows the resulting MST, for which the wirelength ratio is {4:4}. After performing the wirelength refinement procedure for minimum current mismatch, a new routing topology with the best wirelength ratio, {8:5}, can be derived, as shown in Figure 11(d).

After performing the parasitic-aware routing, the global routing path of each net can be obtained. We then estimate the horizontal/vertical spacing between unit transistors according to the design rules and the number of required routing tracks in a horizontal/vertical channel. We keep the spacing as small as possible for better dispersion degree while satisfying common-centroid constraints.

#### 5. EXPERIMENTAL RESULTS

We implemented the proposed common-centroid FinFET placement methodology in the MATLAB programming language on a personal computer with an Intel Core i7-2600 3.4GHz CPU and 16GB memory. We created a set of test cases of current mirrors, CM1, CM2, ..., CM8, with different width ratios of the transistors, as shown in the second column of Table III. To demonstrate the effectiveness of our approach, we conducted two sets of experiments: (1) applying different placement approaches with our

parasitic-aware routing approach, and (2) applying our parasitic-aware placement with parasitic-unaware and parasitic-aware routing approaches.

#### 5.1. Applying Different Placement Approaches With Our Parasitic-Aware Routing Approach

For the first set of the experiment, we applied different placement approaches with the proposed parasitic-aware routing method. We compared our placement approach with that of Lin et al. [2011], which is known to be the most recent work in the literature handling common-centroid transistor placement with the considerations of diffusion sharing and dispersion and without the considerations of gate misalignment and parasitic resistance. Since the approach of Lin et al. [2011] does not include a router, we also performed our proposed parasitic-aware routing algorithm for their derived placements. To show the importance with and without considering parasitic resistance, we also compare our parasitic-aware placement approach with our ISPD work ("parasitic-unaware placement approach") [Wu et al. 2015]. For each current mirror, the expected current ratio must be equal to the unit transistor ratio. For each common-centroid Fin-FET layout generated by different approaches, we simulated the drain current of each transistor in the current mirror with the impact of gate misalignment and parasitic resistance according to Equation (4). We also evaluated the dispersion degree based on Equation (1) and the current mismatch based on Equation (10).

Table IV compares the simulated current ratio, current mismatch resulting from the impact of gate misalignment (" $\epsilon^{G}$ "), current mismatch resulting from the impact of parasitic resistance (" $\epsilon^P$ "), total current mismatch (" $\epsilon = \epsilon^G + \epsilon^P$ "), dispersion degree (" $\rho$ "), and runtime ("T") for different approaches. According to Table IV, with the consideration of gate misalignment, the parasitic-unaware placement approach can obtain a more accurate simulated current ratio than the approach of Lin et al. [2011] compared with the expected current ratio for all circuits. When comparing the evaluation metric of current mismatch with the approach of Lin et al. [2011], the parasitic-unaware placement approach can achieve up to 78% improvement, which is calculated by  $\frac{\epsilon_2 - \epsilon_1}{\epsilon_1}$ . When considering both gate misalignment and parasitic resistance during common-centroid FinFET placement and routing, our parasitic-aware approach can derive the most accurate simulated current ratio compared with the expected current ratio for all circuits among these approaches. Moreover, our parasitic-aware approach can reduce up to 86% and 67% current mismatch compared with the approach of Lin et al. [2011] and the parasitic-unaware placement approach, which are calculated by  $\frac{\epsilon_3-\epsilon_1}{\epsilon_1}$  and  $\frac{\epsilon_3-\epsilon_2}{\epsilon_2}$ , respectively. It should be noted that all  $\epsilon^G$  values resulting from different approaches are the same, while the  $\epsilon^P$  values resulting from different approaches are quite different because the current mismatch due to gate misalignment was considered in all placement approaches. Most of the  $\epsilon^P$  values are negative because our proposed parasiticaware routing approach can effectively adjust the routing wirelength to further reduce the current mismatch resulting from parasitic resistance. Consequently, it is necessary to apply both parasitic-aware placement and routing for better current matching, and our parasitic-aware placement is even better than the other two placement approaches.

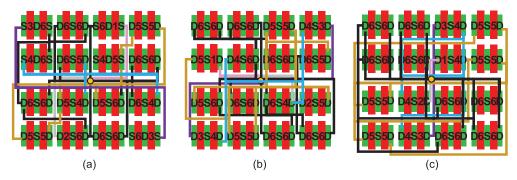

In addition to much better current ratio matching resulting from our parasitic-aware placement and routing approach, both the parasitic-unaware placement approach and our parasitic-aware approach can obtain higher dispersion degree than the approach of Lin et al. [2011] in all circuits. We did not compare the layout area because the layout area resulting from different approaches for each circuit is the same. The runtimes based on three different approaches are similar. Figures 12(a)–(c) show the resulting common-centroid FinFET arrays of CM5 generated by different approaches, respectively.

39:18 P.-H. Wu et al.

Table IV. Comparisons of Simulated Current Ratio, Current Mismatch Resulting from the Impact of Gate Misalignment (" $\epsilon^{Gn}$ ), Current Mismatch Resulting from the Impact of Parasitic Resistance (" $\epsilon^{Pn}$ ), Total Current Mismatch (" $\epsilon = \epsilon^G + \epsilon^{Pn}$ ), Dispersion Degree (" $\rho$ "), and Runtime ("T") for Lin et al.'s and Our Approaches

| Mismatch (" $\epsilon = \epsilon^{o} + \epsilon^{e}$ "), Dispersion Degree (" $\rho$ "), and Huntime ("1") for Lin et al.'s and Our Approaches |                                |                |                |              |          |       |                                              |                                  |                         |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|----------------|--------------|----------|-------|----------------------------------------------|----------------------------------|-------------------------|--|

| Lin et al. [2011] + our parasitic-aware routing                                                                                                |                                |                |                |              |          |       |                                              |                                  |                         |  |

|                                                                                                                                                |                                |                |                |              |          | $T_1$ | Comparison (%)                               |                                  |                         |  |

| Circuits                                                                                                                                       | Simulated current ratio        | $\epsilon_1^G$ | $\epsilon_1^P$ | $\epsilon_1$ | $\rho_1$ | (s)   | $\epsilon_1$                                 | $\rho_1$                         | $T_1$                   |  |

| CM1                                                                                                                                            | 1:1                            | 0.00           | 0.00           | 0.00         | 0.90     | 0.00  | -                                            | -                                | -                       |  |

| CM2                                                                                                                                            | 1:1:2.19                       | 0.21           | -0.01          | 0.20         | 2.60     | 0.01  | -                                            | -                                | -                       |  |

| CM3                                                                                                                                            | 1:1:2.17:4.37                  | 0.41           |                |              | 5.26     | 0.01  | -                                            | -                                | -                       |  |

| CM4                                                                                                                                            | 1:1:2.17:4.39:8.06             | 0.62           | -0.05          | 0.57         | 8.96     | 0.02  | -                                            | -                                | -                       |  |

| CM5                                                                                                                                            | 1:1:2.14:4.36:8.10:17.14       | 0.88           | -0.14          | 0.73         | 12.85    | 0.05  | -                                            | -                                | -                       |  |

| CM6                                                                                                                                            | 1:1:2.14:4.39:8.12:            | 1.14           | -0.13          | 1.01         | 18.10    | 0.26  | -                                            | -                                | -                       |  |

|                                                                                                                                                | 17.25:33.20                    |                |                |              |          |       |                                              |                                  |                         |  |

| CM7                                                                                                                                            | 1:1:2.23:4.44:8.29:            | 1.42           | 0.13           | 1.55         | 24.14    | 0.28  | -                                            | -                                | -                       |  |

|                                                                                                                                                | 17.54 : 34.40 : 69.83          |                |                |              |          |       |                                              |                                  |                         |  |

| CM8                                                                                                                                            | 1:1.11:2.17:4.13:8.45:         | 1.69           | 0.26           | 1.96         | 28.10    | 1.04  | -                                            | -                                | -                       |  |

|                                                                                                                                                | 18.21 : 36.06 : 71.00 : 143.29 |                |                |              |          |       |                                              |                                  |                         |  |

| Т                                                                                                                                              | The parasitic-unaware placemen | nt app         | roach [        | Wu et        | al. 20   | 15] + | our parasiti                                 | c-aware rou                      | ting                    |  |

|                                                                                                                                                |                                |                |                |              |          | $T_2$ |                                              | omparison (                      |                         |  |

| Circuits                                                                                                                                       | Simulated current ratio        | $\epsilon_2^G$ | $\epsilon_2^P$ | $\epsilon_2$ | $ ho_2$  | (s)   | $\frac{\epsilon_2 - \epsilon_1}{\epsilon_1}$ | $\frac{\rho_2-\rho_1}{\rho_1}$   | $rac{T_2-T_1}{T_1}$    |  |

| CM1                                                                                                                                            | 1:1                            | 0.00           | 0.00           | 0.00         | 0.90     | 0.00  | 0.00                                         | 0.00                             | 0.00                    |  |

| CM2                                                                                                                                            | 1:1:2                          | 0.21           | -0.21          | 0.00         | 2.60     | 0.01  | 0.00                                         | 0.00                             | 0.00                    |  |

| CM3                                                                                                                                            | 1:1:2.01:4.10                  | 0.41           | -0.33          | 0.08         | 5.26     | 0.02  | -78.26                                       | 0.00                             | 33.33                   |  |

| CM4                                                                                                                                            | 1:1:1.9883:4.06:8.23           | 0.62           | -0.44          | 0.17         | 9.11     | 0.04  | -69.79                                       | 1.70                             | 100.00                  |  |

| CM5                                                                                                                                            | 1: 1: 1.99: 4.06: 8.25: 16.76  | 0.88           | -0.52          | 0.36         | 13.04    | 0.08  | -50.63                                       | 1.43                             | 57.14                   |  |

| CM6                                                                                                                                            | 1:1:2.10:4.18:8.21:            | 1.14           | -0.56          | 0.58         | 19.18    | 0.28  | -42.59                                       | 5.95                             | 6.97                    |  |

|                                                                                                                                                | 16.79 : 33.78                  |                |                |              |          |       |                                              |                                  |                         |  |

| CM7                                                                                                                                            | 1:1:2.08:4.23:8.27:            | 1.42           | -0.36          | 1.06         | 24.60    | 0.32  | -31.95                                       | 1.87                             | 13.64                   |  |

|                                                                                                                                                | 17.15 : 34.44 : 68.96          |                |                |              |          |       |                                              |                                  |                         |  |

| CM8                                                                                                                                            | 1:1:2.02:4.09:8.29:            | 1.69           | -0.42          | 1.27         | 30.51    | 1.39  | -34.90                                       | 8.57                             | 33.20                   |  |

|                                                                                                                                                | 16.93:34.08:68.32:137.15       |                |                |              |          |       |                                              |                                  |                         |  |

|                                                                                                                                                | Our parasitic                  | -awar          | e place        | ment         | and rot  | ıting | approach                                     |                                  |                         |  |

|                                                                                                                                                |                                |                |                |              |          |       | Co                                           | omparison (                      | %)                      |  |

|                                                                                                                                                |                                |                |                |              |          | $T_3$ | $\epsilon_3 - \epsilon_1$                    | $\rho_3-\rho_1$                  | $\frac{T_3-T_1}{T_1}$   |  |

| Circuits                                                                                                                                       | Simulated current ratio        | $\epsilon_3^G$ | $\epsilon_3^P$ | €3           | $\rho_3$ | (s)   | $(\frac{\epsilon_3}{\epsilon_2})$            | $(\frac{\rho_1}{\rho_3-\rho_2})$ | $(\frac{T_3-T_1}{T_1})$ |  |

|                                                                                                                                                |                                | -              | -              |              |          |       |                                              | P2                               | T <sub>2</sub>          |  |

| CM1                                                                                                                                            | 1:1                            | 0.00           |                | 0.00         | 0.90     | 0.00  |                                              | 0.00 (0.00)                      | 0.00 (0.00)             |  |

| CM2                                                                                                                                            | 1:1:2                          | 0.21           |                |              | 2.60     | 0.01  | 0.00 (0.00)                                  |                                  | 0.00 (0.00)             |  |

| CM3                                                                                                                                            | 1:1:2:4.06                     | 0.41           | -0.36          | 0.05         | 5.27     | 0.02  | -85.84                                       | 0.33                             | 33.33                   |  |

| OB T 4                                                                                                                                         | 1 1 100 400 001                | 0.00           | 0.40           | 011          | 0.00     | 0.04  | (-34.84)                                     | (0.33)                           | (0.00)                  |  |

| CM4                                                                                                                                            | 1:1:1.99:4.03:8.21             | 0.62           | -0.48          | 0.14         | 8.96     | 0.04  | -75.73                                       | 0.03                             | 100.00                  |  |

| CIME                                                                                                                                           | 1.1.100.400.007.1044           | 0.00           | 0.00           | 0.10         | 10 17    | 0.00  | (-19.67)                                     | (-1.64)                          | (0.00)                  |  |

| CM5                                                                                                                                            | 1:1:1.99:4.03:8.07:16.44       | 0.88           | -U.69          | 0.19         | 13.17    | 0.08  | -73.83                                       | 2.45                             | 57.14                   |  |

| CIMO                                                                                                                                           | 1.1.000.410.000                | 1 1 4          | 0.70           | 0.41         | 10.10    | 0.00  | (-46.98)                                     | (1.00)                           | (0.00)                  |  |

| CM6                                                                                                                                            | 1:1:2.06:4.13:8.30:            | 1.14           | -0.73          | 0.41         | 19.18    | 0.29  | -59.06                                       | 5.94                             | 10.55                   |  |

| CIME                                                                                                                                           | 16.68:33.12                    | 1 40           | 0.00           | 0.50         | 04.07    | 0.00  | (-28.70)                                     | (0.00)                           | (3.35)                  |  |

| CM7                                                                                                                                            | 1:1:2.08:4.13:8.22:            | 1.42           | -0.90          | 0.52         | 24.37    | 0.33  | -66.38                                       | 0.92                             | 17.00                   |  |

| CIME                                                                                                                                           | 16.36 : 33.14 : 65.95          | 1.00           | 1.00           | 0.40         | 20.00    | 1 40  | (-50.59)                                     | (-0.94)                          | (2.95)                  |  |

| CM8                                                                                                                                            | 1:1:2.01:4.03:8.02:            | 1.69           | -1.28          | 0.42         | 30.32    | 1.40  | -78.74                                       | 7.90                             | 35.00                   |  |

|                                                                                                                                                | 16.05 : 32.91 : 64.92 : 130.80 |                |                |              |          |       | (-67.34)                                     | (-0.62)                          | (1.35)                  |  |

Fig. 12. The common-centroid FinFET layouts of CM5, which result from (a) the approach of Lin et al. [2011], (b) the parasitic-unaware placement approach, and (c) our parasitic-aware placement approach, respectively.

Table V. Comparisons of Simulated Current Ratio, Current Mismatch (" $\epsilon$ ") and Runtime ("T") based on the Parasitic-Unaware Routing and Our Parasitic-Aware Routing

|                                 | Our parasitic-aware placement approach + parasitic-unaware routing |                                      |                                          |                                                   |                                      |                                                                                     |                                          |

|---------------------------------|--------------------------------------------------------------------|--------------------------------------|------------------------------------------|---------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------|

|                                 |                                                                    |                                      |                                          |                                                   | $T_4$                                | $T_4$ Comparison (%)                                                                |                                          |

| Circuits                        | Simulated current ratio                                            | $\epsilon_4^G$                       | $\epsilon_4^P$                           | $\epsilon_4 = \epsilon_4^P + \epsilon_4^G$        | (s)                                  | $\epsilon_4$                                                                        | $T_4$                                    |

| CM1                             | 1:1                                                                | 0.00                                 | 0.00                                     | 0.00                                              | 0.00                                 | -                                                                                   | -                                        |

| CM2                             | 1:1:2                                                              |                                      | -0.21                                    | 0.00                                              | 0.00                                 | -                                                                                   | -                                        |