Small transistors necessitate big changes, in the way digital circuits are modeled and optimized for manufacturability, and new strategies for logic, memory, clocking and power distribution.

By BENTON H. CALHOUN, Member IEEE, YU CAO, Member IEEE, XIN LI, Member IEEE, KEN MAI, Member IEEE, LAWRENCE T. PILEGGI, Fellow IEEE, ROB A. RUTENBAR, Fellow IEEE, AND KENNETH L. SHEPARD, Senior Member IEEE

**ABSTRACT** | Well-designed circuits are one key "insulating" layer between the increasingly unruly behavior of scaled complementary metal-oxide-semiconductor devices and the systems we seek to construct from them. As we move forward into the nanoscale regime, circuit design is burdened to "hide" more of the problems intrinsic to deeply scaled devices. How this is being accomplished is the subject of this paper. We discuss new techniques for logic circuits and interconnect, for memory, and for clock and power distribution. We survey work to build accurate simulation models for nanoscale devices. We discuss the unique problems posed by nanoscale lithography and the role of geometrically regular circuits as one promising solution. Finally, we look at recent computer-aided design efforts in modeling, analysis, and optimization for nanoscale designs with ever increasing amounts of statistical variation.

INVITED PAPER

KEYWORDS Clock distribution; complementary metal-oxidesemiconductor (CMOS); device scaling; digital circuits; lithography; logic; manufacturability; memory; optimization; power distribution; regular circuit fabrics; statistical variability; yield

## I. INTRODUCTION

For four decades, Moore's law [1] has driven the worldwide semiconductor industry. The expectation of continued device scaling drove fundamental research on physics, materials, devices, interconnect, and—of principal interest in this paper—integrated circuits, leading to an enormous and diverse range of commercial electronics. As we move into the era of nanoscale devices, however, scaling-as-usual is under significant duress.

The problems are, of course, well known. As we move to more atomistic dimensions, simple scaling eventually stops. The devices are smaller, but many aspects of their performance deteriorate: leakage increases, gain decreases, and sensitivity to unavoidable small fluctuations in the manufacturing process rises dramatically. Power and energy have become the key limiters on many new designs. We can no longer rely on experience with a few "worst case" process corners to predict worst case behavior for these technologies. Nothing is deterministic any longer: most relevant parameters are statistical; many exhibit complex correlations and distressingly wide variances. The rising costs associated with fabricating circuits in such scaled technologies (e.g., mask costs) only exacerbate these problems of predictability.

Nevertheless, we see significant opportunities in these challenges. Our goal in this paper is to survey briefly how circuit design is both affected by, and successfully responding to, these challenges. In a very real sense, welldesigned circuits are one key "insulating" layer between the increasingly unruly and nonideal behavior of scaled devices and the systems we seek to construct from them. As we move forward into the nanoscale regime, further into the (rather ominously denoted) "end of the roadmap"

Manuscript received February 2, 2007; revised August 17, 2007. This work was supported in part by the Center for Circuit and System Solutions under the Focus Center Research Program.

**B. H. Calhoun** is with the Department of Electrical and Computer Engineering, University of Virginia, Charlottesville, VA 22904 USA (e-mail: bcalhoun@virginia.edu). **Y. Cao** is with the Department of Electrical Engineering, Arizona State University, Tempe, AZ 85287 USA (e-mail: yu.cao@asu.edu).

X. Li, K. Mai, L. T. Pileggi, and R. A. Rutenbar are with the Department of Electrical and Computer Engineering, Carnegie-Mellon University, Pittsburgh, PA 15213 USA (e-mail: xinli@cec.cmu.edu; kenmai@cec.cmu.edu; pileggi@cec.cmu.edu; rutenbar@cec.cmu.edu).

K. L. Shepard is with the Department of Electrical Engineering, Columbia University, New York, NY 10027 USA (e-mail: shepard@ee.columbia.edu).

Digital Object Identifier: 10.1109/JPROC.2007.911072

for silicon, circuit design is increasingly burdened to "hide" more and more of the problems intrinsic to deeply scaled devices. How this is being accomplished is the subject of this paper.

Given space limitations, we restrict our focus to digital circuits. (Companion papers in this issue address the problem from the analog perspective; see [2] for example.) We survey a range of novel circuit ideas that respond to the particular pressures of scaling. This paper is organized as follows. Section II discusses logic circuits and interconnect and chip-level problems, such as clock and power distribution. Section III discusses the ongoing evolution of compact device models (i.e., models suitable for use in SPICE-type simulation engines), which are an essential link from the new physics of scaled devices to any practical application of these devices. Section IV surveys the unique problems of static RAM (SRAM) memory circuits; these are often the very first circuits prototyped in any new technology, and the decision to move to a new scaled node is often held hostage to our ability to make SRAM designs work successfully. Section V examines challenges to application-specific integrated circuit (ASIC) design flows. The principal concern here is lithography—our ability to print patterns predictably, and its growing impact on manufacturability. The principal strategy to "hide" lithographic problems is the use of highly regular layout strategies. Section VI surveys recent computer-aided design (CAD)-oriented work on statistical circuit design-how we can model, analyze, and optimize circuits in the face of growing statistical variability. Section VIII summarizes the changes in current design practice at the circuit/logic/ memory interface that we believe will be necessary to address these various scaling challenges. Section VIII offers concluding remarks.

## II. LOGIC AND INTERCONNECT, CLOCK, AND POWER DISTRIBUTION CHALLENGES

Traditional Dennard scaling [3] no longer applies to technologies below 0.13  $\mu$ m due to the nonscaling of the thermal voltage (kT/q) and the built-in voltage  $V_{\rm bi}$ . As a result, traditional parameters of device scaling, such as the supply voltage  $V_{\rm DD}$  and threshold voltage  $V_{\rm T}$ , are no longer fixed numbers for a given technology node but design parameters that must be optimized to trade off energy, delay, and noise margins and contend with issues of variability.<sup>1</sup> New device structures at the end of the complementary metal-oxide-semiconductor (CMOS) roadmap [5] (the modeling challenges of which are described in Section III) will create even more device-level parameters that will have to be included in these circuit optimizations. Furthermore, digital circuits can no longer be optimized without concern for the function they are performing or workload with which they are contending [6]. Increasingly adaptive circuit structures must be employed to ensure close to optimal operation with variability in workload, supply voltage, temperature, and process.

### A. Logic and Interconnect

Energy-delay optimizations are the most fundamental in digital circuit design. Traditionally, these tradeoffs have been considered with an energy-delay product metric [7]. More recently, it has been recognized that the optimization that is most likely to be performed is actually to minimize the energy with a fixed performance requirement (or maximize performance with a fixed energy). This optimization strategy makes immediately evident the fact that high-performance requirements translate into large amounts of energy for small performance gains while lowenergy requirements translate into large amounts of performance degradation for small energy gains. Both the delay and energy required to complete a given task are functions of many variables  $(x_i)$ , including supply voltage, threshold voltage, logic family or circuit style, circuit sizing, pipeline depth, and other microarchitectural features: delay  $D(x_i)$  and energy  $E(x_i)$ . Introducing a Lagrange multiplier *S*, the function to be optimized (in the case of delay-constrained energy minimization) is given by

$$F(x_{i}, S) = E(x_{i}) + S(D(x_{i}) - D_{0})$$

(1)

where  $D_0$  is the target delay constraint. Optimization of this leads to the conclusion that if

$$S_{i} = \frac{\partial E / \partial x_{i}}{\partial D / \partial x_{i}} \bigg|_{x_{i} = x_{0}}$$

<sup>(2)</sup>

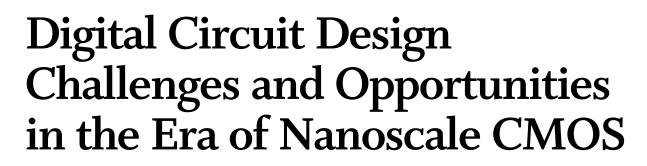

then all of the  $S_i$  must be the same for all parameters in the optimization; that is, the marginal cost in energy for a change in delay must be the same for all parameters [8]–[10], as shown in Fig. 1.

Many low-power techniques simply eliminate power that is being wasted, improving energy at no performance cost. The best example of this is clock gating. Other techniques, such as parallelism, can improve performance at minimal energy cost [11]. Because of the large variability present in workload, most low-power techniques are really ones that adapt circuits to this variability allowing "reoptimization" with changing requirements such as dynamic frequency and voltage scaling [12], [13], body-biasing for  $V_{\rm T}$  adjustment [14], and leakage control switches.

Wires also remain a significant challenge in the design of digital integrated circuits. Over the past few decades, improvements in integrated circuit density and performance

<sup>&</sup>lt;sup>1</sup>Channel length *L*, which is usually chosen as minimum for most digital circuits, is emerging as an optimization parameter as well, as  $V_{\rm T}$  and output conductance (drain-inducted barrier lowering) become strongly dependent on *L* [4].

**Fig. 1.** Delay-constrained energy minimization to meet delay constraint *D*<sub>0</sub>. Minimum energy occurs at the point at which the sensitivities *S*<sub>1</sub> are the same for all parameters of interest.

have been achieved by scaling down transistors. Latency (rather than pipelined throughput) of on-chip wires is important for many applications such as buses between cache memories and processors [15]. Although the latencies of local interconnects scale accordingly, the delay per unit length of on-chip wires, as determined by a diffusive *RC*-limited response and as measured relative to gate delays, approximately doubles every technology generation [16], [17] as wire resistances per unit length increase and gate delays decrease with scaling. Furthermore, these wire delays (*D*) grow quadratically with wire length  $D \propto R_{\rm wire}C_{\rm wire}L^2$ . Wire bandwidths, which are inversely proportional to *D*, also degrade.

Buffers (or repeaters) are traditionally added to make the interconnect latency linear with wire length, with simple relationship guiding an optimal number of repeaters (and their sizing) to minimize interconnect delay [16]. Wide wires can be used to improve overall latency, requiring fewer numbers of repeaters of larger area (to drive the larger wire capacitance) to achieve a delay optimal solution. Overall energy-per-bit and routing density, however, degrade with wire widening [16].

Interconnect latency, bandwidth density (bits per second per unit routing width), and energy-per-bit for on-chip wires can be improved with more intelligent circuits, moving beyond the use of a full-rail RC-limited interconnect buffered by CMOS inverters for on-chip communications. On-chip RC links that run low-swing can provide an order of magnitude improvement in energy-perbit, but generally do so at the cost of degraded latency [18], [19]. Other circuit approaches take advantage of transmission line effects to simultaneously improve latency and energy-per-bit, including pulsed current-model signaling [20] and the use of distributed loss compensation [21].

The clock and power networks in digital integrated circuits present important additional challenges and are considered in detail in the following two sections.

#### **B.** Clock Distribution

Clock distribution remains an important challenge in the design of large-scale digital chips, a challenge that has only grown with technology scaling. Most modern clock distributions are "single wire," meaning that only a single clock phase is distributed globally although multiple clock phases are often created locally with clock "shaper," clock "chopper," or clock buffer circuits. The challenge of clock distribution is to distribute the clock simultaneously everywhere (no skew) and periodically everywhere (no jitter) using minimal power and wiring resources and being as impervious as possible to process variations and supply noise. The typical "gain" of a clock distribution network, as measured by the ratio of the clock load capacitance to the capacitance driven from the phase-locked-loop reference, is more than 10<sup>5</sup>.

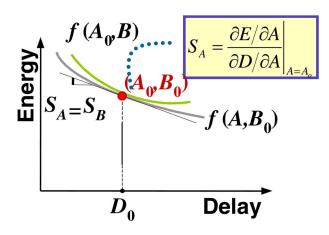

Clock distributions are typically designed as trees or tree-driven grids. Tree distributions consume the minimum wiring resources and provide the minimum wiring capacitance (and consequently represent the low-power solution). They unfortunately suffer from the most sensitivity to spatial variation (in either load capacitance or buffer strength). Active deskewing circuits [22] are one way to address this limitation for trees but add to clock latency. The addition of a grid to the tree [23] also helps to amortize this variation at the expense of additional wiring resources and wiring capacitance. Fig. 2 shows global clock latencies as reflected in published data from two leading microprocessor companies. The "circles" represent treebased designs augmented with active deskewing circuits, while the "squares" represent a tree-driven-grid design. The former has significantly higher latency.

Clock distributions are becoming more challenging with technology scaling because of several factors. The size of a typical synchronous domain is not decreasing as more

Fig. 2. Global clock latencies from published microprocessor designs; circles are tree-based clocks with active deskewing; squares are tree-driven grid clocks.

function is integrated onto chips with the availability of additional transistors. The relative nonscaling of wire delay and the increasing amount of capacitance per unit area exacerbate clock latency and increase the required gain of the clock network. Variability in process, temperature, and voltage, both temporal and spatial, make skew and jitter management increasingly difficult. Growing clock latency (as reflected in Fig. 2) presents challenges in the presence of variability. For example, for a four-cycle clock latency, a 10% delay variation will result in skew and jitter that is 40% of the clock cycle time (assuming a tree distribution, all silicon delay, and no common paths between clock and data). Jitter from power supply noise can also vary across the chip and change every cycle.

These challenges have led to a search for circuit alternatives for clock distribution networks. Resonant clock distributions have been proposed as an alternative clock technology and have shown promise in reducing clock timing uncertainty and power dissipation [24]. Standingwave clock distributions have been implemented at both the board level [25] and chip level [26]. These designs achieve low-skew and low-jitter clocks and can save power due to the resonance between the clock capacitance and the clock wire inductance. Standing-wave clock distributions must, however, contend with nonuniform clock amplitude, which may result in skew or make local clock buffering more complex. Traveling-wave clock distributions [27] use coupled transmission line rings to generate a low-skew and low-jitter clock and also benefit from the power advantage of resonance. Nonuniform phase across the distribution makes integration with existing local clocking methodologies more difficult, however.

Resonant-load global clock distribution allows the distribution of uniform-phase uniform-amplitude clock waveforms by augmenting traditional tree-driven grids with a set of spiral inductors, which resonates with the clock load capacitance [28], [29]. A sizable portion of the jitter reduction and power savings results from reducing the strength of the clock buffers driving the resonant load, exploiting the proclivity of the network to sustain a tone at the target resonant frequency, resulting in a nearly sinusoidal clock signal. Sinusoidal clocks are however generally undesirable because of slower signal transition times, which exacerbate timing uncertainty at single-ended local clock buffers in the presence of process, voltage, and temperature variations. Another drawback associated with the resonant-load global clock distribution is the requirement for large on-chip decoupling capacitance to serve as a charge reservoir.

These issues are addressed in an improved resonant clock design based on a differential oscillator (DDO) global clock network [30], [31]. The differential distribution is a free-running oscillator injection-locked to an external reference with symmetric inductors placed between the two clock phases, eliminating the need to add large capacitors to the clock. At resonance, the DDO global clock is uniform in both amplitude and phase across the distribution. Differential detection at the local clock buffers reduces skew and jitter due to power-supply noise, process variations, and other common-mode noise sources, mitigating the disadvantages of the more sinusoidal clocks characteristic of resonant distributions.

# C. Power Supply Distribution, Regulation, and Measurement

With technology scaling and increasing performance requirements, the power levels to the chip are increasing while the supply voltages are decreasing. This leads to a rapid increase in the supply current requirements. With increasing current transients and average current levels, more on-chip decoupling capacitance is required while the resistance and inductance of the power distribution network (including on-chip wiring, pins, sockets, and connectors) must be kept stringently low for supply integrity. Operating at supply voltages below 1 V, 90-nm (and below) technologies still demand in excess of 100 W of power in the largest chips, such as high-performance microprocessors. The demands for no more than 10% power supply variation require impedances on the power distribution of less than 1 m $\Omega$ , putting unprecedented demands on the power distribution.

On-chip measurement of the power supply is an important first step in understanding the nature of power supply noise. On-chip samplers [32] have been used to make simple sampling oscilloscopes [33] to measure on-chip supply noise. Measurements on real microprocessors have also been demonstrated [34].

Active on-chip regulation, similar to that employed for on-board voltage regulation modules, as implemented with high-bandwidth push-pull linear regulators could help to reduce on-chip decoupling capacitance requirements. Other circuit approaches have been considered to reduce current demands in the power distribution outright. One such approach [35], [36] achieves implicit on-chip dc-dc conversion by "stacking" logic and recycling charge from one domain to another. Logic is stacked n-high and operated at an  $nV_{DD}$  supply. By stacking the logic domains n high, the on-chip current demands on the power and ground networks are also reduced by a factor of n over the case of all of the domains running in parallel at  $V_{\rm DD}$ . Due to inevitable charge mismatches between the domains of the stack, the internal node voltages require regulation, which can be achieved by the addition of push-pull linear regulators and decoupling capacitors.

## **III. DEVICE MODELING CHALLENGES**

Device models are the critical interface between the underlying technology and integrated circuit design. Coupled with circuit simulation tools, they significantly improve design productivity, providing insight into the relationship between design choices and circuit performance. In order to

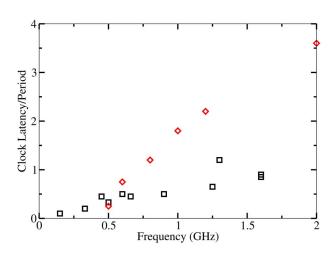

Fig. 3. The scaling trend of ON and OFF current for traditional bulk CMOS technology [1].

guarantee design quality, device models should be scalable with latest technology advances, accurate across a wide range of process and operation conditions, and efficient for large-scale computation. As CMOS technology scales into the sub-50-nm regime, these modeling demands are tremendously challenged, especially by the introduction of alternative device materials and structures, as well as the ever-increasing amount of process variations.

The scaling of traditional bulk CMOS structure is slowing down in recent years as fundamental physical and process limits are rapidly approached. For instance, short-channel effects, such as drain-induced barrierlowering (DIBL) and threshold voltage ( $V_T$ ) rolloff, severely increase leakage current and degrade the ratio of  $I_{\rm on}/I_{\rm off}$  (Fig. 3) [37]. To overcome these difficulties and continue the path perceived by Moore's law, new materials need to be incorporated into the bulk CMOS structure, including high-permittivity (high-k) gate dielectrics, metal gate electrodes, low-resistance source/ drain, and strained channel for high mobility [38], [39]. Therefore compact models for bulk CMOS technology should be updated to capture the distinct electrical behavior of these advanced materials.

Starting from the 90-nm technology node, strain engineering has offered a new technique to enhance carrier mobility and transistor performance, since the saturation current  $I_{on}$  is proportional to the mobility ( $\mu$ ) for a shortchannel device

$$I_{\rm on} \propto \mu W C_{\rm ox} (V_{\rm gs} - V_{\rm T}).$$

(3)

From the modeling perspective, two challenges are posed for emergent design needs. First, the dependence of carrier mobility and velocity on strain and other process parameters needs to be understood [39], [40]. Presently the p-channel MOS device benefits more from the strained channel than the n-channel MOS device. This suggests a different scenario of circuit sizing. When the channel length scales down to the 10-nm regime, the MOS fieldeffect transistor carrier transport will eventually reach the ballistic limit and weakly depend on the strain

$$I_{\rm on} \propto \langle v(0) \rangle W C_{\rm ox} (V_{\rm gs} - V_{\rm T})$$

(4)

where  $\langle v(0) \rangle$  is the average velocity of carriers at the source [39], [41]. A physical mobility model is desirable to continuously describe these characteristics. The second challenge is the layout dependence induced by both the stress process and nonuniform patterns [42]. Currently empirical models exist to explain the experimental data. More physical and holistic models are required through the joint efforts of technology CAD (TCAD) simulations and compact modeling.

High-k/metal gate may be adopted for IC production as early as the 45-nm technology node. High-k dielectrics help reduce gate leakage and allow more aggressive scaling of gate dielectrics than classic silicon oxide, while the metal gate is necessary to tune the threshold voltage [38]. However, the implementation of high-k dielectrics comes at the expense of transistor reliability. The consequences include a larger amount of negative-bias temperature instability (NBTI) and faster degradation of the drain current [43], [44]. Additional compact models need to be developed to account for the instability and to support the design for reliability approach [45].

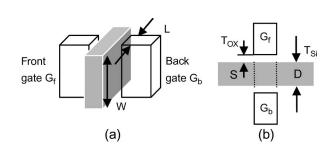

Beyond the 32-nm technology generation, more radical solutions will be vital to meet the scaling criteria of offstate leakage. The FinFET, or the double-gate device (DG), is considered as the most promising technology of choice [38], [46]. Fig. 4 illustrates the structure of a FinFET device. The FinFET device is electrostatically more robust than a bulk CMOS transistor since two gates are used to control the channel. At the 32-nm node, it may improve the  $I_{\rm on}/I_{\rm off}$  ratio by more than 100% [47]. Extensive research has been conducted to understand the underlying physics [48], [49]. Yet a compact model for DG devices, akin to the Berkeley Short channel Insulated gate field

Fig. 4. The structure of a FinFET device: (a) three-dimensional view and (b) the top view of both.

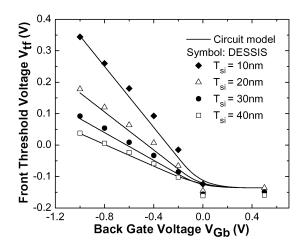

Fig. 5. The coupling between  $V_{\rm Tf}$  and  $V_{\rm Gb}$  in a FinFET device.

effect transistor Model (BSIM) and Pennsylvania State University-Philips (PSP) model [50] for the bulk CMOS transistor, has not been standardized. Alternatively, an equivalent subcircuit model is proposed in [47], which models a FinFET device as two silicon-on-insulator (SOI) transistors with common source and drain. The unique property of a FinFET device is the electrical coupling between front and back transistors. Specifically, the threshold voltage of the front transistor ( $V_{\rm Tf}$ ) is controlled by the back gate voltage ( $V_{\rm Gb}$ ), through the partition between the gate oxide capacitance ( $C_{\rm oxb}$  and  $C_{\rm oxf}$ ) and the silicon body capacitance ( $C_{\rm Si}$ )

$$\partial V_{\rm Tf} / \partial V_{\rm Gb} = -(C_{\rm Si} \| C_{\rm oxb}) / C_{\rm oxf}.$$

(5)

Fig. 5 evaluates the model against the results from TCAD simulations for a variety of  $T_{\rm Si}$  [51]. Such an approach is compatible with SPICE simulators and enables early stage design exploration for digital applications.

While technology scaling can be extended with alternative materials and structures, CMOS technology will eventually reach the ultimate limits that are defined by both physics and the fabrication process. One of the most profound physical effects will result from the vastly increased parameter variations due to manufacturing and environmental factors [52]. These variations exacerbate design margins, degrade the yield, and invalidate current deterministic design methodologies [53]. To maintain design predictability with those extremely scaled devices, compact models should be extended from the traditional corner-based approach to a suite of modeling efforts, including extraction methods, the decoupling of variation sources, and highly efficient strategies for the statistical design paradigm [54].

Process variations usually manifest themselves as parameter fluctuations in nanoscale transistors, such as the channel length, threshold voltage, and transistor parasitics. By characterizing appropriate test structures, these variations need to be correctly extracted and embedded into a transistor model file, such that a circuit designer can perform statistical analysis and optimization to mitigate performance variability. A rigorous extraction method further helps shed light on the mechanism of variations.

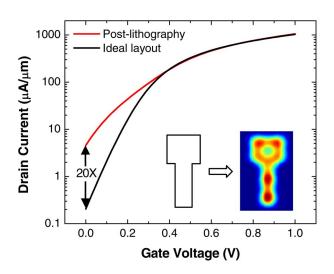

The main modeling challenge under variations is to identify systematic variation components, develop predictive models for performance analysis, and incorporate them into design tools. One example of predictable variations is the layout-dependent change induced by subwavelength lithography or local stress engineering [54], [55]. As the semiconductor industry migrates to subwavelength lithography, there is a growing difference between the layout viewed in the design stage and that after the manufacturing process (Fig. 6). The distortion of the layout shape may lead to more than 20 times increase in off-state leakage, as demonstrated from the TCAD simulation at the 65-nm technology node (Fig. 6). This phenomenon demands the construction of compact models beyond the level of individual devices. The local environment should be included to account for the interaction between design, performance, and manufacturability.

Statistical analysis under variations inevitably increases the cost of computation. This problem is further exacerbated as future digital design becomes bigger and more complex. Therefore, the simplicity of device models is key to a statistical design flow. Current compact transistor models consist of a large number of parameters and complicated equations to capture many physical mechanisms for a short-channel device, but significantly slowing down the simulation speed. At the other extreme end, lookup table based approaches are much more efficient; however, their empirical nature limits the scalability to process

Fig. 6. Subwavelength lithography causes a nonrectangular gate shape and the significant increase in leakage.

variations. In the context, a desirable solution could be a behavior model for nanoscale CMOS devices, with sufficient fidelity to parameter variations [56].

In nanoscale design, compact device modeling plays an even more essential role, driven by the increasingly complex and diverse nature of the underlying technology. Solutions to those modeling challenges will provide early comprehension of process choices and design opportunities.

## IV. SRAM MEMORY DESIGN CHALLENGES

For the foreseeable future, SRAM will likely remain the embedded memory technology of choice for many microprocessors and systems on chips (SoCs) due to its speed and compatibility with standard logic processes. Further, the number and size of SRAM arrays on these chips will increase as more of the memory hierarchy is integrated onto the processing die. The embedded memory system plays a key role in determining the system performance, efficiency, and cost. However, the unique characteristics of SRAMs exacerbate a number of the previously mentioned design challenges, particularly variability.

SRAMs contain a large number of at- or near-minimum sized devices, use circuits based on path-matching and/or race conditions, and use low-swing signaling for better performance and lower power. Full custom design is often necessary to achieve the desired bit density, power, and performance. Fortunately, given the large amount of replication in SRAM design, full custom design is still feasible. Due to the large amount of design replication and SRAM's overall criticality in modern microprocessors and SoCs, they are one of the first designs ported to a new technology node and often become the design driver for identifying and addressing emerging circuit challenges in a new process.

SRAM design is becoming increasingly challenging with each new technology node. The most pressing issues arising from scaling are increased static power, cell stability concerns, reduced operating margins, robustness and reliability, and testing. Increasing inter- and intradie variability exacerbates each of these problems, particularly in the cell arrays with their large numbers of near-minimum sized devices. Due to the large number of devices in SRAMS, designs must take into account the extreme tails of the device distributions (i.e.,  $5\sigma$  or greater) to achieve acceptable yield rates.

## A. Power

As scaling has increased device leakage currents,<sup>2</sup> the static power dissipation of SRAM arrays in both active and sleep modes has become a serious concern, especially given the increasingly large fraction of SoC and microprocessor dies dedicated to embedded SRAM. Variations

<sup>2</sup>http://www.sia-online.com.

induce a large spread of leakage currents for bitcells across the array. For example, since subthreshold leakage current depends exponentially on the threshold voltage ( $V_T$ ), the cells at the lower end of the  $V_T$  variation distribution tend to set the overall leakage power.

Using higher  $V_{\rm T}$  devices in the SRAM bitcells is a first step in keeping leakage power within reasonable limits [59]. Other options exist for further reducing leakage in memory arrays. Body biasing can be used to reduce standby leakage power [60], [61]. Also, standby leakage power can be lowered significantly by reducing the voltage drop across the cross-coupled inverters in the bitcell. This approach has been implemented by lowering  $V_{\rm DD}$  [62]–[65], raising  $V_{\rm SS}$  [66]–[70], or both [71]. There is a limit, however, to the extent by which the voltage can be decreased before the data in the bitcell is lost. The data retention voltage (DRV) is the lowest voltage at which a bitcell still retains its data [65].

Again, variations produce a distribution in the DRV for cells across an SRAM array. Most existing implementations simply apply a voltage guard band by limiting the extent of the voltage scaling to account for worst case variation. Given the large spread of DRV values, this practice can limit the achievable savings. The use of canary replica cells [72] can allow aggressive voltage reduction to near the DRV. However, replicas of any sort are more difficult to produce due to the presence of process variations. In particular, traditional sizing-based replicas become less reliable because of variation.

## B. Cell Stability

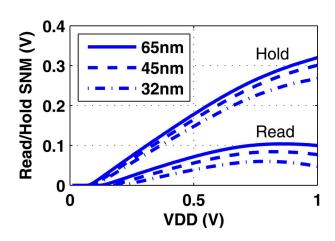

One of the most serious threats to long-term SRAM viability in scaled processes is cell stability, how to maintain both cell read stability and writeability. The read static noise margin (SNM) is often used as a measure of the cell read stability [73] and Fig. 7 shows that read SNM degrades rapidly at lower  $V_{\rm DD}$  and with scaling.

**Fig. 7.** Read SNM versus  $V_{DD}$  using predictive technology models.

Furthermore, the larger variation inherent in advanced technologies creates a greater spread in the SNM distribution. Read SNM rapidly becomes a serious limiter of voltage and technology scaling [74], [75].

Write margin degrades in a similar fashion. Exacerbated by large process variations, the write drivers and access transistors of cells with insufficient write margin cannot overpower the load inside the cell, preventing successful write operation. This effect gets worse at low voltage, and it can actually be the primary limitation to voltage scaling [75], [76].

In the short term, there are a number of techniques to extend the viability of the traditional 6T SRAM cell to lower supply voltages and newer technologies. Almost all cutting edge SRAMs use a variety of voltage knobs to compensate for variations. For example, lower bitline precharge voltage [76], [78], boosted cell voltage [79]–[81], and write after read [78] improve or bypass read SNM. For write accesses, boosted wordline voltage [75], [81] or collapsed cell voltage [75], [76], [80], [81] improve the write margin. An additional complicating factor in cell design is the printability of subdesign rule "pushed" cell layouts, which further constrains viable cell sizings and topologies (see Section V).

However, in the long term, whether the 6T cell is the optimal cell topology choice in nanoscale processes is still an open question. Other options, such as using alternative bitcells [77] or dual-port bitcells with read buffers [75], [81], can eliminate the read SNM problem. There are a number of attractive alternate cell topologies that, while they do require more area and/or devices per cell, may achieve higher overall bit density because they require less peripheral circuitry. Using alternate or emerging technologies offers some promising solutions as well. For example, process variations are less severe in SOI than in bulk CMOS [59], and FinFET-based SRAM cells can offer improved characteristics [83].

#### C. Operating Margins

In addition to the stability of a single cell decreasing, the operating margins of the memory as a whole are decreasing due to scaling effects on the cell arrays and peripheral circuits. Variability in the cells decreases the minimum expected  $I_{\rm on}$ . Leakage and variability increase the bitline leakage of the unselected cells, further reducing the bitline differential voltage. Designers have developed ways to reduce the "off" cell leakage onto the bitlines which include using long *L* or high- $V_{\rm T}$  devices, read bitlines precharged to less than  $V_{\rm DD}$ , leakage cancelling bitcells, and active leakage compensation [82]. Variability in the peripheral circuits also decreases the operating margin by affecting the sense amplifiers, control signal generation, and decoders.

Variability is causing sense amplifiers to have large input-referred offsets. The sense amplifier offset can be reduced in a number of ways, including using larger devices, shaping the sense enable signal, or active offset compensations [88], [89]. Alternately, large swing (e.g., half or full  $V_{\rm DD}$ ) bitlines can be used, but this comes at the cost of power and performance.

On a read, clocked sense amplifiers can be fired either from a clock edge or using a replica timing circuit. The replica timing circuit mimics the delay of the actual bitline and tracks that delay over process and environmental variations [90], which is why it is the preferred method of sense enable generation for high-performance SRAMs. However, device variations also affect the replica circuit, further decreasing the read margin. The replica circuit can be made robust to variations by simply increasing the number of replica driver cells (and proportionally increasing the replica load), but this requires a large number of replica driver cells to achieve average-case matching. Future replica circuits will require variability tolerant driver cells or a way to configure the driver cells such that they achieve average-case performance.

Decoder design will also require a rethink in nanoscale processes. Previous high-performance designs used pulsemode self-resetting logic for high-speed and low-power [90]. However, these logic styles often relied on race conditions and had numerous timing constraints. With increasing variability, these logic styles become increasingly difficult to design in a robust and manufacturable way. Also, high-performance decoders have used low- $V_{\rm T}$  devices for better performance, but leakage in these devices will contribute significantly to leakage power.

To combat these trends, future designs will likely use higher degrees of bitline segmentation to decrease the number of cells on a bitline, larger swing signaling to account for the decreased bitline differential voltages, and generally more conservative circuit design given the erosion of previously held assumptions about cell, device, and path matching. Bit density and performance will likely not scale as quickly as in past generations, given the more conservative approach to design.

#### D. Robustness and Reliability

With scaling, hard and soft errors in SRAM will increase in frequency and scope, so that a single error event is more likely to cause multiple bit failures within a single word and across multiple words [91]. There are a number of causes of soft errors including energetic particle strikes, signal or power-supply noise coupling, and erratic device behavior [84]-[86], [93]. In today's technologies, the vast majority of soft error events will result in only a single cell's being disturbed, but as we scale into the nanometer regime, single event multibit errors will become more and more likely [91]. While the failures-in-time (FIT) rate of an individual SRAM cell will remain approximately constant across process technology due to the proportionate shrinking of the cell  $Q_{crit}$  and collection area, the overall chip FIT rate will increase due to the increasing number of SRAM cells on a die [91]. Additionally, the number of SRAM cells that fall under the footprint of a single energetic particle strike will increase, since the particle strike footprint does not scale, and thus increase the likelihood of multibit upsets.

Hard errors are the result of a number of phenomena including electromigration, device wearout/aging (e.g., oxide breakdown, NBTI), and highly energetic particle strikes. Hard errors can result in large-scale data loss, such as an entire data row or column, pairs of rows or columns, or even an entire subarray [94], [95]. In deeply scaled processes, the incidence of hard error at manufacture time and in the field is expected to rise dramatically [95], [96]. This large-scale information loss and high rate of hard errors will likely overwhelm conventional memory protection techniques and threatens both the yield rate and runtime reliability of chips with large embedded memories.

Finally, inter- and intradie variability not only increases the percentage of memory cells and peripheral logic blocks that fail altogether (e.g., from insufficient read static noise margin in a 6T SRAM cell) but also increases the number of cells and peripheral logic blocks that are marginally functional and thus more susceptible to hard and soft error phenomena.

To combat hard and soft errors, designers currently employ a number of techniques, including error-correcting codes (ECCs), bit-interleaving, redundancy, and devicelevel countermeasures. Single error correct, double error detect (SECDED) ECC is widely used in modern memories for soft error protection. SECDED ECC can also be used for yield enhancement by letting the ECC code correct single-bit, manufacture-time, hard errors, but this sacrifices soft error immunity for the data words that have a preexisting hard error from manufacturing [97]-[99]. Bitinterleaving (also known as column multiplexing) is often employed for higher performance and easier layout, but in combination with ECC, it allows the correction of smallscale multibit errors that have a footprint less than or equal to the degree of interleaving. Unfortunately, the degree of bit-interleaving cannot be increased much beyond four before incurring significant performance and power penalties [100]. To map out manufacture-time hard errors and thus improve yield, modern SRAM designs use redundant rows, columns, and subarrays. Combined with built-in self-test (BIST) or built-in self-repair (BISR) mechanisms, the memories can detect and repair hard errors during both manufacturing test and in-the-field operation [101]-[103].

In addition to microarchitecture mechanisms based on error detection and rollback [105], and logic and circuitlevel mechanisms that strive to harden sensitive bit-level storage elements [106], [107], there are a number of process-level techniques to reduce soft errors such as SOI processes, explicit capacitors to increase  $Q_{\rm crit}$ , and specialized hardened processes primarily used for space applications. These techniques often require expensive additional mask layers and processing steps to implement the explicit capacitors. While effective for the error rates and types seen today, these conventional techniques will not scale to cover the high incidence of error and multibit error events that will occur in nanoscale technologies. Thus, an efficient multibit error protection scheme is necessary to ensure high efficiency, reliable operation, and high yield for future memory-intensive ICs.

Finally, memory test and design for testability will likely become primary design considerations, as the number and size of deeply embedded SRAM arrays in SoCs and microprocessors dies increase. BIST and BISR will become a necessity for these deeply embedded memory arrays. By itself, memory test is a large and critical field [108], [109], coverage of which lies outside of the scope of this designfocused paper. Yet the role of BIST/BISR circuitry will expand beyond testing for faulty/marginal circuits at manufacture time to include characterization of the die (or portion of the die) to enable postmanufacturing self-tuning of the entire die or individual components on the die. Researchers have already proposed using on-die leakage characterization circuits to guide tuning of the back bias voltage for process centering to combat interdie process variations [87]. As inter- and intradie variability becomes more pronounced, designers will likely need to incorporate more knobs for postmanufacturing tuning, and BIST/BISR circuits will play a critical role in the tuning control loop.

### E. Design Methodology, Tools, and Optimization

Given the large number of design and topology choices, as well as the necessary multidimensional optimization problem, SRAM design and optimization by hand is becoming increasingly infeasible. To find the optimal design, SRAM designers will require optimization and design tools that allow for fast exploration of the design space. These tools will need to operate at a higher level than today's transistor-level circuit optimizers (e.g., IBM's EinsTuner, Stanford's Circuit Optimization Project, CMU's ROAD, Cadence's NeoCircuit) and offer more degrees of freedom than today's memory compilers. This new class of memory design tools must offer memory synthesis capability similar to today's logic synthesis tool chain. Taking in design and process constraints along with a precharacterized set of memory circuit topologies, the tool would produce a set of memory designs along the Pareto-optimal surface. One of the primary challenges in developing this type of tool is performing design optimization across multiple levels of the design stack, from process technology to microarchitecture. Capturing a sufficiently wide range of circuit topologies to cover widely separated points in the SRAM design space (e.g., low-power designs versus high-performance designs) and different process technology choices will also pose a significant challenge.

Because robustness and yield will be key optimization goals, such a tool will also require extensive simulations under process variations. Efficient Monte Carlo simulation tools targeted at rapid exploration and sampling from the statistically rare tails of the variation distributions will be critical. Research efforts in this area include ideas from Monte Carlo mixture importance sampling [104] and the recently introduced statistical blockade technique [133], which we shall describe further in Section VI-A.

Due to the increasingly difficult design environment in scaled technologies, SRAM designers must take advantage of opportunities at all levels of the design stack, especially often overlooked solutions at microarchitecture and architecture levels. Codesign will have to occur across process technology, circuits, and microarchitecture to meet future power, area, and performance targets.

# V. CHALLENGES TO DIGITAL DESIGN FLOWS

#### A. Lithography, Manufacturability, and Regularity

In the past, complying with design rules was sufficient to ensure acceptable yields for circuits designed in a specific technology. However, for sub-90-nm technology designs, this approach tends to create physical geometry patterns that cannot be reliably printed for a given lithography setup, thus leading to hot spots and systematic yield failures.

Correspondingly, the economics of chip design have been changing as these technology challenges become more prominent with each process generation. For instance, even though the design complexity has been increasing, the timeto-market (or time-to-mission for military applications) has been steadily shrinking as well. Missing the market window can be catastrophic, as the proper demand for the product might exist for only a short period of time. This fast pace has resulted in concurrent process and product development, as companies can no longer afford to complete process development before starting out with product design. The practice of debugging designs in silicon, therefore, becomes economically infeasible, and there is increasing pressure for the silicon to work correctly the first time.

Present ASIC design methodologies break down in light of these new economic and technology realities, and new design methodologies are required for which the physical implementation of the design is more predictable. For several generations, migration to the next process node has relied primarily upon optical lithography to shrink feature sizes. It is apparent, however, that the challenges introduced in the sub-100-nm regime will make such scaling intractable without a corresponding change in the design methodology. An especially promising solution strategy is one based on so-called *regular design fabrics*; we discuss the concept of regularity and its consequences in this section.

### B. Lithographic Challenges to Design Methodology

Moore's law scaling [1] relies on the ability to shrink feature sizes of the IC by approximately 70% in each process generation. As a direct result of the aggressive scaling, the industry is now operating in the nanometer regime. However, as feature sizes continue to scale, the industry is beginning to experience a number of difficulties, thus calling into question the pace of scaling that has been the *de facto* standard.

For the industry to continue to progress with CMOS scaling and ultimately beyond, a paradigm shift is required whereby circuits are constructed from a small set of lithography friendly patterns that have previously been extensively characterized and ensured to print reliably. Two of the more prominent approaches are based on the use *restricted design rules* (RDRs) [110] and/or *regular design fabrics* [111], [112]. There are, of course, several other approaches that are motivated by the same problems [113]– [116]; namely, the functional and parametric yield failures associated with subwavelength lithography for nanoscale pattern features.

In the past, lithographers have relied on aggressively scaling the wavelength of light to enable classical CMOS scaling. In the face of recent challenges with developing cost-effective lithography systems that can operate at shorter wavelength of light, the industry has explored alternative techniques to aggressively shrink feature sizes while using the same light source. Most of these techniques rely on the use of strong resolution enhancement techniques (RETs), such as off-axis illumination and alternating aperture phase-shift masks (altPSM) [117], [118]. Although the use of RETs can improve the image quality of some patterns in the design, they tend to compromise the image quality of other patterns present in the layout. Such non-RET compliant patterns need to be identified and eliminated from the design in order to create RETcompliant design. The implementation of such an RETcompliant design is a very difficult task in general [119].

Nanoscale lithography generates a rather daunting set of problems that we must address; we enumerate the essential set of problems in the rest of this section.

1) Failure of Layout Design Rules: Design rules not only act as a means to integrate IC design and manufacturing but also serve to isolate both the design and manufacturing communities from the challenges faced by the other. The design rules attempt to define the limits for a given process in terms of overly simplified design constraints. Traditionally, a simple set of design rules was sufficient to ensure a "what you see is what you get" (WYSIWYG) paradigm that would still produce sufficient product yield. But as feature sizes continued to shrink, a simple set of design rules is incapable of documenting all the complex physical, chemical, and mechanical phenomenon that occur in a manufacturing process. In order to extend the WYSIWYG design paradigm, process engineers have introduced additional design rules to account for failures that occur due to lithography, chemically mechanically polished, etch-loading, stresses in dielectrics, and other

complex physical, chemical, and mechanical interactions. In addition, the need for RET-compliant lithography friendly designs in more advanced process technologies has further increased the raw number and the complexity of these rules [117]. In addition, the new expanded set of "DFM" design rules often leads to rules that are contradictory and conflicting to existing design rules and goals. Consequently, designs that comply with this expanded set of design rules tend to be less efficient in terms of area, timing, and power. Besides, even after complying with the expanded set of design rules, designs in the sub-100-nm regime still do not provide sufficient yield during manufacturing and require multiple design respins prior to reaching market.

2) Geometry Pattern Explosion: The problem with design respins is correlated with the large number of patterns that must be precharacterized and validated prior to final product implementation. Most importantly, the set of patterns is design-dependent; therefore, the task of characterizing a manufacturing process becomes impossible, as one has to account for the all possible patterns in a design. As a result, a process is only characterized and qualified for a small set of test patterns, and it is not uncommon to observe some uncharacterized patterns in the design that are difficult to manufacture, hence more prone to failures. In several cases where critical failures have occurred frequently, both design respins and process retargeting were warranted in order to ramp up yield of the product. Such unwanted increase in nonrecurring engineering costs has also been an area of concern for the industry, where designers have become reluctant to scale designs to more advance process technologies.

3) Drawback of Existing Design Flows: A conventional ASIC design flow begins with a high-level specification of the intended behavior of the circuit. This is often accomplished through the use of a register transfer level (RTL) description of the circuit. An RTL netlist describes the functionality of the circuit in the form of transfer functions that are linked by registers. A logic synthesis step converts the RTL into a gate-level netlist. The synthesis step includes a series of logic optimization steps to find a solution that meets the required design constraints, such as area, timing, and power. As such, the logic synthesis relies on the existence of a predefined library of logic gates to translate the RTL into a gate-level netlist while making the appropriate tradeoffs between design constraints. These logic gates are commonly referred to as standard cells, with the collection of them being referred to as a standard cell library. A standard cell library for a modern technology node can easily consist of several hundred, or even thousands, of these standard cells. In the final step of a conventional ASIC design flow, the standard cells are arranged next to each other and routed according to the connections defined in the gate level netlist, in a manner that meets both the timing and area constraints of the design.

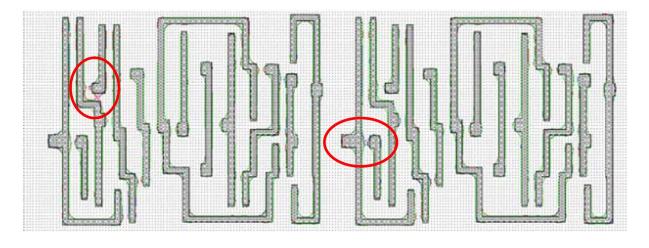

In the past, it was sufficient to ensure manufacturability of each individual standard cell to guarantee manufacturability of the entire chip. However, the complex optical interactions in sub-100-nm lithography make it difficult to predict the manufacturability and behavior of each standard cell under the influence of all the possible neighborhoods it might experience in an IC design. It is not surprising that the borders of these standard cells are breeding grounds for hotspots, as shown in Fig. 8. The simulation shown in this figure consists of two standard cell flip-flops. The flip-flop on the left has no cells on its left, whereas the flip-flop on the right has a flip-flop to its left. It can be observed that the neighborhood of the design strongly influences the presence of hot spots. Hence, the only methodology to ensure manufacturability of the entire library is to verify printability of each standard cell in all of the possible neighborhoods taking into account all possible cell abutments. For a standard cell library consisting of 1000 standard cells, there are  $\sim 2$  million possible configurations in which one can arrange a pair of standard cells. Moreover, as the feature sizes continue to shrink without reducing the wavelength of light being used, the complex optical interactions can extend past the nearest cell in the design. As such, the number of possible configurations makes the characterization of an entire standard cell library an intractable task.

#### C. The Need for Design Regularity

Limiting the number of layout patterns required to implement a design in a particular technology can greatly simplify the required RETs. Specifically, construction of the design out of a set of geometric patterns that are guaranteed to manufacture and can be well controlled to reduce variability will address the failures associated with modeling complex semiconductor processes by a set of simplistic design rules. Moreover, design methodologies that do not rely on the existence of large standard cell libraries can further reduce the number of patterns present in the ASIC design. Hence, design regularity must occur at both the pattern level and the gate/logic level. We address the former in terms of microregularity, and the latter with constraints on macroregularity.

1) Restrictive Design Rules: The use of RDRs has been proposed in the literature [110], [117]. These RDRs are used during physical design and account for the design intent. RDRs are designed to be RET generic and also serve to reduce optical proximity correction (OPC) complexity. The essence of RDRs is that they overcome challenges in implementing RETs by a paradigm shift in tools, flow, and methodology instead of introducing small changes in conventional design rules [110]. The key concepts introduced by RDRs are:

- use of smaller range of line widths for critical patterns;

- critical features such as gates are made unidirectional to decrease across-chip linewidth variation (ACLV);

Fig. 8. Lithography simulation showing hotspots as a function of pattern neighborhood.

- critical features are placed on grid (integer multiples of critical pitch);

- limit possible combinations of proximities for critical features (e.g., for critical gates select critical pitch).

This RDR microregularity improves pattern uniformity within a "macro" cell. Orientation and critical pitches can be varied from block to block as long as the pitch lies within a set of well characterized pitches. The reduction of ACLV is demonstrated in [110]. Three hundred percent reductions in ACLV are reported using RDRs. Reference [110] also shows that design rule checking, OPC, and altPSM generation are significantly simplified by using RDRs. Importantly, RDRs are effective for designs that are restricted and optimized for a particular process. To make designs portable across foundries, as is required for lowvolume ASICs and fabless design houses, a more stringent set of design rules are required.

2) Gridded Layouts: A repeating set of alternating dark (lines) and clear (spaces), known as a grating, is the simplest and most lithography-friendly patterning. The use of gridded layouts would assist in the optimization of manufacturability and decrease cost, but at the expense of increased area. The cost and area tradeoff can be minimized by selecting an optimal pitch, hence determining a grid pitch is critical [118]. To reduce the area penalty, the use of gridded layouts is sometimes suggested only for polysilicon (gates) and contact levels in the direction parallel to the lengths of the transistors [118]. Using the same horizontal pitch for contact and gate can decrease the manufacturing cost and enable the use of template trim lithography. Detailed characterization of the process at this critical pitch can improve circuit performance by reducing variability.

3) *Macroregularity*: Macroregularity, which is the limiting of the number of patterns by limiting the number of unique

"macro" pattern groupings, can provide considerable benefit for overcoming the penalties associated with microregular gridding alone. For example, field-programmable gate arrays (FPGAs) and memory designs have relied primarily on their *macroregularity* (e.g. bit-cell repeatability and known neighborhood of other bit-cells) to address the manufacturability challenges posed by new technology nodes. Due to the limited number of unique shapes present, one can afford to perform RETs, simulation-based modeling, and silicon verification for the small structures as they will ultimately appear, surrounded by the regular geometry neighborhood of other cells. It is for this reason that memories and FPGAs are often the first products to utilize a new manufacturing process.

Recently, new methodologies have been proposed for design of regular logic structures that literally combine the benefits of programmable devices (FPGAs) and application-specific customized designs [115], [116], [120]-[122]. These approaches are based on an underlying regular fabric for the logic that is constructed from configurable logic blocks, much like FPGAs and memories that can be fine-tuned for manufacturability and performance based on the layers that are shared for multiple designs and applications. Recent work on via-configurable regular fabrics in particular has shown that fabrics built from a fully programmable universal block, capable of being configured to implement many different functions, can simplify the synthesis process while providing performance comparable to that of ASIC implementations [120]-[122]. The simplified synthesis process, however, can sometimes correspond to poor silicon utilization, and hence larger designs and possibly increased yield loss due to random defects. Moreover, these approaches cannot attain the power and performance that can be achieved by full customization, and they will waste considerable area due to underutilized logic and memory, which are defined by fixed footprints across multiple applications.

#### **D. Regular Logic Bricks**

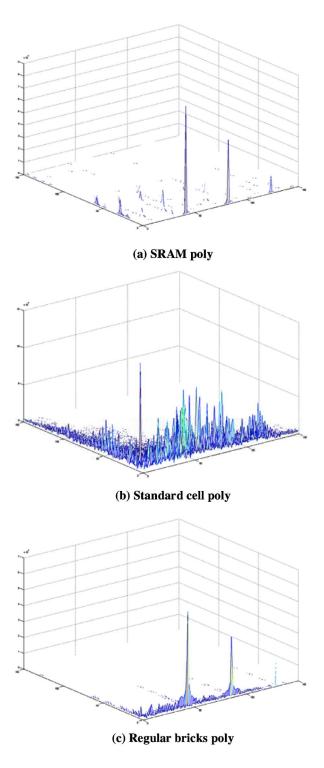

The approach in [111] and [112] proposes to limit the total number of patterns in the design by implementing both micro- and macroregularity constraints. It is apparent that the resulting regular layout offers a high degree of spatial repetition. The quantity of such repetition can be analyzed by performing a spatial frequency analysis of the layout. For example, consider the two-dimensional Fourier transform as applied to analyze the dominant frequencies in the layout patterns. We expect a layout utilizing a small number of layout patterns placed at a fixed pitch to have a high degree of repetition, and as such have a finite number of dominant frequency components, as shown in Fig. 9(a) for the polysilicon layer of the SRAM.

As expected, the plot in Fig. 9(a) shows a dominating frequency component. The other peaks, seen at the multiple of the dominating frequency component, are just harmonics that result from our choice of using Fourier analysis. Moreover, also observable from the plot are the nonzero frequencies in perpendicular orientation that indicate the periodicity of the bit-cell in the SRAM array. While the Fourier transform of the contacts in the SRAM shows a much greater number of frequency components due to nontypical contact shapes in the bit-cell layout, it is still possible to identify the few dominating frequencies that are present. Similar analysis for the polysilicon layer of a standard cell design shows that the number of patterns and their placement is not limited, resulting in a large number of frequency components in the Fourier plot [Fig. 9(b)]. A striking similarity can be seen between Fourier transform plots of the layout implemented using logic bricks on a microregular design fabric in Fig. 9(c) and that of the SRAM. The regular logic bricks are formed by grouping the logic at a higher level of abstraction and using synthesis techniques to limit the number of unique bricks that are required to implement the design [111], [112]. Because of these regularity restrictions, and the macroregular behavior similar to SRAMs, like SRAMs, the spacing rules for the logic brick patterns can be "pushed" to improve the overall design density and negate some of the area penalty that is incurred with a regular, gridded design.

1) Validating Printability of Pushed Rules: Although the introduction of regularity in the design flow improves the manufacturability of a design, it also increases the size of the design. Some of this area penalty can be regained by the use of "pushed rules." Importantly, traditional design rules are specified so that all expected patterns will print properly in all anticipated pattern neighborhoods. However, if a design is based on very microregular patterns that are grouped in macroregular controlled pattern environments, the rules can be relaxed, or *pushed*, to tighter spacings. This is typically applied in SRAMs to exploit macroregularity for higher density, but it is important to note that SRAMs have redundancy that can be used to overcome yield loss due to

**Fig. 9.** Spatial frequency analysis for (a) SRAM poly, (b) standard cell poly, and (c) regular bricks poly for a 65-nm bulk CMOS process.

spot defects. For regular logic brick implementations, one must trade off the gain in density with pushed rules against the anticipated random defect yield loss caused by the distribution of expected spot defects. The yield of a product can be simply defined as the number of good dies over the total number of dies manufactured. Traditionally, the yield was governed by random defects, such as foreign particles that would land on an IC during one of the manufacturing steps, causing a short or an open. Due to the concurrent product and process development and inherently more complex processing steps, however, the yield loss of modern ICs has been dominated by systematic defects and parametric variations (both systematic and random) [123].

## VI. STATISTICAL CIRCUIT DESIGN CHALLENGES

While delay and power are the most important performance metrics in traditional digital design, *yield* (defined as the proportion of the manufactured chips that function correctly) is now the third important metric as process variations become increasingly critical in 65-nm technologies and beyond. Enabling yield-aware digital design requires substantial modifications in the existing CAD infrastructure, including modeling, analysis, and optimization.

The overall yield loss consists of two major portions: catastrophic yield loss (due to physical and structural defects, e.g., open, short, etc.) and parametric yield loss (due to parametric variations in process parameters, e.g.,  $V_{\rm T}$ ,  $T_{\rm OX}$ , etc.). In this section, we review the new CAD methodologies that are evolving to address the parametric yield problem that is expected to become dominant as random process variations become more and more significant over technology scaling.

Recently, many advanced statistical design methodologies have been proposed to address the parametric yield issue. For instance, statistical timing analysis [124], [125] and leakage analysis [126] are two promising techniques that facilitate the bold move from deterministic IC signoff toward statistical signoff. Furthermore, advanced robust optimization algorithms [127] have also developed to concurrently improve circuit performance and parametric yield. In what follows, we review several of our own efforts in the realm of statistical methodologies and highlight the challenges and opportunities in this area.

#### A. Statistical Circuit Modeling

Circuit-level modeling focuses on a single circuit block (e.g., a standard library cell, an interconnect wire, etc.). It can be generally classified into two broad categories: *behavior modeling* and *performance modeling*.

Model order reduction (MOR) is a systematic approach to create behavior models. It takes a high-order algebraic differential equation (e.g., the modified-nodal-analysis equation for circuit simulation) as the input and creates a simplified (i.e., low-order) dynamic system to approximate the original input–output behavior. The extracted behavior models are typically utilized in a hierarchical simulation flow to reduce the simulation cost. For example, reduced-order interconnect models can be used to speed up the gate-interconnect cosimulation.

While most early stage MOR works focus on a fixed dynamic system [128]–[130], nanoscale integrated circuits are no longer deterministic due to large-scale process variations. The challenging problem here is how to incorporate the statistical process parameters into the MOR formulation and extract the reduced-order model as a function of them. Such a problem is typically referred to as the parameterized MOR (PMOR) in the MOR community.

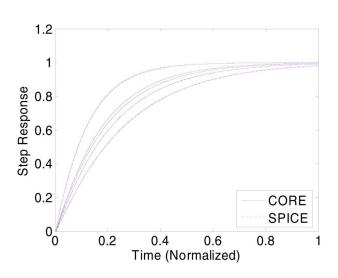

CORE [131] is one novel algorithm to solve the aforementioned PMOR problem. CORE utilizes a two-step moment matching scheme that first matches the multiparameter moments for process parameters and then matches the moments for frequency. The main advantage of such a two-step moment matching is that an extremely compact (small-size) reduced-order model can be generated to match a large number of multiparameter moments. Fig. 10 shows one example of PMOR analysis using CORE.

Performance modeling is most commonly referred to as *response surface modeling* in mathematics. It approximates the performance of interest (e.g., delay, leakage power, etc.) as a function of the parameters of interest (e.g.,  $V_{TH}$ ,  $T_{OX}$ , L, W, temperature, etc.). For example, statistical timing library characterization is one of the performance modeling problems in the digital domain.

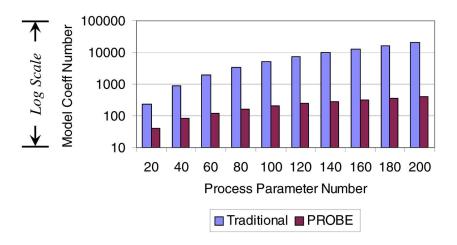

While the simplest (but least accurate) performance modeling is based on linear approximation, it is not sufficiently accurate for capturing large-scale process variations in many practical cases. To achieve better accuracy, a quadratic approximation can be used, which, however, significantly increases the modeling cost. For example, a commercial 65-nm CMOS process typically contains ~100 independent random variables to model global

Fig. 10. CORE [1] accurately captures the step response variation of an interconnect network containing 1275 RC elements. Results are plotted at five random Monte Carlo samples.

Fig. 11. PROBE [1] significantly reduces the number of model coefficients compared with the traditional full-rank quadratic approximation.

process variations. In this case, a quadratic model will include a  $100 \times 100$  quadratic coefficient matrix containing  $10^4$  coefficients. The problem size will become even larger if device mismatches must be simultaneously considered.

One successful avenue of attack on this problem relies on use of *projection-based* approaches (PROBE [132]) to address the aforementioned complexity problem. Instead of fitting the full-rank quadratic model, we attempt to find an optimal low-rank model by minimizing the approximation error. For example, using the PROBE method (see Fig. 11), the number of model coefficients almost linearly scales with the number of process parameters.

Reducing the size of these models is only one of the critical optimizations we need to address. Another is the runtime of some models. A particularly vexing example is the problem of estimating rare event statistics for highreplication circuits such as SRAMs and flip-flops. In these scenarios, a very rare event for a single cell may become a not-so-rare event for a full SRAM or control-dominated ASIC, where millions of copies of this fundamental circuit may be present. In these problems, methods borrowed from data mining turn out to be highly useful. For example, the method called statistical blockade proposed in [133] attempts to build a nonlinear classifier that filters out "insufficiently rare" combinations of statistical circuit parameters during Monte Carlo analysis. The core idea is quite simple: it is easy to generate the data for one Monte Carlo sample; it is expensive to actually simulate the circuit associated with each sample. Statistical blockade prevents us from having to simulate the uninteresting high probability circuits but passes through the rare event parameter combinations. In this way, rare circuit events that occur far out in low-probability tails of the performance distribution can be accurately and much more quickly extracted. The technique can offer significant speedups. For example, a recently proposed analytical model for DRV was validated with a 1 billion element "virtual" Monte Carlo analysis: an advanced form of statistical blockade was applied [134], which required the simulation of only roughly 45 000 different circuit points to achieve  $6-\sigma$  accuracy, a speedup of over 20 000 times.

#### **B. Statistical Circuit Analysis**

Integrated circuit analysis has been moving from the traditional corner-based approach towards a range of new statistical flows for both transistor-level blocks and fullchip systems.

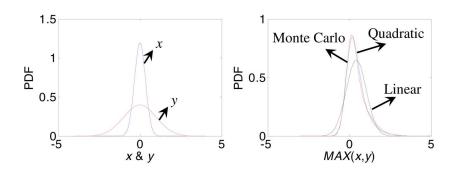

Direct Monte Carlo analysis based on transistor-level simulation is a straightforward yet expensive approach to estimate the statistical performance distribution. One more efficient approach is to first extract the performance model and then estimate the distribution using the model. In many practical cases, if the performance model is approximated as a quadratic function, the performance distribution can be analytically extracted using the APEX algorithm proposed in [135]. APEX conceptually considers the unknown probability density function to be of the form of the impulse response of a linear time-invariant (LTI) system. The probability density function is then optimally approximated by moment matching.

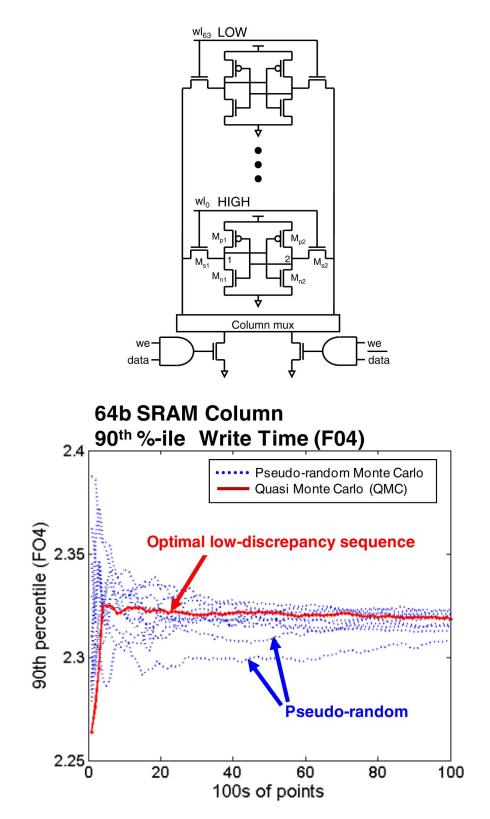

An alternative strategy is to better control the Monte Carlo samples to reduce the analysis cost. Instead of directly drawing samples from a pseudorandom number generator, [136] uses so-called *low-discrepancy* samples, which are deterministically chosen to "more uniformly" sample the statistical distribution. The technique, of classical origin, is called *quasi-Monte Carlo* (QMC) and, interestingly enough, is now a standard method in the computational finance world, used for evaluating complex financial instruments under various forms of statistical uncertainty. The technique seems extremely promising when applied to the world of scaled semiconductor problems as well: speedups from 10 to 50 times have been demonstrated in [136] compared with the direct Monte Carlo simulation. Fig. 12 shows one detailed example from statistical SRAM analysis.

Full-chip statistical analysis typically utilizes a hierarchical flow to handle the large problem size. For example, the statistical static timing analysis (SSTA) proposed in [137] takes the gate-level timing model as the input, propagates the delay distributions throughout the full-chip netlist by a number of  $SUM(\bullet)$  and  $MAX(\bullet)$  operations, and finally generates the statistical slacks to predict the parametric timing yield.

While the SSTA algorithm in [137] is limited to linear approximations, Zhan *et al.* further proposed an improved algorithm that can handle nonlinear gate-level timing models and nonlinear MAX( $\bullet$ ) approximations [138]; see Fig. 13. Compared with linear approximations, more than 10x error reduction has been demonstrated in [138] by applying quadratic models to a number of benchmark circuits.

In addition to delay variations, leakage power varies significantly (e.g.,  $10x \times 20x$ ) in nanoscale technologies. To accurately predict the leakage variation and facilitate an efficient leakage/timing cooptimization, [139] proposed a novel projection-based full-chip leakage analysis algorithm. The algorithm can extract quadratic leakage models by using an iterative numerical algorithm borrowed from matrix computations. The extracted leakage power, therefore, is not limited to a log-normal distribution.

#### C. Statistical Circuit Optimization

The objective of statistical circuit optimization is to leave sufficient performance margins to accommodate large-scale process variations. The recent advances in statistical circuit analysis make it possible to accurately predict statistical performance distribution, thereby facilitating much more accurate statistical optimization than the traditional corner-based technique. Overdesign can be avoided (or at least significantly reduced) by using the statistical techniques.

Transistor-level statistical optimization focuses on a single circuit block (e.g., flip flops, memory cells, etc.). It takes a fixed circuit topology and optimizes the device sizes (e.g., transistor widths and lengths) to maximize the performance of interest (e.g., power, delay, etc.). Although one circuit block is small (e.g., consisting of  $10 \sim 20$  transistors), statistically optimizing such a block is not trivial since its performance can be affected by  $50 \sim 100$  process parameters and the variations of these parameters significantly increase the problem complexity.

The ROAD tool developed in [140] is a novel optimization algorithm to address the transistor-level problem. ROAD consists of three major steps: 1) performance modeling using PROBE [132]; 2) statistical performance analysis using APEX [135]; and 3) statistical optimization to push the distribution tail to the specification boundary. ROAD utilizes PROBE and APEX for statistical modeling and analysis so that the optimization problem becomes tractable with consideration of all process variations.

Compared with transistor-level optimization, full-chip statistical optimization is much more challenging due to the significantly increased problem size. A particularly fruitful class of methods for these large problems relies on clever exploitation of convex modeling. One example statistical technique for optimizing (i.e., sizing) large-size digital circuits is [141]. The main idea is to approximate the gate and interconnect delays by (generalized) posynomial functions. As such, the digital sizing problem can be formulated as a (generalized) geometric programming that can be efficiently and robustly solved by a convex optimizer for extremely large problem sizes. In many practical cases, the approximated polynomial delay models are sufficiently accurate to create a good initial design from which further local optimizations can be applied with fast convergence.

## VII. MAINTAINING THE DIGITAL DESIGN ABSTRACTION AS SCALING CONTINUES

Digital circuit design has the dominant position that it does because of its ability to hide the many layers of complex physical and electrical behavior of the elementary devices it exploits. For example, digital noise margins ensure predictable behavior according to relatively simple logiclevel abstractions even in the presence of process, temperature, and voltage variability and increasingly "nonideal" devices. The robustness of these logic-level abstractions has resulted in entire chip-level design flows (most notably for ASICs,) which are based on judicious hiding of circuit and layout details. These design flows have been remarkably successful for the past two decades but are today under duress due to the challenges arising from nanometer-scale transistors.