# Read Disturb Errors in MLC NAND Flash Memory: Characterization, Mitigation, and Recovery

Carnegie Mellon University Yu Cai, Yixin Luo, Saugata Ghose, Erich F. Haratsch\*, Ken Mai, Onur Mutlu \*Seagate Technology

#### Overview

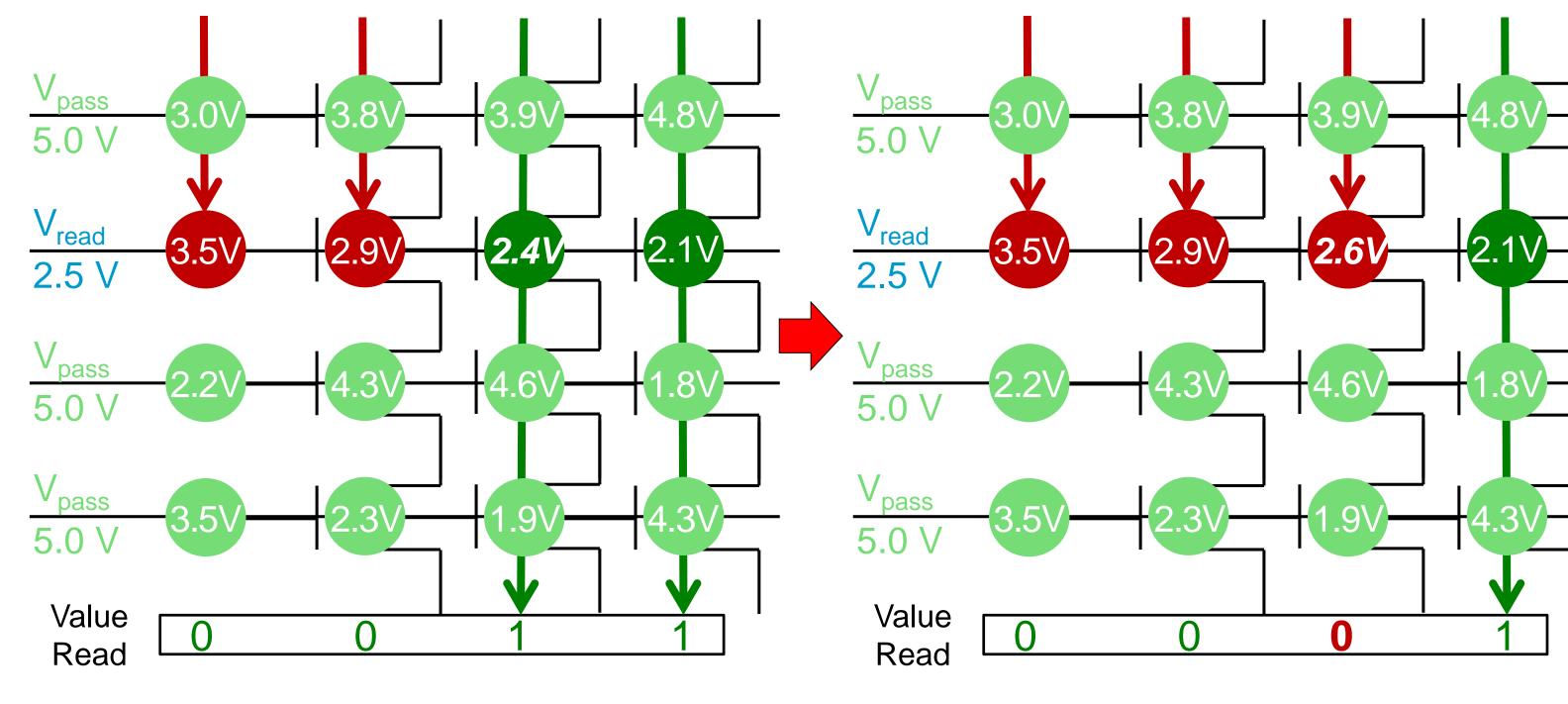

Within flash block, when one page is read, V<sub>pass</sub> (pass-through voltage) applied to other pages • Pass-through voltage has a weak programming effect – in unread pages, stored voltages increase over time: *read disturb*

### **Read Disturb Characterization: Real Chips**

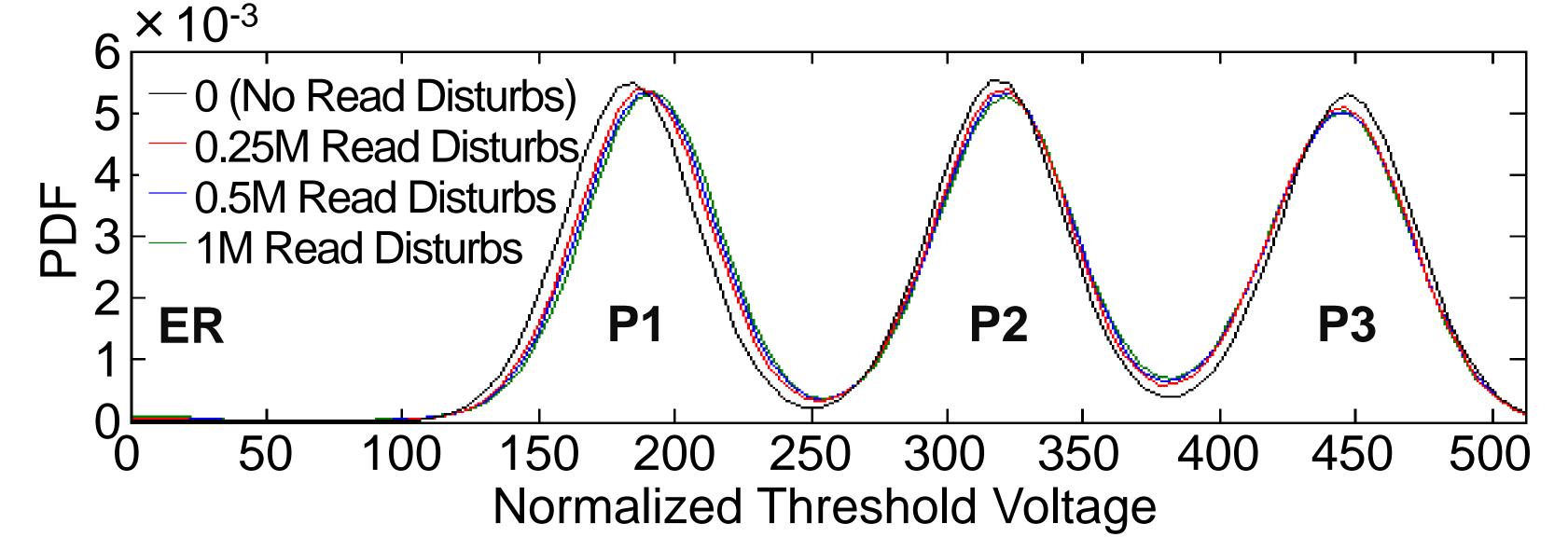

Lower voltage states shift more as read disturb counts increase due to greater F-N tunneling

- Characterize impact of read disturb errors on real 2Y-nm flash chips

- Two solutions for read disturb

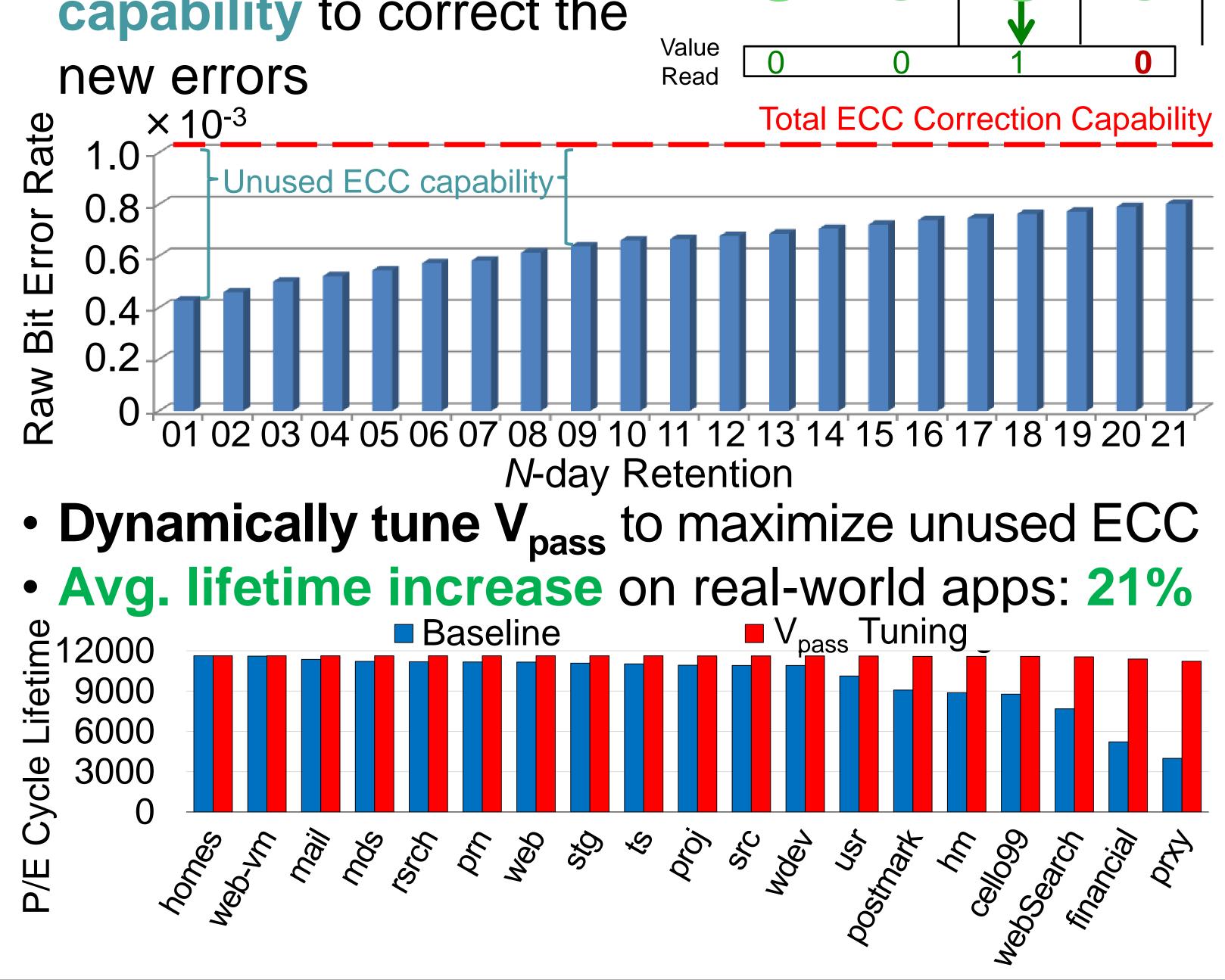

- Mitigation by performing dynamic V<sub>pass</sub> Tuning

read

Recovery by reversing read disturb behavior

- Wear-out increases effect of each read disturb

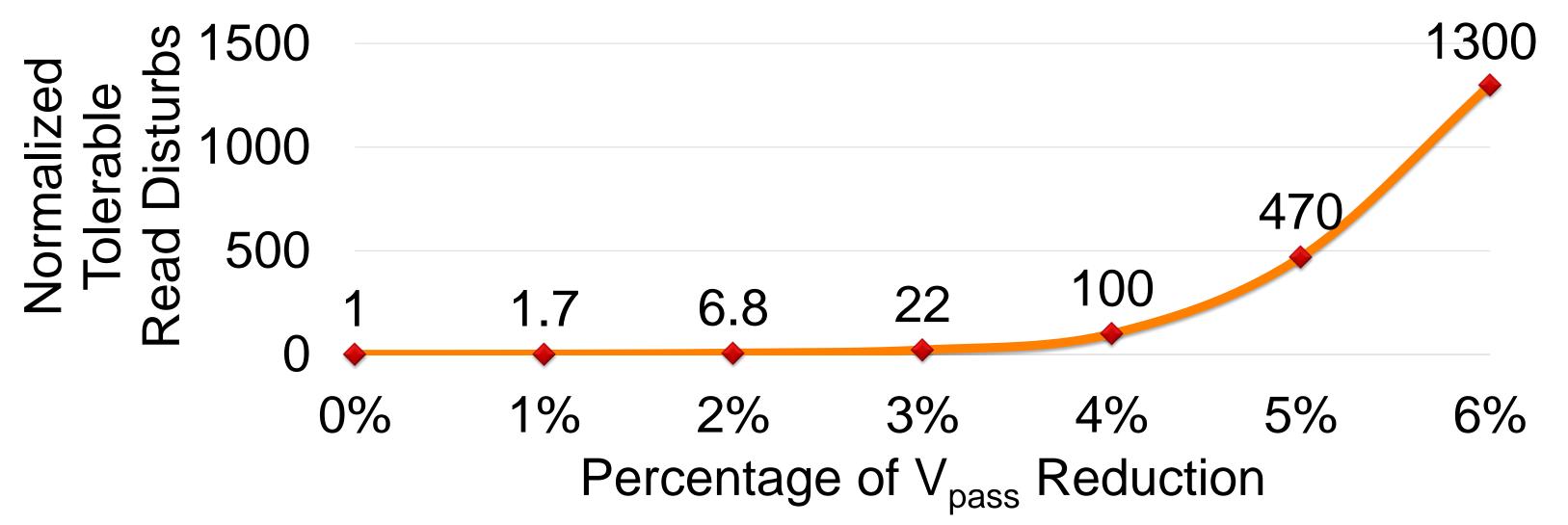

- Slightly lowering V<sub>pass</sub> greatly reduces read disturb errors

## **Read Disturb Mitigation: V**pass **Tuning**

- Lowering V<sub>pass</sub> reduces V<sub>pass</sub> read disturb errors, but 4.7 V can introduce new 2.5 V read errors – *improper* pass-through

- Exploit unused ECC capability to correct the

#### **Read Disturb Oriented Error Recovery**

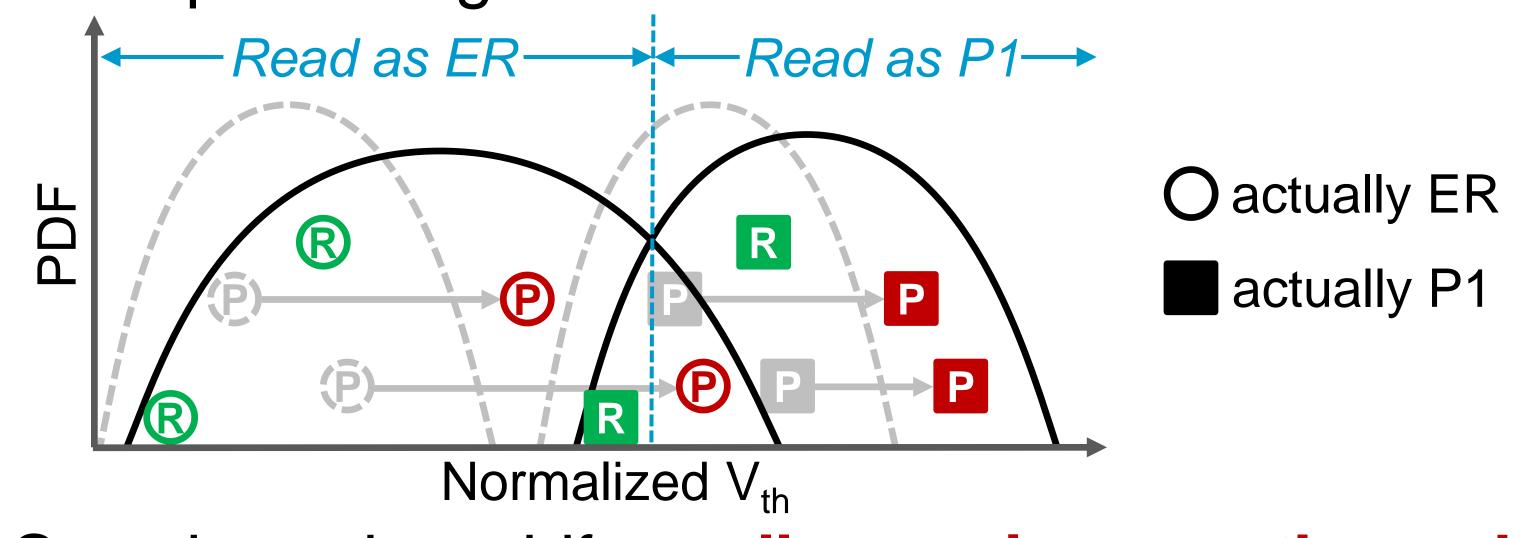

- Some flash cells *more susceptible* to read disturb

- Disturb-prone cells (P): large voltage shifts to high end of state distribution

- Disturb-resistant cells (R): small shifts, remaining in low end of distribution

- Example: voltage shifts after 250K read disturbs

- State boundary shifts: cells now incorrectly read

- Once flash lifetime ends (too many errors for ECC), recover data by *reversing read disturb*

- Induce more read disturbs to ID prone/resistant

- Predict prone cells  $\rightarrow$  lower state

- Predict resistant cells  $\rightarrow$  higher state

- ECC handles remaining corrections

- After 1M read disturbs, recovery can reduce error count by 36%

Y. Cai et al. *Read Disturb Errors in MLC NAND Flash* Memory: Characterization and Mitigation. DSN 2015.