### Providing High and Controllable Performance in Multicore Systems Through Shared Resource Management

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Lavanya Subramanian

B.E., Electronics and Communication, Madras Institute of Technology

M.S., Electrical and Computer Engineering, Carnegie Mellon University

#### **Thesis Committee:**

Advisor: Prof. Onur Mutlu Prof. Greg Ganger Prof. James Hoe Dr. Ravi Iyer, Intel

Carnegie Mellon University Pittsburgh, PA

July, 2015

Copyright © 2015 Lavanya Subramanian

In memory of my beloved granddad Rajamony (1917 - 2005) who was so full of life until his last breath

#### **Abstract**

Multiple applications executing concurrently on a multicore system interfere with each other at different shared resources such as main memory and shared caches. Such inter-application interference, if uncontrolled, results in high system performance degradation and unpredictable application slowdowns. While previous work has proposed application-aware memory scheduling as a solution to mitigate inter-application interference and improve system performance, previously proposed memory scheduling techniques incur high hardware complexity and unfairly slowdown some applications. Furthermore, previously proposed memory-interference mitigation techniques are not designed to precisely control application performance.

This dissertation seeks to achieve high and controllable performance in multicore systems by mitigating and quantifying the impact of shared resource interference. First, towards mitigating memory interference and achieving high performance, we propose the Blacklisting memory scheduler. We observe that ranking applications individually with a total order based on memory access characteristics, like previous schedulers do, leads to high hardware cost, while also causing unfair application slowdowns. The Blacklisting memory scheduler overcomes these shortcomings based on two key observations. First, we observe that, to mitigate interference, it is sufficient to separate applications into only two groups, one containing applications that are vulnerable to interference and another containing applications that cause interference, instead of ranking individual applications with a total order. Vulnerable-to-interference group is prioritized over the interference-causing group. Second, we show that this grouping can be efficiently performed by simply counting the number of consecutive requests served from each application – an application that has a large number of consecutive requests served is dynamically classified as interference-

causing. The Blacklisting memory scheduler, designed based on these insights, achieves high system performance and fairness, while incurring significantly lower complexity than state-of-the-art application-aware schedulers.

Next, towards quantifying the impact of memory interference and achieving controllable performance in the presence of memory bandwidth interference, we propose the Memory Interference induced Slowdown Estimation (MISE) model. The MISE model estimates application slowdowns due to memory interference based on two observations. First, the performance of a memory-bound application is roughly proportional to the rate at which its memory requests are served, suggesting that request-service-rate can be used as a proxy for performance. Second, when an application's requests are prioritized over all other applications' requests, the application experiences very little interference from other applications. This provides a means for estimating the uninterfered request-service-rate of an application while it is run alongside other applications. Using the above observations, MISE estimates the slowdown of an application as the ratio of its uninterfered and interfered request service rates. We propose simple changes to the above model to estimate the slowdown of non-memory-bound applications. We propose and demonstrate two use cases that can leverage MISE to provide soft performance guarantees and high overall performance/fairness.

Finally, we seek to quantify the impact of shared cache interference on application slowdowns, in addition to memory bandwidth interference. Towards this end, we propose the Application Slowdown Model (ASM). ASM builds on MISE and observes that the performance of an application is strongly correlated with the rate at which the application accesses the shared cache. This is a more general observation than that of MISE and holds for all applications, thereby enabling the estimation of slowdown for any application as the ratio of the uninterfered to the interfered shared cache access rate. This reduces the problem of estimating slowdown to estimating the shared cache access rate of the application had it been run alone on the system. ASM periodically estimates each application's cache-access-rate-alone by minimizing interference at the main memory and quantifying interference at the shared cache. We propose and demonstrate several use cases of ASM that leverage it to provide soft performance guarantees and improve performance and fairness.

## **Acknowledgments**

My educational journey until this point has been fruitful and very memorable, thanks to all the wonderful people who have been a part of my journey. First and foremost, I am grateful to my advisor, Prof. Onur Mutlu, who was willing to take me on as his student despite my lack of background in computer architecture then and give me the mentorship, time and encouragement to build background and grow as a researcher. Onur's emphasis on clarity in thinking, speaking and writing has been a major influence in shaping me. I am also very thankful to Onur for providing me with the resources and freedom to carry out research and for always finding the right opportunities by way of collaborations and internships to further my research.

I would like to thank my committee members, Prof. Greg Ganger, Prof. James Hoe and Dr. Ravi Iyer for their time, effort and inputs in bringing this dissertation to completion. Special thanks to James for his encouragement and feedback even since my early years at Carnegie Mellon University. Thanks to Greg for his incisive insights on various aspects of my work, from his unique perspective as the storage QoS expert on my committee. Thanks to Ravi for his many inputs and insights on QoS and for giving me the opportunity to intern with his spirited and warm group in Intel Labs, Hillsboro.

The SAFARI group has been a great source of critical feedback, ideas and fun. I am incredibly thankful for everything I've learned from this group of smart, enthusiastic and hard-working graduate students over the years. Vivek Seshadri has been a great friend and lab mate. He has been an amazing sounding board for new ideas. Several of the ideas in this thesis have evolved

a lot through numerous discussions with Vivek. Thanks a lot to Yoongu Kim for all his feedback on writing and presentation. Yoongu's high standards for research, presentation and writing are an inspiration. I am thankful to Chris Fallin for his critical feedback on research and for all I learned from him during the many times we worked together on TAing, course work, quals. Thanks a lot to Samira Khan for the many discussions on research and life, in general. Donghyuk Lee's DRAM expertise and drive to keep learning are admirable. Kevin Chang's methodical approach to research and problem solving have been very useful in many of the projects we have worked together on. Thanks to Rachata Ausavarungnirun for his helpful nature. Many thanks to visiting researchers Hui Wang, Hiroyuki Usui and interns Harsha Rastogi, Arnab Ghosh for working with me on different research projects. Thanks to Gennady Pekhimenko for being a great cube mate. His work ethic and discipline are admirable. Thanks to Justin Meza, Hongyi Xin, Nandita Vijayakumar, Yang Li, Yixin Luo, Kevin Hsieh and Amirali Bouramand for the many discussions and dinners.

Besides members of the SAFARI group, several graduate students have been a great source of advice and encouragement at several points. Thanks to Siddharth Garg for getting me inducted into the workings of graduate school and the sound advice, when I was still learning the ropes as a first year graduate student. Thanks to Michael Papamichael for all the inputs, advice and discussions over the years at Carnegie Mellon University. Michael's genuine passion for research and his ability to explain concepts so clearly are inspiring. Thanks to Karthik Lakshmanan for the many discussions and inputs during my early years. Thanks to Anagha Kulkarni for her encouragement and the many discussions we have had about graduate school and life in general when at MSR, Redmond. Thanks to Michelle Goodstein for her company and her perspectives on life. Many thanks to Elaine Lawrence, Samantha Goldstein, Karen Lindenfelser, Nathan Snizaski, Marilyn Patete, Debbie Scappatura and Olivia Vadnais for helping me navigate through administrative aspects. Thanks also to the CMU shuttle and escort drivers who have safely ferried me home several late nights.

I enjoyed my internships at Intel Labs, Hillsboro and Microsoft Research, Redmond. Thanks to Li Zhao for being a very hands-on and involved mentor during my internship at Intel Labs.

Li was always available to brainstorm and discuss. Thanks to Trishul Chilimbi, Sriram Sankar and Kushagra Vaid for being great mentors during my internship at MSR. Thanks to Thomas Moscibroda for the weekly brainstorming sessions when I was at MSR. Many thanks to Gabriel Loh for his mentorship. I would like to thank National Science Foundation (NSF), Semiconductor Research Corporation (SRC), Gigascale Systems Research Center (GSRC) and Intel for generously supporting my research over the years and Carnegie Mellon University for supporting me with the John and Claire Bertucci fellowship

I am very thankful to all my teachers from school and professors from undergrad for instilling in me a basic sense of curiosity and an urge to learn. Special thanks to Ms. Jennifer, Ms. Nargis, Ms. Bhuvaneswari, Prof. Mala John and Prof. Kannan. Thanks also to several seniors from my undergraduate institution who served as role models and a source of inspiration. I am grateful to Dr. Sasikanth Avancha from Intel for mentoring me on my undergraduate project and my manager at SanDisk, Radhakrishnan Nair, for his support when applying to graduate school.

Graduate school is a long and intense journey, with many highs and lows. I am very thankful for the support systems I had through grad school, in terms of friends, room mates and family. Thanks to Anusha Venkatramani, Ashwati Krishnan, Aishwarya Sukumar, Lavanya Iyer, Swati Sarraf and Manali Bhutiyani for being great and very understanding room mates and friends. Thanks to Abhay Ramachandra, Aditi Pandya, Arun Kannawadi, Arvind Muralimohan, Athula Balachandran, Bhavana Dalvi, Divya Hariharan, Divya Sharma, Janani Mukundan, Madhumitha Ramesh, Mahesh Joshi, Natasha Kholgade, Niranjini Rajagopal, Ramkumar Krishnan, Siddharth Komini Babu, Siddharth Gopal, Suchita Ramachandran, Swaminathan Ramesh, Varoon Shankar for their companionship through different points of grad school. Thanks to Aishwarya R, Anusha Radhakrishnan, Ramya Guptha, Gayatri Singaravelu, Mukund Kalyanaraman, Sudharsan Seshadri and Arunachalam Annamalai for their friendship and support from afar.

My family has been a big source of support, encouragement and comfort all through my journey. Thanks to my mother, Bhuvaneswari and my father, Subramanian for instilling in me the value of education. My mother, a math teacher, inculcated in me an interest in math from a young age and has been a big source of encouragement. My father's work ethic has been an inspiration. My grand parents have been extremely supportive of all my endeavors, right from a very young age and I am grateful to them for all the warmth, support and care over the years. My grand father Rajamony's enthusiasm until his very last breath was infectious. My grand mother Jambakam's appreciation of and strong belief in the need for a solid education, despite her not having had access to it is admirable. I am also very grateful to my paternal grand mother Visalakshi for her encouragement - she, for some reason, thought I was going to be an engineer since I was ten years old. I wish she had seen me finish my PhD.

My uncle, Kumar, has been a great source of encouragement, knowledge and fun. He introduced me to science through fun experiments at home. He introduced me to the wonderful world of books and libraries from a very young age. He has had an immense role in shaping me during my formative years. My sister, Lakshmi, has been a pillar of support. Through school and undergrad, she was always willing and eager to get me any books and resources I needed. She has been extremely supportive and involved in all my major academic/career decisions. My parents-in-law and sister-in-law, Devi have been a big source of encouragement over the past couple of years.

Finally, Kaushik Vaidyanathan has been a rock solid pair of dependable shoulders, over the past several years as my best friend and more recently, my husband. Right from pushing me to apply to grad school to listening to my long rants during times of self doubt to putting up with my erratic schedules to what not, his support has been immense and has made this whole journey possible and that much more fun and enjoyable. I will not even attempt to say thank you for that will trivialize all that he has done for me.

# **Contents**

| 1 | Intr | roduction 1                                                            |    |  |  |  |

|---|------|------------------------------------------------------------------------|----|--|--|--|

|   | 1.1  | Problem                                                                | 1  |  |  |  |

|   | 1.2  | Our Solutions                                                          | 3  |  |  |  |

|   |      | 1.2.1 The Blacklisting Memory Scheduler                                | 3  |  |  |  |

|   |      | 1.2.2 The Memory Interference induced Slowdown Estimation (MISE) Model | 4  |  |  |  |

|   |      | 1.2.3 The Application Slowdown Model (ASM)                             | 5  |  |  |  |

|   | 1.3  | Thesis Statement                                                       | 5  |  |  |  |

|   | 1.4  | Contributions                                                          | 6  |  |  |  |

|   | 1.5  | Dissertation Outline                                                   | 7  |  |  |  |

| 2 | Bacl | kground and Related Prior Work                                         | 8  |  |  |  |

|   | 2.1  | DRAM Main Memory Organization                                          | 8  |  |  |  |

|   | 2.2  | Related Work on Memory Scheduling                                      | 10 |  |  |  |

|   | 2.3  | Related Complementary Memory Scheduling Proposals                      | 11 |  |  |  |

|   | 2.4  | Other Related Work on Memory Interference Mitigation                   | 12 |  |  |  |

|   | 2.5  | Related Work on DRAM Optimizations to Improve Performance              | 13 |  |  |  |

|   | 2.6  | Related Work on Shared Cache Capacity Management                       | 14 |  |  |  |

|   | 2.7   | Related  | Work on Coordinated Cache and Memory Management                  | 15 |

|---|-------|----------|------------------------------------------------------------------|----|

|   | 2.8   | Related  | d Work on Cache and Memory QoS                                   | 15 |

|   | 2.9   | Related  | l Work on Storage QoS                                            | 16 |

|   | 2.10  | Related  | l Work on Interconnect QoS                                       | 17 |

|   | 2.11  | Related  | Work on Online Slowdown Estimation                               | 18 |

| 3 | Mitig | gating N | Memory Bandwidth Interference Towards Achieving High Performance | 20 |

|   | 3.1   | Key Ol   | oservations                                                      | 22 |

|   | 3.2   | Mecha    | nism                                                             | 26 |

|   |       | 3.2.1    | The Blacklisting Mechanism                                       | 26 |

|   |       | 3.2.2    | Blacklist-Based Memory Scheduling                                | 27 |

|   | 3.3   | Implen   | nentation                                                        | 27 |

|   |       | 3.3.1    | Storage Cost                                                     | 28 |

|   |       | 3.3.2    | Logic Cost                                                       | 28 |

|   | 3.4   | Method   | dology                                                           | 29 |

|   |       | 3.4.1    | System Configuration                                             | 29 |

|   |       | 3.4.2    | Workloads                                                        | 29 |

|   |       | 3.4.3    | Metrics                                                          | 30 |

|   |       | 3.4.4    | RTL Synthesis Methodology                                        | 30 |

|   |       | 3.4.5    | Mechanism Parameters                                             | 31 |

|   | 3.5   | Evalua   | tion                                                             | 31 |

|   |       | 3.5.1    | Analysis of Individual Workloads                                 | 33 |

|   |       | 252      | Hardwara Complayity                                              | 24 |

|   |     | 3.5.3          | Trade-offs Between Performance, Fairness and Complexity     | 35       |

|---|-----|----------------|-------------------------------------------------------------|----------|

|   |     | 3.5.4          | Understanding the Benefits of BLISS                         | 37       |

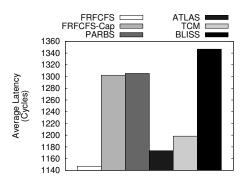

|   |     | 3.5.5          | Average Request Latency                                     | 38       |

|   |     | 3.5.6          | Impact of Clearing the Blacklist Asynchronously             | 40       |

|   |     | 3.5.7          | Comparison with TCM's Clustering Mechanism                  | 40       |

|   |     | 3.5.8          | Evaluation of Row Hit Based Blacklisting                    | 41       |

|   |     | 3.5.9          | Comparison with Criticality-Aware Scheduling                | 42       |

|   |     | 3.5.10         | Effect of Workload Memory Intensity and Row-buffer Locality | 43       |

|   |     | 3.5.11         | Sensitivity to System Parameters                            | 45       |

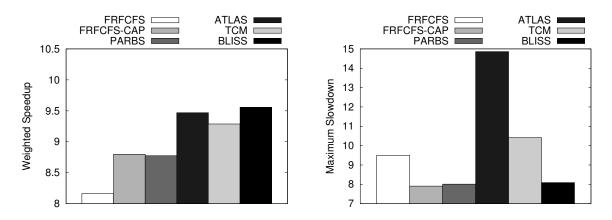

|   |     | 3.5.12         | Sensitivity to Algorithm Parameters                         | 48       |

|   |     | 3.5.13         | Interleaving and Scheduling Interaction                     | 49       |

|   | 3.6 | Summa          | ary                                                         | 52       |

| 4 | Qua | ntifying       | Application Slowdowns Due to Main Memory Interference       | 53       |

|   | 4.1 | The M          | ISE Model                                                   | 54       |

|   |     | 4.1.1          | Memory-bound Application                                    | 54       |

|   |     | 4.1.2          | Non-memory-bound Application                                | 57       |

|   | 4.2 | Implen         | nentation                                                   | 58       |

|   |     |                |                                                             |          |

|   |     | 4.2.1          | Memory Scheduling Algorithm                                 | 58       |

|   |     | 4.2.1<br>4.2.2 | Memory Scheduling Algorithm                                 |          |

|   |     |                |                                                             | 59       |

|   |     | 4.2.2          | Computing shared-request-service-rate (SRSR)                | 59<br>60 |

|   | 4.3 | Methodology .      |                         |                          |        |         |        |      |       |      |      | 62 |

|---|-----|--------------------|-------------------------|--------------------------|--------|---------|--------|------|-------|------|------|----|

|   | 4.4 | Comparison to S    | TFM                     |                          |        |         |        |      |       |      |      | 63 |

|   | 4.5 | Sensitivity to Alg | gorithm Parameters .    |                          |        |         |        |      |       |      |      | 66 |

|   | 4.6 | Summary            |                         |                          |        |         |        |      |       |      |      | 67 |

| 5 | App | lications of the M | IISE Model              |                          |        |         |        |      |       |      |      | 68 |

|   | 5.1 | MISE-QoS: Prov     | riding Soft QoS Guara   | antees                   |        |         |        |      |       |      |      | 68 |

|   |     | 5.1.1 Mechani      | sm Description          |                          |        |         |        |      |       |      |      | 69 |

|   |     | 5.1.2 MISE-Q       | oS with Multiple AoIs   | s                        |        |         |        |      |       |      |      | 70 |

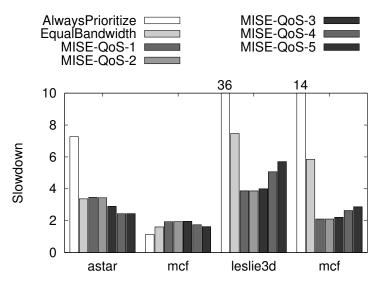

|   |     | 5.1.3 Evaluation   | on with Single AoI      |                          |        |         |        |      |       |      |      | 70 |

|   |     | 5.1.4 Case Stu     | dy: Two AoIs            |                          |        |         |        |      |       |      |      | 75 |

|   | 5.2 | MISE-Fair: Mini    | mizing Maximum Slo      | owdown                   |        |         |        |      |       |      |      | 77 |

|   |     | 5.2.1 Mechani      | sm                      |                          |        |         |        |      |       |      |      | 77 |

|   |     | 5.2.2 Interaction  | on with the OS          |                          |        |         |        |      |       |      |      | 78 |

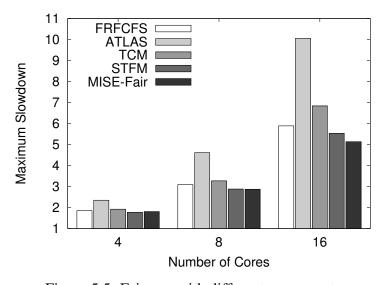

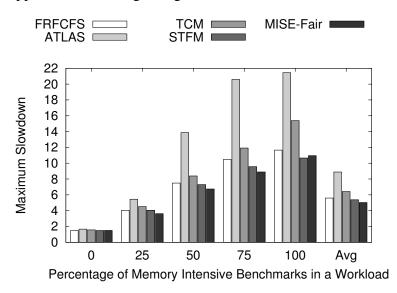

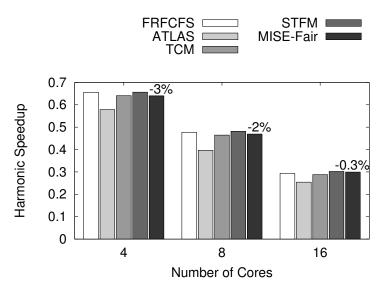

|   |     | 5.2.3 Evaluation   | on                      |                          |        |         |        |      |       |      |      | 79 |

|   | 5.3 | Summary            |                         |                          |        |         |        |      |       |      |      | 82 |

| 6 | Oua | ntifying Annlicat  | ion Slowdowns Due t     | o Roth Sha               | red C  | ache I  | nterf  | eren | ല വ   | ad S | hare | ha |

| U |     | n Memory Interf    |                         | o Doin Sha               | icu Ca | aciic i | iici i |      | cc ai | iu 5 | 1141 | 83 |

|   | 6.1 | •                  | Application Slowdow     | n Model (A               | SM)    |         |        |      |       |      |      |    |

|   | 0.1 |                    |                         |                          |        |         |        |      |       |      |      |    |

|   |     | 6.1.1 Observat     | ion: Access rate as a j | proxy for pe             | erform | ance    |        |      |       |      |      | 84 |

|   |     | 6.1.2 Challeng     | e: Accurately Estimat   | ting CAR <sub>alor</sub> | ne · · |         |        |      |       |      |      | 87 |

|   |     | 6.1.3 ASM vs.      | Prior Work              |                          |        |         |        |      |       |      |      | 88 |

|   | 6.2 | Implementing AS    | SM                      |                          |        |         |        |      |       |      |      | 88 |

|   |     | 6.2.1    | Measuring $CAR_{shared}$                  |

|---|-----|----------|-------------------------------------------|

|   |     | 6.2.2    | Estimating $CAR_{alone}$                  |

|   |     | 6.2.3    | Accounting for Memory Queueing            |

|   |     | 6.2.4    | Sampling the Auxiliary Tag Store          |

|   |     | 6.2.5    | Hardware Cost                             |

|   | 6.3 | Metho    | dology                                    |

|   | 6.4 | Evalua   | tion of the Model                         |

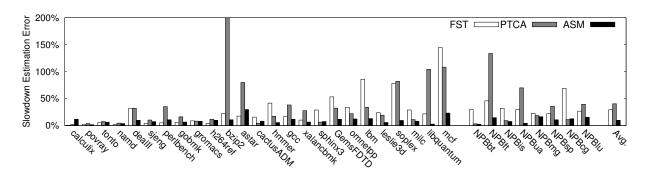

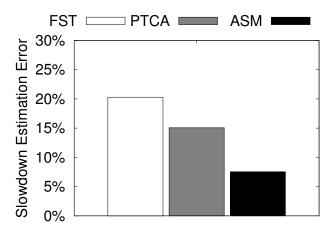

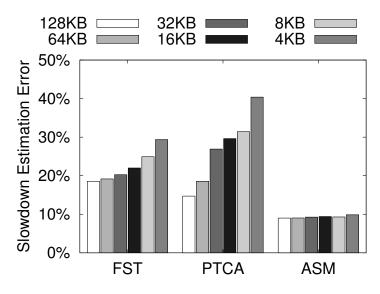

|   |     | 6.4.1    | Slowdown Estimation Accuracy              |

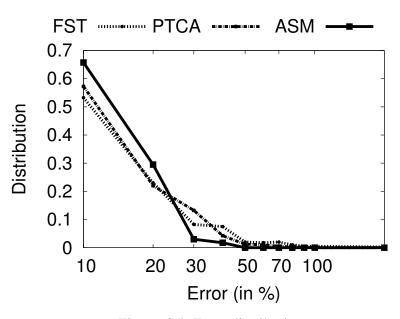

|   |     | 6.4.2    | Distribution of Slowdown Estimation Error |

|   |     | 6.4.3    | Impact of Prefetching                     |

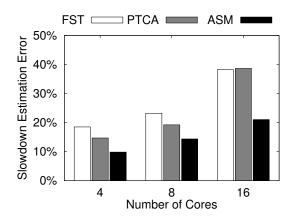

|   |     | 6.4.4    | Sensitivity to System Parameters          |

|   |     | 6.4.5    | Sensitivity to Algorithm Parameters       |

|   | 6.5 | Summ     | ary                                       |

| 7 | App | lication | s of ASM 102                              |

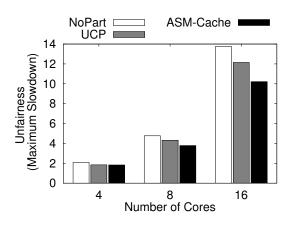

|   | 7.1 | ASM (    | Cache Partitioning (ASM-Cache)            |

|   |     |          | Mechanism                                 |

|   |     | 7.1.2    | Evaluation                                |

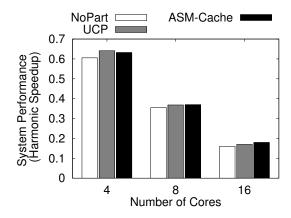

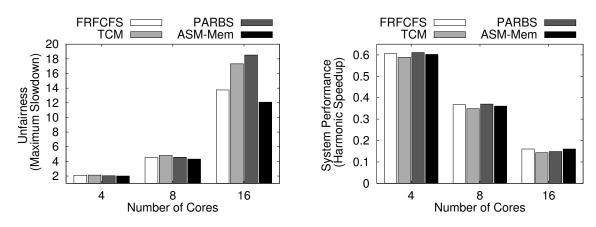

|   | 7.2 | ASM I    | Memory Bandwidth Partitioning             |

|   |     | 7.2.1    | Mechanism                                 |

|   |     | 7.2.2    | Evaluation                                |

|   |     | 7.2.3    | Combining ASM-Cache and ASM-Mem           |

|   | 7.2 |          |                                           |

|   | 7.3 | Provid   | ing Soft Slowdown Guarantees              |

|   | 7.4 | Fair Pr  | icing in Cloud Systems                                   |

|---|-----|----------|----------------------------------------------------------|

|   | 7.5 | Migrat   | ion and Admission Control                                |

|   | 7.6 | Summ     | ary                                                      |

| 8 | Con | clusions | s and Future Directions 112                              |

|   | 8.1 | Conclu   | asions                                                   |

|   | 8.2 | Future   | Research Directions                                      |

|   |     | 8.2.1    | Leveraging Slowdown Estimates for Cluster Management     |

|   |     | 8.2.2    | Performance Guarantees in Heterogeneous Systems          |

|   |     | 8.2.3    | Integration of Memory Interference Mitigation Techniques |

|   |     | 8.2.4    | Resource Management for Multithreaded Applications       |

|   |     | 8.2.5    | Coordinated Management of Main Memory and Storage        |

|   |     | 8.2.6    | Comprehensive Slowdown Estimation                        |

# **List of Tables**

| 3.1 | Configuration of the simulated system                                     | 29  |

|-----|---------------------------------------------------------------------------|-----|

| 3.2 | Clearing the blacklist asynchronously                                     | 40  |

| 3.3 | Performance sensitivity to threshold and interval                         | 48  |

| 3.4 | Unfairness sensitivity to threshold and interval                          | 48  |

| 4.1 | Configuration of the simulated system                                     | 62  |

| 4.2 | Average error for each benchmark (in %)                                   | 66  |

| 4.3 | Sensitivity of average error to epoch and interval lengths                | 67  |

| 5.1 | Workload mixes                                                            | 71  |

| 5.2 | Effectiveness of MISE-QoS                                                 | 71  |

| 5.3 | Effectiveness of STFM-QoS                                                 | 75  |

| 6.1 | Quantities measured by ASM for each application to estimate $CAR_{alone}$ | 90  |

| 6.2 | Configuration of the simulated system                                     | 93  |

| 6.3 | Sensitivity to epoch and quantum lengths                                  | 101 |

# **List of Figures**

| 1.1  | leslie3d's slowdown compared to when run alone                           | 2  |

|------|--------------------------------------------------------------------------|----|

| 2.1  | DRAM main memory organization                                            | 9  |

| 3.1  | Performance vs. fairness vs. simplicity                                  | 21 |

| 3.2  | Request service distribution over time with TCM and Grouping schedulers  | 23 |

| 3.3  | Performance and fairness of Grouping vs. TCM                             | 24 |

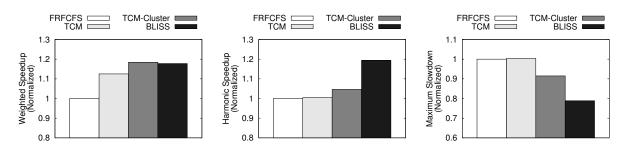

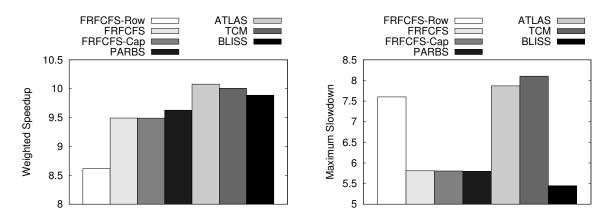

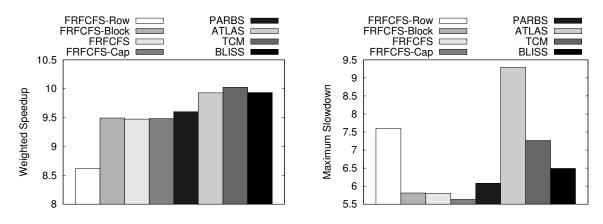

| 3.4  | System performance and fairness of BLISS compared to previous schedulers | 32 |

| 3.5  | Pareto plot of system performance and fairness                           | 32 |

| 3.6  | System performance and fairness for all workloads                        | 34 |

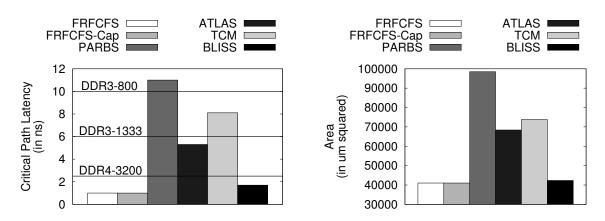

| 3.7  | Critical path: BLISS vs. previous schedulers                             | 35 |

| 3.8  | Area: BLISS vs. previous schedulers                                      | 35 |

| 3.9  | Performance, fairness and simplicity trade-offs                          | 36 |

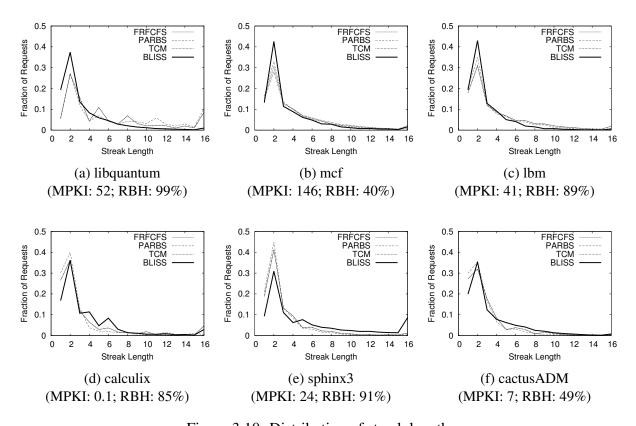

| 3.10 | Distribution of streak lengths                                           | 37 |

| 3.11 | The Average Request Latency Metric                                       | 39 |

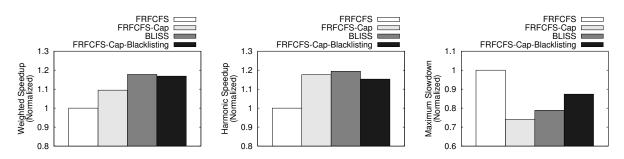

| 3.12 | Comparison with TCM's clustering mechanism                               | 41 |

| 3.13 | Comparison with FRFCFS-Cap combined with blacklisting                    | 42 |

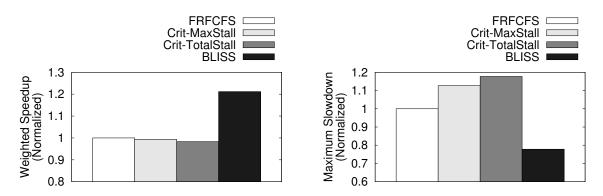

| 3.14 | Comparison with criticality-aware scheduling                             | 43 |

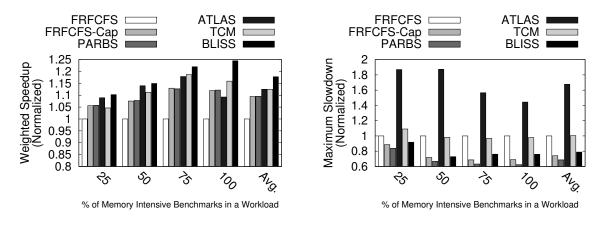

| 3.15 | Sensitivity to workload memory intensity                                       | 44 |

|------|--------------------------------------------------------------------------------|----|

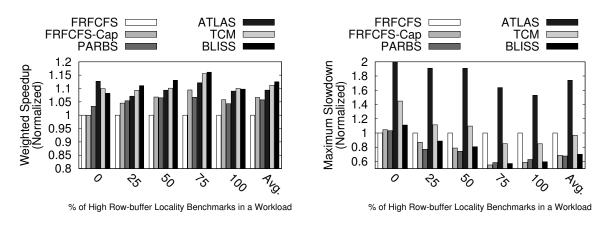

| 3.16 | Sensitivity to row-buffer locality                                             | 45 |

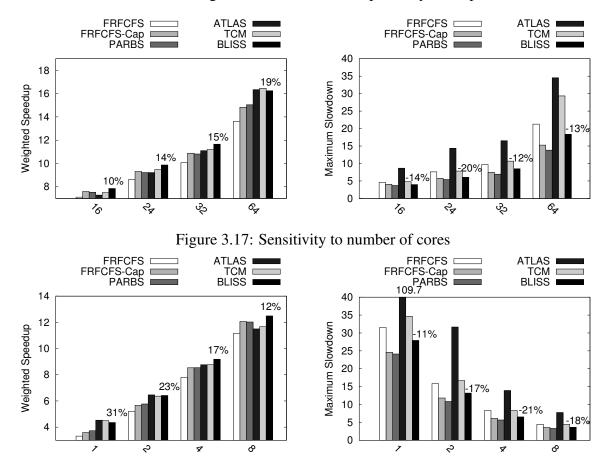

| 3.17 | Sensitivity to number of cores                                                 | 46 |

| 3.18 | Sensitivity to number of channels                                              | 46 |

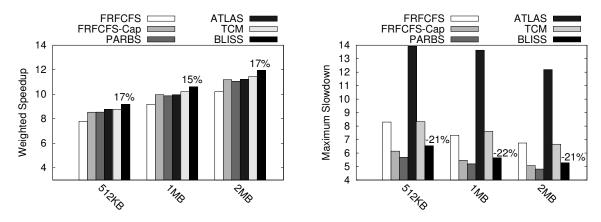

| 3.19 | Sensitivity to cache size                                                      | 47 |

| 3.20 | Performance and fairness with a shared cache                                   | 47 |

| 3.21 | Scheduling and cache block interleaving                                        | 50 |

| 3.22 | Scheduling and sub-row interleaving                                            | 51 |

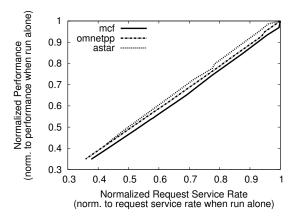

| 4.1  | Request service rate vs. performance                                           | 55 |

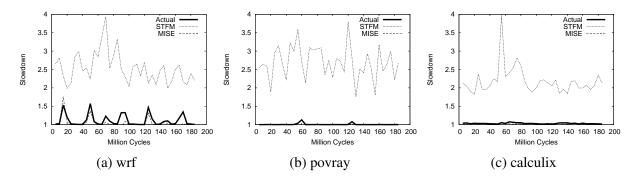

| 4.2  | Comparison of our MISE model with STFM for representative memory-bound         |    |

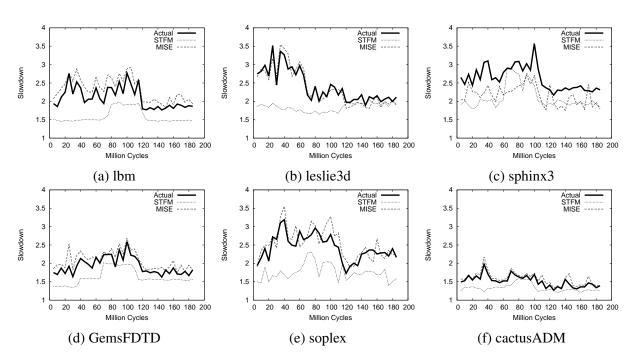

|      | applications                                                                   | 65 |

| 4.3  | Comparison of our MISE model with STFM for representative non-memory-bound     |    |

|      | applications                                                                   | 65 |

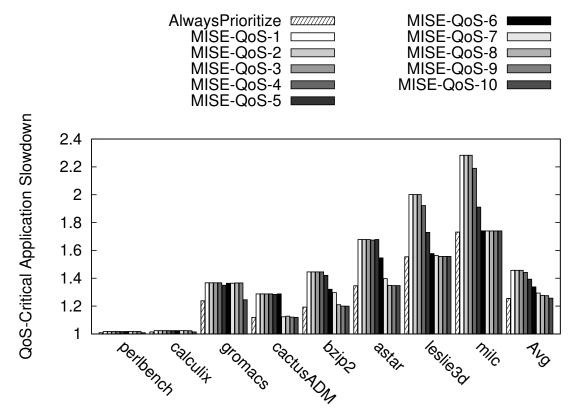

| 5.1  | AoI performance: MISE-QoS vs. AlwaysPrioritize                                 | 72 |

| 5.2  | Average system performance and fairness across 300 workloads of different mem- |    |

|      | ory intensities                                                                | 73 |

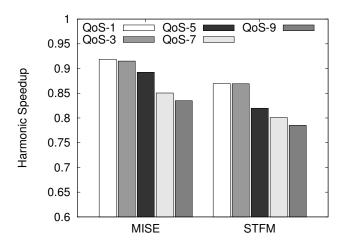

| 5.3  | Average system performance using MISE and STFM's slowdown estimation mod-      |    |

|      | els (across 300 workloads)                                                     | 75 |

| 5.4  | Meeting a target bound for two applications                                    | 76 |

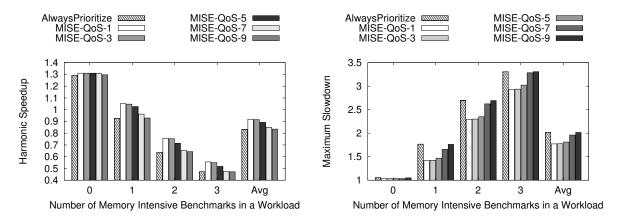

| 5.5  | Fairness with different core counts                                            | 79 |

| 5.6  | Fairness for 16-core workloads                                                 | 80 |

| 5.7  | Harmonic speedup with different core counts                                    | 81 |

| 6.1 | Impact of shared cache interference on application slowdowns |

|-----|--------------------------------------------------------------|

| 6.2 | Cache access rate vs. performance                            |

| 6.3 | Slowdown estimation accuracy with no sampling                |

| 6.4 | Slowdown estimation accuracy with sampling                   |

| 6.5 | Error distribution                                           |

| 6.6 | Prefetching impact                                           |

| 6.7 | Sensitivity to core count                                    |

| 6.8 | Sensitivity to cache capacity                                |

| 6.9 | Sensitivity to ATS size                                      |

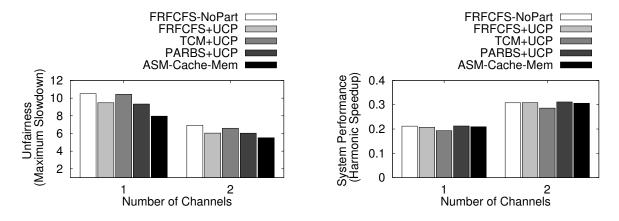

| 7.1 | ASM-Cache: Fairness and performance                          |

| 7.2 | ASM-Mem: Fairness and performance                            |

| 7.3 | Combining ASM-Cache and ASM-Mem                              |

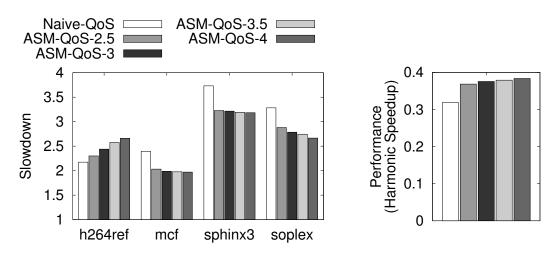

| 7.4 | ASM-OoS: Slowdowns and performance                           |

# **Chapter 1**

### Introduction

#### 1.1 Problem

Applications executing concurrently on a multicore chip contend with each other to access shared resources such as main memory and shared caches. The main memory has limited bandwidth, driven by constraints on pin counts. If the available shared cache capacity and memory bandwidth are not managed well, different applications can harmfully interfere with each other, resulting in significant degradation in both system performance and individual application performance. Furthermore, the slowdown experienced by an application due to inter-application interference at these shared resources depends on the other concurrently running applications and the available memory bandwidth and shared cache capacity. Hence, different applications experience different and unpredictable slowdowns.

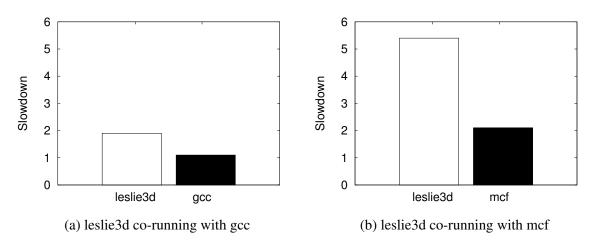

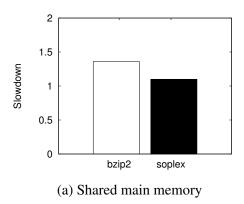

Figure 1.1 shows leslie3d, an application from the SPEC CPU 2006 suite when it is run with two different applications, gcc and mcf, on a simulated two-core system where the cores share a main memory channel. As can be seen, leslie3d and mcf slow down significantly due to shared resource interference (gcc does not slow down since it is largely compute-bound and does not access the main memory much). Furthermore, leslie3d slows down by 1.9x when it is run with

gcc, an application that rarely accesses the main memory. However, leslie3d slows down by 5.4x when it is run with mcf, which frequently accesses the main memory. This is one representative example demonstrating that an application experiences different slowdowns when run with applications that have different shared resource access characteristics. We observe this behavior across a variety of applications, as also observed by previous works [82, 86, 87, 89], resulting in high and unpredictable applications slowdowns.

Figure 1.1: leslie3d's slowdown compared to when run alone

Inter-application interference and the resultant high application slowdowns are a major problem in most multicore systems, where multiple applications share resources. Furthermore, the unpredictable nature of the slowdowns is particularly undesirable in several scenarios where some applications are critical and need to meet requirements on their performance. For instance, in a data center/virtualized environment where multiple applications, each potentially from a different user, are consolidated on the same machine, it is common for each user to require a certain guaranteed performance for their application. Another example is in mobile systems where interactive and non-interactive jobs share resources and the interactive jobs need to meet deadlines/frame rate requirements. Our main research objective is to mitigate and quantify shared resource interference, towards the end of achieving high and controllable application performance, through simple and implementable slowdown estimation and shared resource management techniques.

#### 1.2 Our Solutions

#### 1.2.1 The Blacklisting Memory Scheduler

Towards achieving our goal of high system performance and fairness, we propose the Blacklisting memory scheduler, a simple memory scheduler design that is able to achieve high performance and fairness at low cost by mitigating interference at the main memory. Although the problem of memory interference mitigation has been much explored, with memory request scheduling being the prevalent solution direction, we observe that previously proposed memory schedulers are both complex and unfair. The main source of this complexity and unfairness is the notion of ranking applications individually, with a total rank order, based on applications' memory access characteristics. Computing and enforcing ranks incurs high hardware complexity, both in terms of logic and storage overhead. As a result, the critical path latency and chip area of ranking-based application-aware memory schedulers is significantly higher compared to application-unaware schedulers. For example, Thread Cluster Memory Scheduler (TCM) [61], a state-of-the-art application-aware scheduler is 8x slower and 1.8x larger than a commonly-employed application-unaware scheduler, FRFCFS [97]. Furthermore, when a total order based ranking is employed, applications that are at the bottom of the ranking stack get heavily deprioritized and unfairly slowed down. This greatly degrades system fairness.

In order to overcome these shortcomings of previous ranking-based schedulers, we propose the Blacklisting memory scheduler (BLISS) [108, 109] based on two new observations. First, in contrast to forming a total rank order of all applications (as done in prior works), we find that, to mitigate interference, it is sufficient to i) separate applications into *only two* groups, one group containing applications that are vulnerable to interference and another containing applications that cause interference, and ii) prioritize the requests of the *vulnerable-to-interference* group over the requests of the *interference-causing* group. Second, we observe that applications can be efficiently classified as either *vulnerable-to-interference* or *interference-causing* by simply counting the num-

ber of consecutive requests served from an application in a short time interval.

BLISS achieves better system performance and fairness than the best-performing previous schedulers, while incurring significantly low complexity. However, BLISS does not tackle the problem of unpredictable application slowdowns.

#### 1.2.2 The Memory Interference induced Slowdown Estimation (MISE) Model

Towards tackling the problem of unpredictable application slowdowns, we first propose to estimate/quantify and control application slowdowns in the presence of interference at the main memory. First, we estimate application slowdowns using the Memory Interference induced Slowdown Estimation (MISE) model [111]. The MISE model accurately estimates application slowdowns based on two key observations. First, the performance of a memory-bound application is roughly proportional to the rate at which its memory requests are served. This observation suggests that we can use request-service-rate as a proxy for performance, for memory-bound applications. As a result, slowdown of such an application can be computed as the ratio of the request-service-rate when the application is run alone on a system to that when it is run alongside other interfering applications. Second, the alone-request-service-rate of an application can be estimated by giving the application's requests the highest priority in accessing memory. Giving an application's requests the highest priority in accessing memory results in very little interference from other applications' requests. As a result, most of the application's requests are served as though the application has all the memory bandwidth for itself, allowing the system to gather a good estimate for the alone-request-service-rate of the application. We adapt these observations and extend the model to estimate slowdowns of applications that are not bound at memory too.

Accurate slowdown estimates from the MISE model can enable several mechanisms to achieve both high and controllable performance. We build two such mechanisms on top of our proposed model to demonstrate its effectiveness.

#### 1.2.3 The Application Slowdown Model (ASM)

The MISE model estimates slowdowns due to interference at the main memory. However, it does not take into account interference at the shared caches and assumes caches are private. The Application Slowdown Model (ASM) [110] estimates slowdowns due to both shared cache and main memory interference. ASM does so by exploiting the observation that the performance of each application is roughly proportional to the rate at which it accesses the shared cache. This observation builds on MISE's observation on correlation between memory request service rate and performance. However, it is more general and applies to all applications, unlike MISE's observation that applies only to memory-bound applications. ASM estimates alone-cache-access-rate in two steps. First, ASM minimizes interference for an application at the main memory by giving the application's requests the highest priority at the memory controller, similar to MISE. Doing so also enables ASM to get an accurate estimate of the average cache miss service time of the application had it been run alone (to be used in the next step). Second, ASM quantifies the effect of interference at the shared cache by using an auxiliary tag store to determine the number of shared cache misses that would have been hits if the application did not share the cache with other applications (contention misses). This aggregate contention miss count is used along with the average miss service time (from the previous step) to estimate the actual time it would have taken to serve the application's requests had it been run alone.

We present and evaluate several mechanisms that can leverage ASM's slowdown estimates towards achieving different goals such as high performance, fairness, bounded application slowdowns and fair billing, thereby demonstrating the model's effectiveness.

#### 1.3 Thesis Statement

High and controllable performance can be achieved in multicore systems through simple and implementable mechanisms to mitigate and quantify shared resource interference.

#### 1.4 Contributions

This dissertation makes the following major contributions:

- This dissertation makes the observation that it is not necessary to rank individual applications with a total rank order, like most previous ranking-based application-aware memory schedulers do, in order to mitigate interference between applications. This observation enables the design of the Blacklisting memory scheduler, a low-complexity memory scheduling technique that is able to achieve high performance and fairness, by simply categorizing applications as interference-causing or vulnerable.

- This dissertation makes the observation that an application's performance is roughly proportional to the rate at which requests are generated to/served at a shared resource. This observation can serve as a general principle enabling the estimation of progress/slowdowns at different shared resources.

- This dissertation presents the Memory Interference induced Slowdown Estimation (MISE) model that accurately estimates application slowdowns in the presence of memory interference as the ratio of uninterfered to interfered request service rates, based on the correlation between request service rate and performance.

- This dissertation presents the Application Slowdown Model (ASM) that accurately estimates application slowdowns due to both shared cache and main memory interference, by minimizing interference at the main memory and quantifying interference at the shared cache.

- This dissertation builds several resource management mechanisms on top of MISE and ASM

that leverage their slowdown estimates to provide high performance, fairness and bounded

slowdowns, demonstrating MISE/ASM's effectiveness in estimating slowdowns.

#### 1.5 Dissertation Outline

This dissertation is organized into eight chapters. Chapter 2 presents background on memory system organization and discusses related prior work on shared resource management and providing Quality of Service (QoS). Chapter 3 presents the design of the Blacklisting memory scheduler (BLISS) and evaluates it against state-of-the-art memory request schedulers. Chapter 4 presents the Memory Interference induced Slowdown Estimation (MISE) model and its evaluation against previous slowdown estimation techniques. Chapter 5 presents memory bandwidth management schemes that leverage the MISE model to provide bounded application slowdowns and fairness. Chapter 6 presents the Application Slowdown Model (ASM) and compares it against previous schemes that estimate slowdown due to both shared cache and main memory interference. Chapter 7 presents several use cases that leverage slowdown estimates from ASM to provide high performance, fairness and bounded slowdowns. Finally, Chapter 8 presents conclusions and future research directions that are enabled by this dissertation.

# Chapter 2

# **Background and Related Prior Work**

The problem of shared resource interference has been a significant deterrent to achieving high and controllable system performance. Not surprisingly, several previous works have attempted to mitigate interference at both the shared caches and main memory, with the goal of improving system performance. However, few previous works have tackled the problem of unpredictable application slowdowns in the presence of shared resource interference.

In this chapter, we will first provide a brief background on DRAM main memory organization and discuss previous proposals in different related areas, namely memory interference mitigation, DRAM optimizations to improve system performance, shared cache capacity management, Quality of Service (QoS) and slowdown estimation.

#### 2.1 DRAM Main Memory Organization

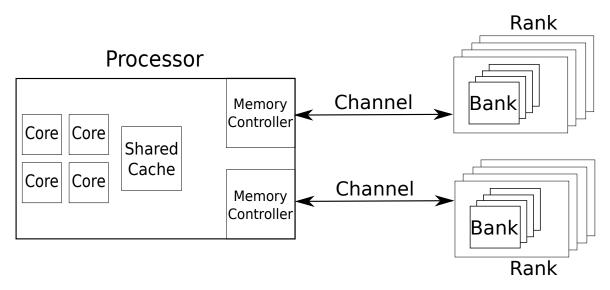

The DRAM main memory system is organized as channels, ranks and banks hierarchically as shown in Figure 2.1. Channels are independent and can operate completely in parallel. Each channel consists of ranks (typically 1 - 4) that share the command and data bus of the channel.

A rank consists of multiple banks. The banks can operate in parallel. However, all banks within

Figure 2.1: DRAM main memory organization

a channel share the command and data bus of the channel. Each bank, in turn, is organized as an array of rows and columns. On a data access, the entire row containing the data is brought into an internal structure called the row-buffer. Therefore, a subsequent access to the same row can be served in the row-buffer itself and need not access the array. This is called a row hit. On an access to a different row though, the array needs to be accessed. Such an access is called a row miss. A row hit is served  $\sim 2x$  faster than a row miss [47]. Please refer to [62, 70, 66] for more detail on DRAM operation.

Commonly employed memory controllers employ a memory scheduling policy called First Ready First Come First Served (FRFCFS) [129, 97] that leverages the row buffer by prioritizing row hits over row misses/conflicts. Older requests are then prioritized over newer requests. FRFCFS aims to maximize DRAM throughput by prioritizing row hits. However, it unfairly prioritizes requests of applications that generate a large number of requests to the same row (high-row-buffer-locality) and access memory frequently (high-memory-intensity) [82, 86].

#### 2.2 Related Work on Memory Scheduling

Much prior work has focused on mitigating this unfairness and inter-application interference at the main memory, with the goals of improving system performance and fairness, of which a predominant solution direction is memory request scheduling. Several previous works [86, 87, 83, 60, 61, 41, 34] have proposed application-aware memory scheduling techniques that take into account the memory access characteristics of applications and schedule requests appropriately in order to mitigate inter-application interference and improve system performance and fairness.

Mutlu and Moscibroda propose PARBS [87], an application-aware memory scheduler that batches the oldest requests from applications and prioritizes the batched requests, with the goals of preventing starvation and improving fairness. Within each batch, PARBS ranks individual applications based on the number of outstanding requests from the application and, using this total rank order, prioritizes requests of applications that have low-memory-intensity to improve system throughput. Kim et al. [60] observe that applications that receive low memory service tend to experience interference from applications that receive high memory service. Based on this observation, they propose ATLAS, an application-aware memory scheduler that ranks individual applications based on the amount of long-term memory service each application receives and prioritizes applications that receive low memory service, with the goal of improving overall system throughput.

Another recently proposed memory scheduling technique, Thread cluster memory scheduling (TCM) [61] ranks individual applications by memory intensity such that low-memory-intensity applications are prioritized over high-memory-intensity applications (to improve system throughput). Kim et al. [61] also observed that ranking all applications based on memory intensity and prioritizing low-memory-intensity applications could slow down the deprioritized high-memory-intensity applications significantly and unfairly. This is because when all applications are ranked by memory service, applications with high memory intensities are ranked lower, as they inherently tend to have high memory service, as compared to other applications. With the goal of mitigat-

ing this unfairness, TCM clusters applications into low- and high-memory-intensity clusters. In the low-memory-intensity cluster, applications are ranked by memory- intensity, whereas, in the high-memory-intensity cluster, applications' ranks are shuffled randomly to provide fairness. Both clusters employ a total rank order among applications at any given time.

More recently, Ghose et al. [34] propose a memory scheduler that aims to prioritize *critical* memory requests that stall the instruction window for long lengths of time. The scheduler predicts the criticality of a load instruction based on how long it has stalled the instruction window in the past (using the instruction address (PC)) and prioritizes requests from load instructions that have large total and maximum stall times measured over a period of time. Although this scheduler is not application-aware, we compare to it as it is the most recent scheduler that aims to maximize performance by mitigating memory interference.

All these state-of-the-art schedulers incur significant hardware complexity and cost to rank applications based on their memory access characteristics and prioritize requests based on this ranking. This results in significant increase in critical path latency and area, as we discuss in Chapter 3.

#### 2.3 Related Complementary Memory Scheduling Proposals

Parallel Application Memory Scheduling (PAMS) [28] tackles the problem of mitigating interference between different threads of a multithreaded application, while Staged Memory Scheduling (SMS) [10] attempts to mitigate interference between the CPU and GPU in CPU-GPU systems. Principles from our work can be employed in both of these contexts to identify and deprioritize interference-causing threads, thereby mitigating interference experienced by vulnerable threads/applications. Complexity effective memory access scheduling [124] attempts to achieve the performance of FRFCFS using a First Come First Served scheduler in GPU systems, by preventing row-buffer locality from being destroyed when data is transmitted over the on-chip network. This proposal is complementary to our proposals and can be combined with our techniques that prevent threads from hogging the row-buffer and banks. Ipek et al. [41] propose a memory

controller design that employs machine learning techniques (reinforcement learning) to maximize DRAM throughput. While such a policy could learn applications' memory access characteristics over time and appropriately optimize its scheduling policy to improve performance, implementing machine learning techniques in the memory controller hardware could increase complexity.

Several previous works have tackled the problem of scheduling write back requests to memory. Stuecheli et al. [107] and Lee et al. [64] propose to schedule write backs such that requests to the same row are scheduled together to exploit row-buffer locality. Seshadri et al. [100] exploit their proposed dirty-block index structure to identify dirty cache blocks from the same row, enabling a simpler implementation of row-locality-aware write back. Zhao et al. [126] propose request scheduling mechanisms to tackle the problem of heavy write traffic in persistent memory systems. Our techniques can be combined with these different write handling mechanisms to achieve better fairness and performance.

Previous works have also tackled the problem of memory management and request scheduling in the presence of prefetch requests. Lee et al. [63] propose to dynamically prioritize/deprioritize prefetch requests based on prefetcher accuracy. Lee et al. [65] also propose to schedule requests accordingly to take advantage of the memory-level parallelism in the system, in the presence of prefetch requests. Ebrahimi et al. [26] propose to incorporate prefetcher awareness, based on monitoring prefetcher accuracy, into previously proposed fair memory schedulers such as PARBS. These mechanisms can be combined with our proposals such as BLISS and the memory bandwidth allocation policies we build on top of MISE and ASM, to incorporate prefetch-awareness.

#### 2.4 Other Related Work on Memory Interference Mitigation

While memory scheduling is a major solution direction towards mitigating interference, previous works have also explored other approaches such as address interleaving [53], memory bank/channel partitioning [84, 50, 71, 122, 57], source throttling [27, 113, 13, 20, 91, 90, 55] and thread scheduling [128, 112, 21, 118] to mitigate interference.

**Subrow Interleaving:** Kaseridis et al. [53] propose minimalist open page, a data mapping policy that interleaves data at the granularity of a sub-row across channels and banks such that applications with high row-buffer locality are prevented from hogging the row buffer, while still preserving some amount of row-buffer-locality.

**Memory Channel/Bank Partitioning:** Previous works [84, 50, 71, 122, 57] propose techniques to mitigate inter-application interference by partitioning channels/banks among applications such that the data of interfering applications are mapped to different channels/banks.

**Source Throttling:** Source throttling techniques (e.g., [27, 113, 13, 20, 91, 90, 55, 11]) propose to throttle the memory request injection rates of interference-causing applications at the processor core itself rather than regulating an application's access behavior at the memory, unlike memory scheduling, partitioning or interleaving. Other previous work by Ebrahimi et al. [26] proposes to tune shared resource management policies such as FST [27] to be aware of prefetch requests.

**OS** Thread Scheduling: Previous works [128, 112, 118] propose to mitigate shared resource contention by co-scheduling threads that interact well and interfere less at the shared resources. Such a solution relies on the presence of enough threads with such symbiotic properties. Other techniques [21] propose to map applications to cores to mitigate memory interference.

Our proposals to mitigate memory interference, with the goals of providing high performance and fairness, can be combined with these solution approaches in a synergistic manner to achieve better mitigation and consequently, higher performance and fairness.

# 2.5 Related Work on DRAM Optimizations to Improve Performance

Several prior works have proposed optimizations to DRAM (internals) to enable more parallelism within DRAM, thereby improving performance. Kim et al. [62] propose techniques to enable access to multiple DRAM sub-arrays in parallel, thereby overlapping the latencies of these paral-

lel accesses. Lee et al. in [66] observe that long bitlines contribute to high access latencies and propose to split bitlines into two shorter segments (using an isolation transistor), enabling faster access to one of the shorter segments. More recently, Lee at al. [67] propose to relax DRAM timing constraints in order to optimize for performance in the common case. Multiple previous works [127, 7, 8] have proposed to partition a DRAM rank, enabling parallel access to these partitioned ranks. These techniques are complementary to memory interference mitigation techniques and can be combined with them to achieve high performance benefits.

#### 2.6 Related Work on Shared Cache Capacity Management

The management of shared cache capacity among multiple contending applications is a much explored area. A large body of previous research has focused on improving the shared cache replacement policy [38, 46, 56, 99]. These proposals use different techniques to predict which cache blocks would have high reuse and try to retain such blocks in the cache. Furthermore, some of these proposals also attempt to retain at least part of the working set in the cache when an application's working set is much larger than the cache size. A number of cache insertion policies have also been studied by previous proposals [51, 101, 94, 121, 45]. These policies use information such as the memory region of an accessed address, instruction pointer to predict the reuse behavior of a missed cache block and insert blocks with higher reuse closer to the most recently used position such that these blocks are not evicted immediately. Other previous works [95, 9, 106, 19, 43, 59] propose to partition the cache between applications such that applications that have better utility for the cache are allocated more cache space. While these previous proposals aim to improve system performance, they are not designed with the objective of providing controllable performance.

# 2.7 Related Work on Coordinated Cache and Memory Management

While several previous works have proposed techniques to manage the shared cache capacity and main memory bandwidth independently, there have been few previous works that have coordinated the management of these resources. Bitirgen et al. [14] propose a coordinated resource management scheme that employs machine learning, specifically, an artificial neural network, to predict each application's performance for different possible resource allocations. Resources are then allocated appropriately to different applications such that a global system performance metric is optimized. More recently, Wang et al. [119] employ a market-dynamics-inspired mechanism to coordinate allocation decisions across resources. We take a different and more general approach and propose a model that accurately estimates application slowdowns. Our model can be used as an effective substrate to build coordinated resource allocation policies that leverage our slowdown estimates to achieve different goals such as high performance, fairness and controllable performance.

#### 2.8 Related Work on Cache and Memory QoS

Several prior works have attempted to provide QoS guarantees in shared memory multicore systems. Previous works have proposed techniques to estimate applications' sensitivity to interference/propensity to cause interference by profiling applications offline (e.g., [77, 31, 29, 30]). However, in several scenarios, such offline profiling of applications might not be feasible or accurate. For instance, in a cloud service, where any user can run a job using the available resources in a pay-as-you-go manner, profiling every application offline to gain a priori application knowledge can be prohibitive. In other cases, where the resource usage of an application is heavily input set dependent, the profile may not be representative. Mars et al. [123] also attempt to estimate

applications' sensitivity to/propensity to cause interference online. However, they assume that applications run by themselves at different points in time, allowing for such profiling, which might not necessarily be true for all applications and systems. Our techniques, on the other hand, strive to control and bound application slowdowns without relying on any offline profiling and are therefore more generally applicable to different systems and scenarios.

Iyer et al. [39, 43, 44], Guo et al. [37] propose mechanisms to provide guarantees on shared cache space, memory bandwidth or IPC for different applications. Kasture and Sanchez [54] propose to partition shared caches with the goal of reducing the tail latency of latency critical workloads. Nesbit et al. [89] propose a mechanism to enforce a memory bandwidth allocation policy – partition the available memory bandwidth across concurrently running applications based on a given bandwidth allocation. Most of these policies aim to provide guarantees on resource allocation. Our goal, on the other hand, is to provide soft guarantees on application slowdowns.

#### 2.9 Related Work on Storage QoS

A large body of previous work has tackled the challenge of providing QoS in the presence of contention between different applications for storage bandwidth. Several systems employ bandwidth-based throttling (e.g., [16, 18, 120, 52]) to ensure that some applications do not hog storage bandwidth, at the cost of degrading other applications' performance. One such system, YFQ [16] controls the proportions of bandwidth different applications receive by assigning priority. Other systems such as SLEDS [18] and Zygaria [120] employ a leaky bucket type model that controls the bandwidth of each workload, while provisioning for some burstiness.

Other systems employ deadline-based throttling (e.g., [81, 102, 74]) that attempts to provide latency guarantees for each request. RT-FS [81] uses the notion of slack to provide more resources to other applications. Cello [102] deals with two kinds of requests, ones that need to meet real-time latency requirements and others that do not need to meet such requirements. Cello tries to balance the needs of these two kinds of requests. Facade [74] tailors its latency guarantees depending on

an application's demand in terms of number of requests. More recent work such as Argon [116] takes into account that the system could be oversubscribed and determines feasibility of meeting utilization requirements and then seeks to provide guarantees in terms of utilization.

While all these previous works are effective in providing different kinds of QoS at the storage, they do not take into account main memory bandwidth and shared cache capacity contention, which is the focus of our work.

#### 2.10 Related Work on Interconnect QoS

Several previous works have tackled the problem of achieving QoS in the context of both off-chip and on-chip networks. Fair queueing [24] emulates round-robin service order among different flows. Virtual clock [125] provides a deadline-based scheme that effectively time-division multiplexes slots among different flows. While these approaches are rate-based, other previous works are frame-based. Time is divided into epochs or frames and different flows reserve slots within a frame. Some examples of frame-based policies are rotated combined queueing [58] and globally synchronized frames [68]. Other previous work [105] proposes simple bandwidth allocation schemes that reduce the complexity of allocation in the intermediate router nodes.

Grot et al. [36] propose the preemptive virtual clock mechanism that enables reclamation of idle resources, without adding significant buffer overhead. This mechanism preempts low-priority requests in order to provide better QoS to higher priority requests. Grot et al. also propose Kilo-NOC [35], an NoC architecture designed to be scalable to large systems. This proposal reduces the amount of hardware changes required at every node, achieving low router complexity. Das et al. in [22] propose to employ stall time criticality information to distinguish between and prioritize different applications' packets at routers. Das et al. also propose Aergia [23] to further distinguish between packets of the same application, based on slack.

Our work on cache and memory QoS can be combined with these previous works on intercon-

nect QoS to achieve comprehensive and effective QoS at the system level.

#### 2.11 Related Work on Online Slowdown Estimation

Eyerman and Eeckhout [33] and Cazorla et al. [17] propose mechanisms to determine an application's slowdown while it is running alongside other applications on an SMT processor. Luque et al. [76] estimate application slowdowns in the presence of shared cache interference. Both these studies assume a fixed latency for accessing main memory, and hence do not take into account interference at the main memory.

While a large body of previous work has focused on main memory and shared cache interference reduction techniques, few previous works have proposed techniques to estimate application slowdowns in the presence of main memory and cache interference.

Li et al [69] propose a scheme to estimate the impact of memory stall times on performance, for different applications, in the context of hybrid memory system with DRAM and phase change memory (PCM). The goal of this work is to leverage this performance estimation scheme to map pages appropriately to DRAM and PCM with the goal of improving performance. Hence, this scheme does not focus much on very accurate performance estimation.

Stall Time Fair Memory Scheduling (STFM) [86] is one previous work that attempts to estimate each application's slowdown induced by memory interference, with the goal of improving fairness by prioritizing the most slowed down application. STFM estimates an application's slowdown as the ratio of its memory stall time when it is run alone versus when it is concurrently run alongside other applications.

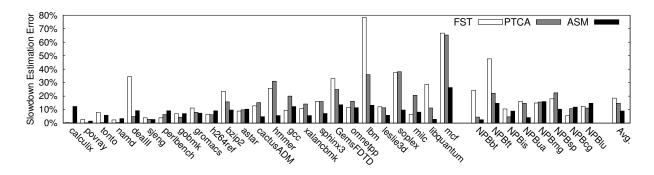

Fairness via Source Throttling (FST) [27] and Per-thread cycle accounting (PTCA) [25] estimate application slowdowns due to both shared cache capacity and main memory bandwidth interference. They compute slowdown as the ratio of alone and shared execution times and estimate alone execution time by determining the number of cycles by which each request is delayed.

Both FST and PTCA use a mechanism similar to STFM to quantify interference at the main memory. To quantify interference at the shared cache, both mechanisms determine which accesses of an application miss in the shared cache but would have been hits had the application been run alone on the system (contention misses), and compute the number of additional cycles taken to serve each contention miss. The main difference between FST and PTCA is in the mechanism they use to identify a contention miss. FST uses a pollution filter for each application that tracks the blocks of the application that were evicted by other applications. Any access that misses in the cache and hits in the pollution filter is considered a contention miss. On the other hand, PTCA uses an auxiliary tag store for each application that tracks the state of the cache had the application been running alone on the system. PTCA classifies any access that misses in the cache and hits in the auxiliary tag store as a contention miss.

The challenge in all these approaches is in determining the alone stall time or execution time of an application *while* the application is actually running alongside other applications. STFM, FST and PTCA attempt to address this challenge by counting the number of cycles by which each individual request that stalls execution impacts execution time. This is fundamentally difficult and results in high inaccuracies in slowdown estimation, as we will describe in more detail in Chapters 4 and 6.

# **Chapter 3**

# Mitigating Memory Bandwidth Interference Towards Achieving High Performance

The prevalent solution direction to tackle the problem of memory bandwidth interference is application-aware memory request scheduling, as we describe in Chapter 2. State-of-the-art application-aware memory schedulers attempt to achieve two main goals - high system performance and high fairness. However, previous schedulers have two major shortcomings. First, these schedulers increase hardware complexity in order to achieve high system performance and fairness. Specifically, most of these schedulers rank individual applications with a total order, based on their memory access characteristics (e.g., [87, 83, 60, 61]). Scheduling requests based on a total rank order incurs high hardware complexity, slowing down the memory scheduler significantly. For instance, the critical path latency for TCM increases by 8x (area increases by 1.8x) compared to an application-unaware FRFCFS scheduler, as we demonstrate in Section 3.5.2. Such high critical path delays in the scheduler directly increase the time it takes to schedule a request, potentially making the memory controller latency a bottleneck. Second, a total-order ranking is unfair to applications at the bottom of the ranking stack. Even shuffling the ranks periodically (like TCM does) does not fully mitigate the unfairness and slowdowns experienced by an application when it is at the bottom of the ranking stack, as we describe in more detail in Section 3.1.

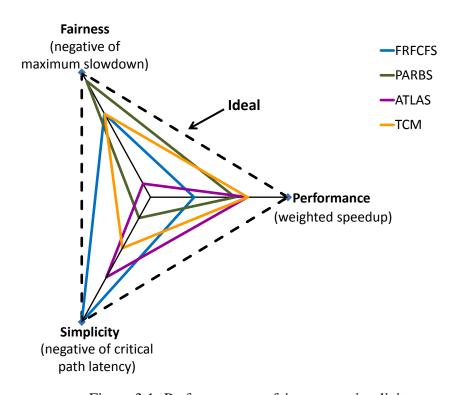

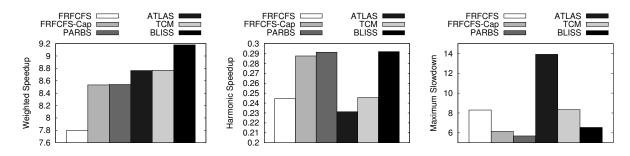

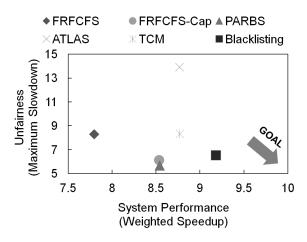

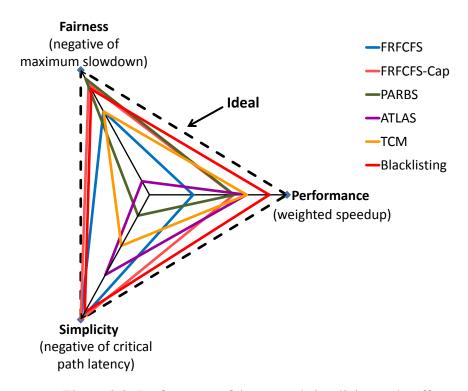

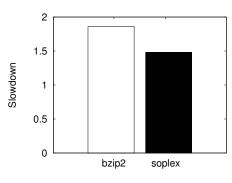

Figure 3.1 compares four major previous schedulers using a three-dimensional plot with performance, fairness and simplicity on three different axes.<sup>1</sup> On the fairness axis, we plot the negative of maximum slowdown, and on the simplicity axis, we plot the negative of critical path latency. Hence, the ideal scheduler would have high performance, fairness and simplicity, as indicated by the black triangle. As can be seen, previous ranking-based schedulers, PARBS, ATLAS and TCM, increase complexity significantly, compared to the currently employed FRFCFS scheduler, in order to achieve high performance and/or fairness.

Figure 3.1: Performance vs. fairness vs. simplicity

**Our goal**, in this work, is to design a new memory scheduler that does not suffer from these shortcomings: one that achieves high system performance and fairness *while* incurring low hardware cost and complexity. To this end, we seek to overcome these shortcomings by exploring an alternative means to protecting vulnerable applications from interference and propose the *Black-listing memory scheduler (BLISS)*.

<sup>&</sup>lt;sup>1</sup>Results across 80 simulated workloads on a 24-core, 4-channel system. Section 3.4 describes our methodology and metrics.

#### 3.1 Key Observations

We build our Blacklisting memory scheduler (BLISS) based on two key observations.

**Observation 1.** Separating applications into only two groups (interference-causing and vulnerable-to-interference), without ranking individual applications using a total order, is sufficient to mitigate inter-application interference. This leads to higher performance, fairness and lower complexity, all at the same time.

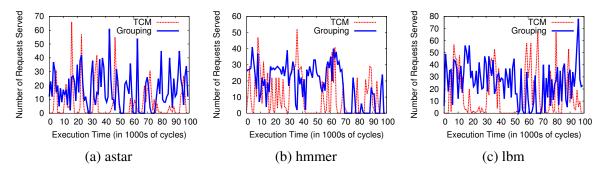

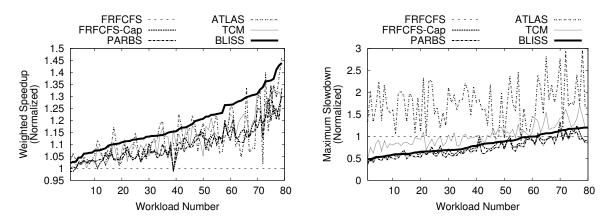

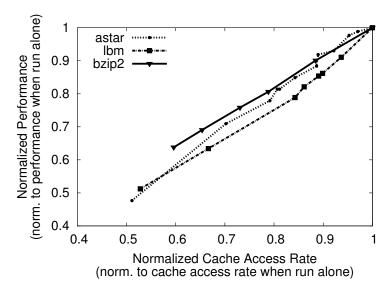

We observe that applications that are vulnerable to interference can be protected from interference-causing applications by simply separating them into two groups, one containing interference-causing applications and another containing vulnerable-to-interference applications, rather than ranking individual applications with a total order as many state-of-the-art schedulers do. To motivate this, we contrast TCM [61], which clusters applications into two groups and employs a total rank order within each cluster, with a simple scheduling mechanism (*Grouping*) that simply groups applications only into two groups, based on memory intensity (as TCM does), and prioritizes the low-intensity group *without* employing ranking in each group. *Grouping* uses the FRFCFS policy within each group. Figure 3.2 shows the number of requests served during a 100,000 cycle period at intervals of 1,000 cycles, for three representative applications, astar, hmmer and lbm from the SPEC CPU2006 benchmark suite [6], using these two schedulers.<sup>2</sup> These three applications are executed with other applications in a simulated 24-core 4-channel system.<sup>3</sup>

Figure 3.2 shows that TCM has high variance in the number of requests served across time, with very few requests being served during several intervals and many requests being served during a few intervals. This behavior is seen in most applications in the high-memory-intensity cluster since TCM ranks individual applications with a total order. This ranking causes some high-memory-intensity applications' requests to be prioritized over *other* high-memory-intensity applications'

<sup>&</sup>lt;sup>2</sup>All these three applications are in the high-memory-intensity group. We found very similar behavior in all other such applications we examined.

<sup>&</sup>lt;sup>3</sup>See Section 3.4 for our methodology.

requests, at any point in time, resulting in high interference. Although TCM periodically shuffles this total-order ranking, we observe that an application benefits from ranking *only* during those periods when it is ranked very high. These very highly ranked periods correspond to the spikes in the number of requests served (for TCM) in Figure 3.2 for that application. During the other periods of time when an application is ranked lower (i.e., most of the *shuffling intervals*), only a small number of its requests are served, resulting in very slow progress. Therefore, most high-memory-intensity applications experience high slowdowns due to the total-order ranking employed by TCM.

Figure 3.2: Request service distribution over time with TCM and Grouping schedulers

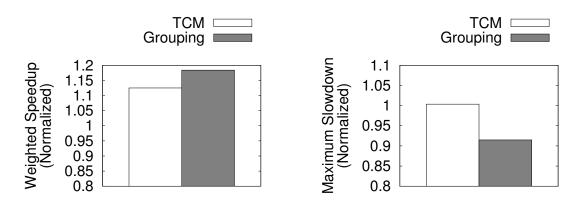

On the other hand, when applications are separated into only two groups based on memory intensity and no per-application ranking is employed within a group, some interference exists among applications within each group (due to the application-unaware FRFCFS scheduling in each group). In the high-memory-intensity group, this interference contributes to the few low-request-service periods seen for *Grouping* in Figure 3.2. However, the request service behavior of *Grouping* is less spiky than that of TCM, resulting in lower memory stall times and a more steady and overall higher progress rate for high-memory-intensity applications, as compared to when applications are ranked in a total order. In the low-memory-intensity group, there is not much of a difference between TCM and *Grouping*, since applications anyway have low memory intensities and hence, do not cause significant interference to each other. Therefore, *Grouping* results in higher system performance and significantly higher fairness than TCM, as shown in Figure 3.3 (across 80 24-core workloads on a simulated 4-channel system).

Figure 3.3: Performance and fairness of Grouping vs. TCM

Grouping applications into two groups also requires much lower hardware overhead than ranking-based schedulers that incur high overhead for computing and enforcing a total rank order for all applications. Therefore, grouping can not only achieve better system performance and fairness than ranking, but it also can do so while incurring lower hardware cost. However, classifying applications into two groups at coarse time granularities, on the order of a few million cycles, like TCM's clustering mechanism does (and like what we have evaluated in Figure 3.3), can still cause unfair application slowdowns. This is because applications in one group would be deprioritized for a long time interval, which is especially dangerous if application behavior changes during the interval. Our second observation, which we describe next, minimizes such unfairness and at the same time reduces the complexity of grouping even further.

**Observation 2.** Applications can be classified into interference-causing and vulnerable-to-interference groups by monitoring the number of consecutive requests served from each application at the memory controller. This leads to higher fairness and lower complexity, at the same time, than grouping schemes that rely on coarse-grained memory intensity measurement.

Previous work actually attempted to perform grouping, along with ranking, to mitigate interference. Specifically, TCM [61] ranks applications by memory intensity and classifies applications that make up a certain fraction of the total memory bandwidth usage into a *group* called the *low-memory-intensity cluster* and the remaining applications into a second group called the *high-memory-intensity cluster*. While employing such a grouping scheme, without ranking individual

applications, reduces hardware complexity and unfairness compared to a total order based ranking scheme (as we show in Figure 3.3), it i) can still cause unfair slowdowns due to classifying applications into groups at coarse time granularities, which is especially dangerous if application behavior changes during an interval, and ii) incurs additional hardware overhead and scheduling latency to compute and rank applications by long-term memory intensity and total memory bandwidth usage.