# COLLECTED WISC PAPERS

(

$\left\{ \begin{array}{c} \end{array} \right\}$

1

$\left( \right)$

June 1987

# WISC Technologies, Inc.

La Honda, CA 94020

First Printing June 1987 Second Printing June 1987 λ

1

<u>≬</u> ≺\_∕

4

d.

$K \rightarrow$

A L

Copyright 1986, 1987

WISC Technologies, Inc. Box 429 Star Route 2 La Honda, CA 94020

# PREFACE

WISC Technologies, Inc. was incorporated in the State of California in March, 1987. The Company is dedicated to the development of new technologies in computer software and hardware design. These papers describe the work we have done.

The original CPU/16 was shown at the San Francisco Computer Faire in 1986. We were pleased that BYTE noted our product in their What's New section of the June 1986 issue.

At the 1986 Rochester Convention, two papers were presented on the history and architecture of the product.

BYTE invited two papers from Phil Koopman, Jr. The first was in their January 1987 issue featuring Programmable Hardware. The second was in their April 1987 issue featuring Instruction Set Strategies.

At the 1987 Rochester Forth Conference with the theme Computer Architectures, Glen B. Haydon presented a paper entitled "A Unification of Software and Hardware; A New Tool for Human Thought" and Phil Koopman Jr. presented an invited paper entitled "Writable Instruction Set, Stack Oriented Computers: The WISC Concept".

These papers are collected in this publication to provide convenient access to the background history and the problems addressed by WISC Technologies, Inc. in their development of computer architectures to implement the WISC concepts.

The WISC CPU/16 and WISC CPU/32 are available for immediate delivery.

i

June 1987

P.K. and G.B.H.

# CONTENTS

i

# PREFACE

| Microcoded IBM PC Board<br>BYTE, June 1986                                                                                                |     |   |     |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|---|-----|

| MVP Microcoded CPU/16; History<br>Glen B. Haydon & Phil Koopman, Jr.<br>1986 Rochester Forth Conference, June 1986                        |     |   |     |

| MVP Microcoded CPU/16; Architecture<br>Phil Koopman, Jr. & Glen B. Haydon<br>1986 Rochester Forth Conference, June 1986                   | . * | · | · . |

| Microcoded Versus Hard-Wired Control<br>Phil Koopman, Jr.<br>BYTE, January 1987                                                           |     | • |     |

| The WISC Concept<br>Phil Koopman, Jr.<br>BYTE, April 1987                                                                                 |     |   | •   |

| A Unification of Software and Hardware;<br>A New Tool for Human Thought<br>Glen B. Haydon<br>1987 Rochester Forth Conference, June 1987   |     |   |     |

| Writable Instruction Set, Stack Oriented Computer;<br>The WISC Concept<br>Phil Koopman, Jr.<br>1987 Rochester Forth Conference, June 1987 |     |   |     |

| Stack Oriented WISC Machine                                                                                                               |     |   |     |

1986 WISC Product Announcement

iii

1

# WHAT'S NEW

# Microcoded IBM PC Board

esigned for building customized processors, the MVP Microcoded CPU/16 from Mountain View Press is an add-on board for the IBM PC that implements a high-speed microcoded processor. A wire-wrapped prototype of the board. which MVP demonstrated at the West Coast Computer Faire in April, ran one FORTH test program 50 times faster than an IBM PC alone. According to the company, the processor can execute over 2 million stack operations per second

The card's 74-chip design includes a 16-bit ALU two hardware stacks. an interface to the IBM PC. 128K bytes of static memory. a program counter. two 16-bit data registers. and room for 256 microcoded processor instructions. Each microcoded instruction is defined by up to eight 32-bit user-definable microcode instructions.

An Engineering Prototype Kit is available for \$1500. and a printed circuit board version should be available this month. MVP includes the following software with the wire-wrap kit. MVP FORTH/16 a word-oriented FORTH that executes directly in the processor: the MVP-FORTH Programmer's Kit: a Number Extensions package: a microcode assembler: a cross-compiler: a set of diagnostic programs. and source code for all the preceding software

For more information, contact Mountain View Press Inc. POB 4656, Mountain View, CA 94040, (415) 961-4103 Inquiry **558**.

34 BYTE . JUNE 1986

# MVP MICROCODED CPU/16

HISTORY

Glen B. Haydon Haydon Enterprises Box 429 Route 2 La Honda, CA 94020

Phil Koopman Jr. 20 Cattail Lane No. Kingstown, RI 02852

INTRODUCTON

The MVP-MICROCODED CPU/16 design resembles that conceived in the ALCOR project in developing an ALGOL translator utilizing multiple hardware stacks combined with the powerful techniques of a freely microcodable processor implemented in discrete components. In the present form of the CPU/16 design, the user is free to structure the processor according to application requirements for optimal efficiency.

# HISTORY

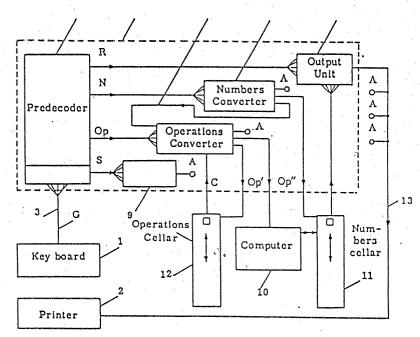

The ALCOR project was led by Samelson and Bauer during the 1950s. Its goal was to provide a direct method for translation of ALGOL. They conceived of a hardware design with two "cellars", one was to hold operational characters and the other to hold numbers. In modern terminology these would be called stacks. They are hardware storage devices based on a last in first out scheme. A block diagram of their concept, Figure 1, has been included in several papers.

8

7

6

5

à.

FIG. 1.

It appears that a hardware implementation of the ALCOR design was never completed. Computer processor designs took another direction. A stack operation was often included but with the stack memory mapped into a portion of the system's memory. Such stacks are usually used to store the return location for subroutine calls and sometimes to preserve other values.

In the late 1960s, Charles Moore designed a scheme of programming also using two stacks. One stack contained the return addresses of successive subroutine calls and the other stored interim data values during computation. Unfortunately, he could find no hardware designed to fulfill his needs and resorted to emulating such a processor. Such emulations are available on many systems today. They are known as a FORTH kernel.

A second consideration in the CPU/16 design is similar to that adopted by Seymore Cray. In his Cray computer design, he used discrete components. His claim was that it was the only way to get speed. Of course the Cray design utilized many other features but the basic idea was that faster processo.'s could be implemented utilizing simple components.

The Cray computers used a Data General Eclipse as a host giving access to the outside world. In a similar manner the CPU/16 uses an IBM compatible as a host providing I/O to the outside world. With only minor changes, the CPU/16 could use any common microcomputer.

Finally, the concept of microcoding a simple processor has been utilized in many different ways. Specific microcodable devices have been designed and are commercially available. Examination of these devices suggested that we could design a simple processor with discrete components which could be microcoded and provide even greater versatility and speed.

# RESULTS

The end result of these ideas is presently operational and available in kit form. It provides an ideal tool for exploring the potential of the design and as a learning medium. Unfortunately, many people are reluctant to undertake a wire wrapping exercise requiring 30 to 40 hours. However, utilizing the single stepping capabilities from the host, any portion of the processor can be exercised step by step. There is no better way to learn at first hand the capabilities of a multistack microcodable processor.

## WORK IN PROGRESS

Now that the CPU/16 design of the kit has stabilized, the next step is to produce that design on printed circuit boards to be placed in the IBM FC compatible. A problem with such a board is that it is no longer simple to change a wire corresponding to a bit in the microcode. The printed circuit board is no longer the experimental tool at the hardware level.

The CPU/16 design is currently being laid out and wire wrapped on a pair of S-100 system boards. It will run with an implementation of MVP-FORTH on an S-100 bus system. There is also interest in implementing the CPU/16 design utilizing the Apple II series of computers as the host.

# NEXT GENERATION

Where to from here? The 16-bit bus of the present design is limited to 16-bits of address space. By addressing on word boundaries, the system can address 128K bytes. But without some form of bank switching, virtual memory or some other technique, the size of memory is limited. Intel has overcome this limitation by utilizing several base segments from which addresses can be indexed. This is in essence a form of bank switching although it has been efficiently implemented.

The next bus size to consider is 32-bits wide. Intermediate numbers of address bits can be used but efficiency dictates the next size limitation at twice the size of the 16-bit limit. Using a 32-bit bus in a manner analogous to the current 16-bit design and adding a number of enhancements, a significant further increase in performance is anticipated. Also a billion 32-bit words (4-giga-bytes) of contiguous memory could be addressed without some form of bank switching. Part of the engineering prototype for a CPU/32 based on these considerations is already completed and functional.

The CPU/16 kit is an ideal hardware system with which to study other architectures. For example, the design is clearly not a RISC machine as currently described. However, by addressing items in the dedicated stack memory with optimized microcode, it would be possible to treat stack RAM as an array of registers and emulate a RISC design. In such an implementation, the RISC architecture could be thought of as a subset of the capabilities of the CPU/32 processor.

### LANGUAGES

The MVP CPU design lends itself to the efficient implementation of a wide variety of high level languages. For example Smalltalk-80 uses approximately 100 primitives each of which could be implemented in microcode. The design would be ideal for implementation of a p-code machine.

FORTH has been used in the initial phases of this work. FORTH is, after all, an emulation of the hardware design. The language has the advantage of ease of interactive programming and access to all hardware components. The diagnostic suite, micro-assembler and cross-compiler were easily developed with a minimum of effort. The language also provides a versatile facility for programming many applications.

However, with the desirability of making the system compatible with other existing programs, it would be desirable to have a common operating system available. One route to a popular operating system would be to first implement the C language. Already, one group is working to implement Small C. With a full implementation of C, the entire UNIX system could be added.

With the versatility of a microcodable processor, the development of new languages tailored to specific applications becomes more reasonable. The languages of LISP and PROLOG are just a beginning in the field of artificial intelligence and they have been implemented in FORTH. It should be relatively easy to move such implementations to the newly designed processor.

# CONCLUSIONS

The MVP CPU design provides flexibility in designing and using hardware to solve many application problems. In addition, many high level languages could be implemented on such a system with excellent efficiency. Initially, FCRTH has been chosen as the as the host and processor language. As such, the system complements a variety of other commercially available implementations of FORTH in hardware. The MVP CPU series of products provides flexibility for experimentation and tailoring the processor to specific application and a tool for teaching and testing a variety of hardware processor designs.

The kit would make an ideal starting point for a comprehensive computer science course sequence. Such a sequence might start with the building of the kit as a microcodable processor. That might be followed with the writing of the software for a compiler and an operating system. The series might conclude with a significant application utilizing the tools which were developed.

The fundamental philosophy has been to examine programming requirements of the application at hand, and design the hardware accordingly. It is a shame to have the hardware limitations drive the programming and limit the solution of the application. The present design is a stage in the evolution of hardware to solve problems. Perhaps more than two stacks would be desirable in some applications. Once a design is found for a specific application, the next step would be to cast that design in silicon. But con't get the cart before the horse.

# BIBLIOGRAPHY

Bauer. Fredrich L., Between Zuse and Rutishauser- The Early Development of Digital Computing in Central Europe., in A History of Computing in the Twentieth Century, N. Metropolis, J. Howlet, and Gain-Carlo Rota, Editors, Academic Press 1980.

Note: This volume is a treasury of historical ideas which are unknown to many workers in various branches of computer science today.

# MVP MICROCODED CPU/16 ARCHITECTURE

Phil Koopman Jr. 20 Cattail Lane No. Kingstown, RI 02852

Glen Haydon Haydon Enterprises Box 429 Route 2 La Honda, CA 94020

# ABSTRACT

The MVP Microcoded CPU/16 is a 16-bit coprocessor board that directly executes high level stack-oriented programs. The CPU/16 may be micro-programmed to execute any stackoriented language. FORTH was used as the initial implementation language to reduce development time and costs.

# INTRODUCTION

Modern computer languages and compilers rely heavily on the concept of the push-down stack. However, conventional computers are optimized for register-oriented operations and impose large memory access time penalties when using stacks residing in main memory. The CPU/16 stack-oriented coprocessor can improve the performance of a personal computer to equal that of a much more expensive mini-computer for programs that make heavy use of stacks.

The MVP Microcoded CPU/16 was designed as a "low tech" exploration tool for stack-oriented processing. The result is an inexpensive commercial system that:

1) Uses simple, inexpensive, commonly available components.

2) Minimizes hardware and software development tool costs.

3) Fits the basic system onto a single IBM compatible

Personal Computer expansion board (13" x 4").

4) Maximizes flexibility and minimizes complexity.

5) Achieves a 20 to 50 times speed improvement over 8088 MVP FORTH.

# SYSTEM ARCHITECTURE

The CPU/16 is implemented in only 74 ICs (with 8k words of program memory), with no custom or semi-custom chips required. 74xx and 74LSxx series ICs provide all logic functions, with 120ns CMOS static RAMs for microcode and program memory.

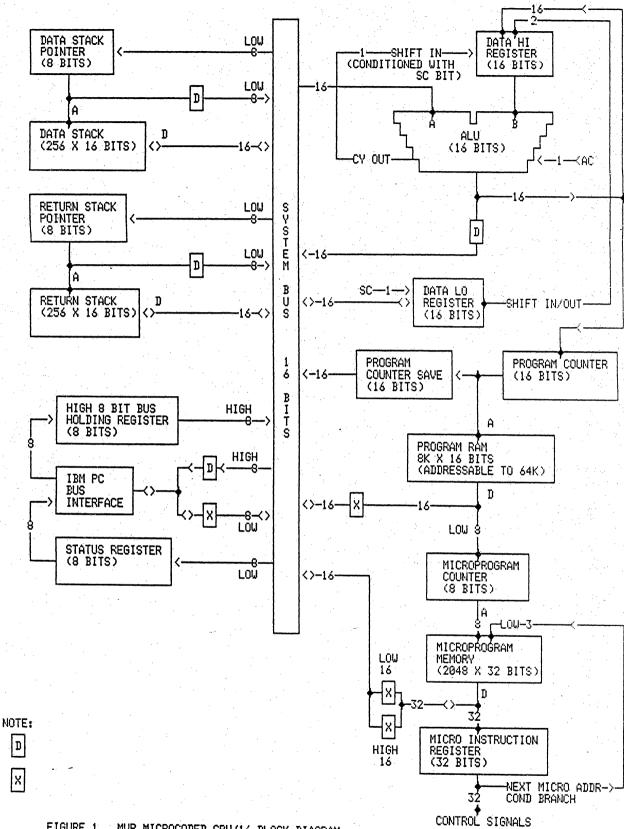

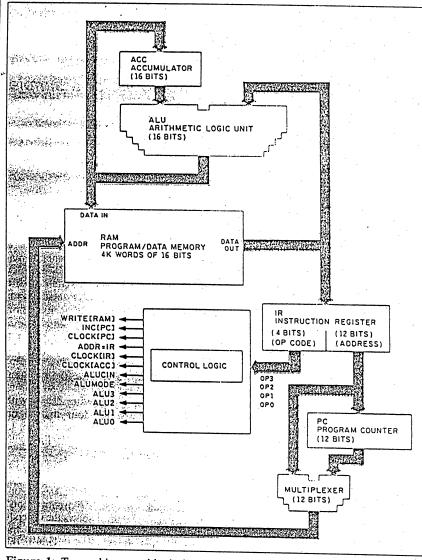

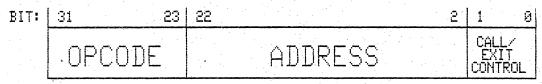

Figure 1 shows the architectural structure of the CPU/16. All data paths are 16 bits wide.

The CPU/16 plugs into an IBM compatible personal computer as a one-slot expansion board. The host interface on the CPU/16 allows the personal computer to alter registers and memory as well as single-step programs at the microcode or macrocode level. When the CPU/16 is in

V L

(i j

11 1

m.

À Ì

1

AL

1

<u>بن</u>ے اِ اِ

V.

"master" mode, the personal computer waits for the CPU/16 to request I/O service through the status register.

The return stack and data stack are hardware stacks with 8-bit pointers addressing 256 elements of stack memory. The stacks may be accessed and pointers incremented or decremented in a single clock cycle.

The ALU is built from 74LS181 chips, and has two shift registers to hold intermediate results. The Data Hi register and the Data Lo register can be shifted together as a 32-bit register for multiplication and division. The Data Hi register normally contains the top data stack element.

Program memory is organized as 64k words of 16 bits. All but the last 256 words may be used for program memory. A 16-bit program counter is used for all memory access addressing. The separate memory address bus from the program counter allows overlapped instruction fetching and execution. Program memory expansion beyond 8k words requires a daughter-board.

Micro-program memory is organized as 2k words of 32 The microcode bit format is typical of bits. modern horizontally microcoded machines. The micro-program counter and micro-instruction register allow overlapped fetching and execution of micro-instructions. Conditional microcode branches and microcode looping are accomplished by manipulation of the low order 3 bits of the micro-program address. If, during macro-instruction decoding, the highest bits of a macro-instruction are not all 8 1, the microprogram counter is forced to all zero's, executing a DOCOL subroutine call. If the highest 8 bits are all 1, then one of 256 possible microcoded primitives is executed.

# SOFTWARE SUPPORT

FORTH was picked as the CPU/16's development language for its efficiency, its simplicity compiler of implementation, and its friendly interactive environment with easy access to hardware resources. The CPU/16 supporting software includes a host control program, a microcode assembler, and a FORTH cross-assembler, as well as FORTH the microcode and kernel for the CPU/16implementation.

host program, microcode assembler, and The crossare written compiler MVP-FORTH. The in 8088 CPU/16 an MVP-FORTH currently uses kernel that differs in functionality from the 8088 MVP-FORTH version in that it uses word-oriented instead of byte-oriented memory addressing. In addition to FORTH, the CPU/16 is capable of supporting other programming languages such as Modula 2, Pascal, Lisp, and C. Any compiler implemented in machineindependent MVP-FORTH can be quickly installed on the CPU/16.

Current applications available on the CPU/16 include double-precision and quad-precision integer arithmetic and single-precision floating point math packages.

# PERFORMANCE

The CPU/16 runs at a 4.77 MHz micro-cycle rate. An "average" microcoded primitive executes in 3 clock cycles (630 ns). This provides approximately a 20 to 50 times speed increase over 8088 MVP-FORTH programs operating at the same clock speed.

Since only half of the micro-program memory is required for the MVP-FORTH implementation, custom-written microcoded primitives may be added to a user's application to increase the speed of commonly used words. As an example, software stack manipulation words:

: INC[@] ( PTR-ADDR -> N ) DUP @ @ 1 ROT +!;

: DEC[!] ( N PTR-ADDR -> ) -1 OVER +! @ !; can each be implemented in 10 micro-cycles (2.10 us), a speed increase of greater than 300% over high-level definitions. The listing for INC[@] is given as an example of CPU/16 microcode:

177 OPCODE: INC[@] (ADDR -> N)0 :: SOURCE=ALU ALU=B DEST=PC ;; \ PC <- ADDR 1 :: SOURCE=ALU ALU=-1 DEST=DLO ;;  $\land$  DLO <- -1 2 :: SOURCE=RAM ALU=A+1 DEST=DHI ;; \ DHI <- POINTER+1 \ POINTER <- DHI 3 :: SOURCE=ALU ALU=B DEST=RAM ;; 4 :: SOURCE=DLO ALU=A+B DEST=PC INC[MPC] ;; \ PC <- PTR 5 :: JMP=000 ;; \ WAIT FOR RAM ACCESS, JMP TO NEXT PAGE 178 CURRENT-PAGE ! 0 :: SOURCE=RAM DEST=DLO ;; \ DLO <- DATA 1 :: SOURCE=PCSAVE ALU=A+1 DEST=PC ;; \ RESTORE PC 2 :: SOURCE=DLO ALU=A DEST=DHI DECODE ;; \ T.O.S. <- DATA 3 :: END ;; ∖ JMP TO NEXT INSTRUCTION

# FUTURE DEVELOPMENTS

Future developments for the CPU/16 will focus on broadening the range of languages and application programs available. Potential applications for a stack-oriented processor include: artificial intelligence, computer graphics, image processing, real-time control, and efficient execution of modern computer languages.

The CPU/16 is the first in a family of stack-oriented processors. A 32-bit general-purpose stack-oriented processor with greater speed and memory addressability is currently in development.

# CONCLUSIONS

The MVP Microcoded CPU/16 is a high performance, general-purpose stack-oriented processor. A "low tech" approach has yielded significant speed improvements over current microprocessors at a modest cost. Compatibility with existing MVP-FORTH systems allows for easy porting of existing software to a high performance environment. PROGRAMMABLE HARDWARE

# Microcoded Versus Hard-wired Control

A comparison of two methods for implementing the control logic for a simple CPU

THE INSTRUCTION decoding and execution control sections of modern computers are prime areas for using programmable hardware. Two of the most widely used methods for designing CPU control sections in microprocessors, minicomputers, and mainframes are microcode and hard-wired logic. Each method has its advantages, and both are natural applications for programmable hardware devices.

## Architectural Description

I'll start by giving the specifications for a simple computer architecture, then walk through the implementation of this architecture using both microcoded and hardwired design strategies. While both approaches require the same description and specification groundwork, they use different schemes to generate control signals.

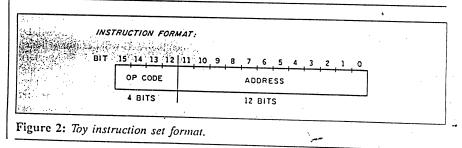

I will examine the CPU architecture of Toy, a fictitious computer designed especially for this article. The CPU has an accumulator (ACC), an arithmetic logic unit (ALU), an instruction register (IR), a program counter (PC), some random-access memory (RAM), and some control logic. Figure 1 is a block diagram of the Toy architecture. All data paths are 16 bits wide with 12-bit memory-address paths. You can directly implement the ALU, ACC, IR, PC, multiplexer, and RAM sections of Toy using commonly available chips. Toy's control-logic section will require detailed design and the use of customized hardware or a large number of combinatorial logic gates.

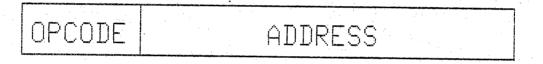

The Toy instruction format shown in figure 2 consists of a 4-bit op code and

# Phil Koopman

a 12-bit address field. The 16 implemented op codes are shown in table 1. Op codes 8 through 15 do not make use of the instruction's address field.

Since Toy is a single-accumulator machine, the instructions ADD, SUB, AND, OR, and XOR combine the contents of a memory location with the accumulator and return the result to the accumulator. The instructions STORE and LOAD transfer the accumulator to and from RAM. The instructions NOT, INC, DEC, and ZERO operate on the accumulator alone. While JMPZ is the only branching instruction, you can program an unconditional branch by following ZERO with a JMPZ. Finally, the four unused op codes act as null operations (NOPs) to eliminate the annoyance of dealing with illegal op codes.

### Control Logic

The control-logic section translates the opcode bit patterns into CPU-control and timing signals. Figure 1 shows the op-code inputs to the control-logic unit and the control-signal outputs required to run the rest of the CPU. The signals ALUO through ALUCIN control the ALU. (I based the bit assignments on those for the 74181 ALU chip. See The TTL Data Book, listed in the Bibliography.) If ALUMODE is a 1, then the ALU will perform a logical operation; if it's a 0, the ALU will perform an arithmetic operation. ALUO through ALU3 control which arithmetic or logic operation the ALU is performing. ALUCIN acts as the carry-in for the ALU. When the signal CLOCK[ACC] is a 1, the ACC register is loaded with the value of its inputs at the rising edge of the system clock. This is usually referred to as "clocking in" the contents of the ACC. When the signal CLOCK[IR] is a 1, the contents of the IR are clocked in from the RAM output. This is the mechanism used to decode the next op code. When ADDR=IR is a 1, the RAM address multiplexer places the contents of the IR address field onto the RAM address bus. When it is a 0, the PC is used to address RAM. I use the descriptor ADDR=PC to mean ADDR=IR is 0. When CLOCK[PC] is a 1 and the ACC is 0, the PC is loaded from the IR address field. When INC[PC] is a 1, the program counter is incremented by 1 at the end of the current clock cycle. When WRITE[RAM] is a 1, the RAM cell addressed by the RAM address bus is loaded with the output of the ALU; when this signal is a 0, the ALU is driven from the output of RAM.

# Functional Specifications

Now for the heart of how the Toy instruction set is implemented. In the Toy CPU, all instructions can be executed in just one or two clock cycles. Table 2 shows the actions required to complete each op code's function. Those actions in table 2 that arc continued

By day, Phil Koopman (20 Cattail Lane, North Kingston, RI 02852) is a U.S. Navy submariner and engineering duty officer; by night, he designs computer hardware, software, and microcode. not the control signals shown in figure 1 are macros for the ALU control bits whose value is given in table 3. Let's examine some representative op codes in detail.

The STORE op code stores the contents of ACC into RAM. For the first cycle of this instruction, the low 12 bits of the IR address RAM. The ALU routes the ACC contents through without modification, then writes them out to RAM. STORE requires two clock cycles since RAM is being used for accessing a data value during the first clock cycle. The second clock cycle is the same for all twocycle instructions; it is simply a decoding of the next op code.

The contents of the RAM address pointed to by the PC are put onto the RAM address bus to fetch the op code. They are then clocked into the IR, and continued

Figure 1: Toy architecture block diagram.

\_\_\_\_ ۲

111

~~~

1

| 14010 1. 10y                                                                       | instruction set.                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Op code                                                                            | Operation                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | STORE<br>LOAD<br>JMPZ<br>ADD<br>SUB<br>OR<br>AND<br>XOR<br>NOT<br>INC<br>DEC<br>ZERO<br>NOP<br>NOP<br>NOP | store accumulator in RAM at address<br>load ACC from RAM at address<br>jump to address if ACC is zero<br>add RAM to ACC<br>subtract RAM from ACC<br>logical OR RAM into ACC<br>logical AND RAM into ACC<br>logical AND RAM into ACC<br>logical XOR RAM into ACC<br>logical one's complement into ACC<br>add 1 to ACC<br>subtract 1 from ACC<br>place 0 in ACC<br>null operation — unused op code<br>null operation — unused op code<br>null operation — unused op code<br>null operation — unused op code |

Table 2: Toy functional specification. Note that ADDR=PC is equivalent to the ADDR=IR signal being 0. Also, I have used descriptive macro names for the ALU control bits (see table 3).

| Op code  | Operation | Cycle  | Specification                                                         |

|----------|-----------|--------|-----------------------------------------------------------------------|

| 0        | STORE     | 1<br>2 | ADDR=IR ; ALU=ACC ; WRITE[RAM]<br>ADDR=PC ; CLOCK[IR] ; INC[PC]       |

| <b>1</b> | LOAD      | 1 2    | ADDR=IR ; ALU=RAM ; CLOCK[ACC]<br>ADDR=PC ; CLOCK[IR] ; INC[PC]       |

| 2        | JMPZ      | 1<br>2 | CLOCK[PC]<br>ADDR=PC ; CLOCK[IR] ; INC[PC]                            |

| 3        | ADD       | 1<br>2 | ADDR=IR ; ALU=ACC+RAM ; CLOCK[ACC]<br>ADDR=PC ; CLOCK[IR] ; INC[PC]   |

| 4 .      | SUB       | 1<br>2 | ADDR=IR ; ALU=ACC-RAM ; CLOCK[ACC]<br>ADDR=PC ; CLOCK[IR] ; INC[PC]   |

| .5       | OR        | 1<br>2 | ADDR=IR ; ALU=ACCorRAM ; CLOCK[ACC]<br>ADDR=PC ; CLOCK[IR] ; INC[PC]  |

| 6        | AND       | 1<br>2 | ADDR=IR ; ALU=ACCandRAM ; CLOCK[ACC]<br>ADDR=PC ; CLOCK[IR] ; INC[PC] |

| 7        | XOR       | 1<br>2 | ADDR=IR ; ALU=ACCxorRAM ; CLOCK[ACC]<br>ADDR=PC ; CLOCK[IR] ; INC[PC] |

| 8        | NOTA      | 1      | ALU=notACC ; CLOCK[ACC] ;<br>ADDR=PC ; CLOCK[IR] ; INC[PC]            |

| 9        | INCA      | 1      | ALU=ACC+1 ; CLOCK[ACC] ; ADDR=PC ;<br>CLOCK[IR] ; INC[PC]             |

| 10       | DECA      | 1      | ALU=ACC-1 ; CLOCK[ACC] ;<br>ADDR=PC ; CLOCK[IR] ; INC[PC]             |

| . 11     | ZERO      | 1      | ALU=0 ; CLOCK[ACC] ;<br>ADDR=PC ; CLOCK[IR] ; INC[PC]                 |

| 12-15    | NOP       | 1      | ADDR=PC ; CLOCK[IR] ; INC[PC]                                         |

|          |           |        |                                                                       |

finally the PC is incremented so that it is pointing to the next op code.

JMPŽ accomplishes a conditional branch by loading the contents of the PC with the address in the IR. For this to be a conditional branch, the control signal to the PC loader must be ANDed with a signal that is only true if all the bits of the ACC are 0. Since the PC is loaded with the new instruction address at the end of the first clock cycle, the second cycle is a normal decoding instruction for this new address, identical to the second cycle of STORE.

| Table 3: Macros f<br>74181 ALU chip). | or the AL | l control | l bits (ba | sed on b | it assignmen | ts in the |

|---------------------------------------|-----------|-----------|------------|----------|--------------|-----------|

| Macro                                 | ALU0      | ALU1      | ALU2       | ALU3     | ALUMODE      | ALUCIN    |

| ALU = ACC         | 1 . | 1  | <u>1</u> | 1         | 1   | x   |

|-------------------|-----|----|----------|-----------|-----|-----|

| ALU = RAM         | 0   | 1  | 0        | 1 1 N N N | 1.1 | ×   |

| ALU = ACC + RAM   | 1   | 0  | 0        | 1         | -0  | 0   |

| ALU = ACC RAM     | Ó . | 1  | 1        | 0         | 0   | 1 . |

| ALU = ACC OR RAM  | Ο.  | 1  | 1        | 1         | - 1 | ×   |

| ALU = ACC AND RAM | 1 . | .1 | -0       | 1         | 1   | x   |

| ALU = ACC XOR RAM | 0   | 1  | 1        | 0         | 1   | x   |

| ALU = NOT ACC     | 0   | Ö  | 0        | 0         | 1   | ×   |

| ALU = ACC + 1     | Ó   | 0  | 0        | 0         | Ó   | 1   |

| ALU = ACC - 1     | 1   | 1  | 1        | 1         | õ   | 0   |

| ALU = 0           | 1   | 1  | 0        | 0         | 1   | x   |

|                   |     |    |          | · · · .   |     |     |

|        | Table 4: Control signal value specification.                                                                                    |                                                          |                                                          |                                                          |                                                |                                                     |                                                               |                                                               |                                                          |                                                     |                                                     |                                           |                                                          |                                                               |                                                          |                                                          |                                                          |

|--------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|

|        | Values for first clock cycle of each instruction                                                                                |                                                          |                                                          |                                                          |                                                |                                                     |                                                               |                                                               |                                                          |                                                     | ÷ ,                                                 |                                           |                                                          |                                                               |                                                          | ·                                                        |                                                          |

|        | Control<br>signal                                                                                                               | Op<br>0                                                  | code<br>1                                                |                                                          | 3                                              | 4                                                   | 5                                                             | 6                                                             | 7                                                        | 8                                                   | 9                                                   | 10                                        | 11                                                       | 12                                                            | 13                                                       | 14                                                       | 15                                                       |

| ۰<br>۱ | ALUO<br>ALU1<br>ALU2<br>ALU3<br>ALUMODE<br>ALUCIN<br>CLOCK[ACC]<br>CLOCK[R]<br>ADDR=IR<br>CLOCK[PC]<br>INC[PC]<br>WRITE[RAM]    | 1<br>1<br>1<br>1<br>1<br>x<br>0<br>0<br>1<br>0<br>1<br>0 | 0<br>1<br>0<br>1<br>1<br>x<br>1<br>0<br>1<br>0<br>0<br>0 | x<br>x<br>x<br>x<br>x<br>x<br>0<br>0<br>1<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>0 | 0<br>1<br>0<br>0<br>1<br>1<br>0<br>1<br>0<br>0<br>0 | 0<br>1<br>1<br>1<br>1<br>x<br>1<br>0<br>1<br>0<br>0<br>0      | 1<br>1<br>0<br>1<br>1<br>x<br>1<br>0<br>1<br>0<br>0<br>0      | 0<br>1<br>1<br>0<br>1<br>x<br>1<br>0<br>1<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>x<br>1<br>1<br>0<br>0<br>1<br>0 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>1<br>0 | 1<br>1<br>1<br>0<br>1<br>1<br>0<br>1<br>0 | 1<br>1<br>0<br>1<br>1<br>x<br>1<br>1<br>0<br>0<br>1<br>0 | ×<br>×<br>×<br>×<br>×<br>×<br>×<br>0<br>1<br>0<br>0<br>1<br>0 | x<br>x<br>x<br>x<br>x<br>x<br>0<br>1<br>0<br>0<br>1<br>0 | x<br>x<br>x<br>x<br>x<br>x<br>0<br>1<br>0<br>0<br>1<br>0 | x<br>x<br>x<br>x<br>x<br>0<br>1<br>0<br>0<br>1<br>0      |

|        | Values for seco                                                                                                                 |                                                          |                                                          | ·                                                        | e of                                           | eac                                                 | h in                                                          | struc                                                         | tion                                                     |                                                     | •.                                                  | •                                         |                                                          | •                                                             |                                                          |                                                          |                                                          |

|        | signal                                                                                                                          | Op<br>0                                                  |                                                          | 2                                                        | 3                                              | 4                                                   | 5                                                             | 6                                                             | 7                                                        | 8                                                   | 9                                                   | 10                                        | 11                                                       | 12                                                            | 13                                                       | 14                                                       | 15                                                       |

|        | ALU0<br>ALU1<br>ALU2<br>ALU3<br>ALUMODE<br>ALUCIN<br>CLOCK[ACC]<br>CLOCK[IR]<br>ADDR = IR<br>CLOCK[PC]<br>INC[PC]<br>WRITE[RAM] | x x x x x x 0 1 0 1 0                                    | x x x x x 010010                                         | x x x x x 0 1 0 0 1 0                                    | x x x x x x 0 1 0 0 1 0                        | x x x x x 0 1 0 0 1 0                               | x<br>x<br>x<br>x<br>x<br>x<br>x<br>0<br>1<br>0<br>0<br>1<br>0 | x<br>x<br>x<br>x<br>x<br>x<br>x<br>0<br>1<br>0<br>0<br>1<br>0 | ×<br>×<br>×<br>×<br>×<br>×<br>×<br>0<br>1<br>0<br>0      | * * * * * * * * * * *                               | × × × × × × × × × × × ×                             | × × × × × × × × × × × × ×                 | * * * * * * * * * * * * *                                | × × × × × × × × × × × × × × × × × × ×                         | × × × × × × × × × × × × × × × × × × ×                    | * * * * * * * * * * *                                    | ×<br>×<br>×<br>×<br>×<br>×<br>×<br>×<br>×<br>×<br>×<br>× |

The single-clock-cycle instructions. such as NOTA, do not require a RAM access for an operand. This means that the usual second-cycle decoding sequence can occur during the same clock cycle as the ALU operation that modifies the ACC contents. In the case of NOTA, the RAM input to the ALU is ignored while the ALU computes the one's complement (logical inverse) of the current ACC contents,

# Control-Logic Outputs

Table 4 gives a complete listing of all the control-logic output values that you need to specify the 'Toy functional description. Each X corresponds to a signal whose value does not matter, either because the controlled resource is unused (as in the ALU signals for op code 2) or because the second clock cycle is unused for op codes 8 to 15. These "don't-care" signals become crucial when you are designing hard-wired control circuitry.

# Hard-wired Control

A CPU designed with hard-wired control uses random logic such as AND, OR, and NOT gates and either flip-flops or counters to decode each op code and control the processing flow. The hard-wired design process usually consists of identifying all the states needed to implement the instruction set, then deriving the Boolean logic equations required to control the computer's resources for each step.

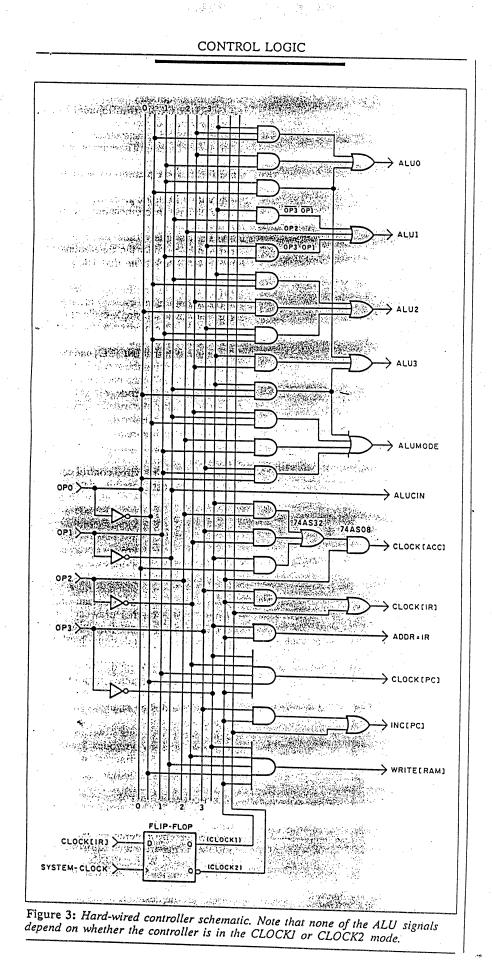

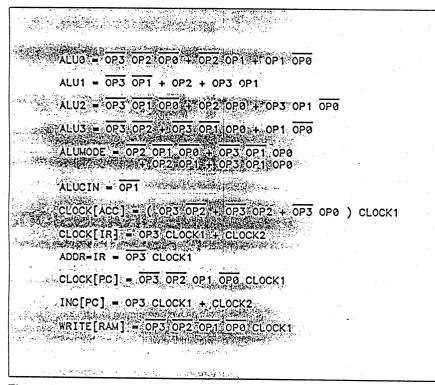

Figure 3 shows the hard-wired implementation of the functional specifications given in table 4. It requires a controller with two states: first clock cycle and second clock cycle. The flip-flop in figure 3 is forced to the CLOCK1 state whenever a new instruction is clocked into the IR and changes to the CLOCK2 state whenever the IR is not clocked.

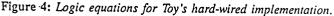

The most tedious part of a hard-wired control design is creating the logic gate networks to decode instructions into control signals. I have derived the required logic equations shown in figure 4 from the functional specifications in table 4. Figure 5 shows the Karnaugh map for deriving the first equation (ALU0) in figure 4. (See W. Fletcher's An Engineering Approach to Digital Design [Prentice-Hall, 1980] for a discussion of Karnaugh maps.)

The don't-care conditions are vital in reducing the complexity of the gate networks, since they allow freedom to ignore some op-code bits or state bits to minimize decoding logic. A good example of a don't-care condition is the ALU control signals; they do not depend on whether the controller is currently in the CLOCK1 or CLOCK2 mode.

continued

238 BYTE • JANUARY 1987

Figure 5: To show how the Boolean equations in figure 4 were derived from table 4, here is the Karnaugh map used to minimize the ALUO Boolean equation. The Xs are the don't-care bits, and the number in the upper right corner of each box is the op code.

To implement the hard-wired controller, the complementary outputs of the CLOCK1/CLOCK2 flip-flop and the inputs from the current op code in the IR are fed throughout the system by the lines at the left of figure 3. These inputs are then fed through logic gate combinations specified by the equations in figure 4. You can implement these logic-gate combinations with TTL logic gates or, if you want to save board space, program them into hardware, such as a PAL.

As an example of how these decoding gates work, consider the generation of the signal INC[PC]. The INC[PC] signal should be a 1 for op codes 8 to 15 on the first clock cycle and for op codes 0 to 7 on the second clock cycle. But, since op codes 8 to 15 are all single-cycle op codes, any signals generated from them during the second cycle can be ignored. This gives the result that INC[PC] can be 1 for all op codes during the second cycle. The logic for INC[PC] then becomes the AND of the highest op-code bit (OP3) and CLOCK1, with the result ORed with CLOCK2.

Because the time required for a signal to pass through a simple logic gate is only a few nanoseconds with most current technologies, hard-wired control can provide the fastest possible decoding of machine language instructions. It also is the most flexible design method for specifying unique and complex control flows within a CPU because the designer can specify any decoding gate combinations and any control-flow hardware.

One drawback to using hard-wired control methodology is that it requires a considerable amount of Boolean algebra manipulation. Another drawback is that the CPU must be completely and correctly specified before you design a hard-wired control unit.

Any additions or modifications to the specification can require a major redesign of the control unit. If you want a feel for the impact a design change can have on a hard-wired controller, try redoing the logic equations with two op codes switched, such as op codes 5 and 9, or with op code 15 defined as a two-cycle logical NAND instruction.

# Microcoded Control

Microcoded design differs from hardwired design in that the control-logic gates are replaced by a memory array (usually a ROM) to generate the required controllogic signals. While ROMs are slower than random logic within the same price and performance categories, using a ROM simplifies the design process and significantly reduces time and costs for implementing a CPU control circuit.

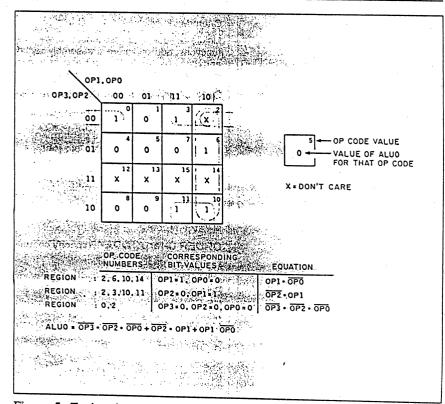

Figure 6 shows the schematic for a

microcoded control circuit for Toy. The op code and a flip-flop similar to the one used in the hard-wired controller are fed in as an address to the microprogram ROM. The outputs of the ROM directly drive the control signals for the CPU. Each ROM location contains the proper bit settings to control a single clock cycle of an op code's execution, as shown in figure 7.

The control signals for the first cycle of each op code are placed in the even memory addresses (which are addressed when the flip-flop in the controller outputs a 0 for the first clock cycle), and the second cycle op codes are placed in odd memory addresses. I have arbitrarily assigned the value 0 to all don't-care bits from table 4 and copied the rest of the bits directly from table 4 to figure 7.

The main advantage to microcoded control is that it lets the designer change the CPU's functional description by changing the bits in any ROM address without having to redesign the machine's logicdecoding gate structure. Microcoded machine design also lends itself to simply structured, low-component-count computers such as those built using bit-slice technology. Most modern microprocescontinued

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | 0.0                                       |                   |                   | <u> </u>          |                       |                                         |        |             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------|-------------------|-------------------|-------------------|-----------------------|-----------------------------------------|--------|-------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                           |                   |                   |                   |                       |                                         |        |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                           |                   |                   |                   |                       |                                         |        |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            | с.<br>1                                   | WR                | c c               | _                 |                       |                                         |        |             |

| and a second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •          |                                           | I<br>TI<br>EN     |                   | C<br>C<br>K A     | A<br>L                |                                         | •      |             |

| NUSPECT<br>CONSTRUCT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | terringer<br>Al-Abrian II                 | [ C<br>R [<br>A P | K D k             |                   |                       |                                         |        |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | OP<br>CODE | ROM<br>ADDRESS                            | мс<br>]]          | CIF<br>]R         | R C I<br>] ] N    | DUU<br>E32            |                                         |        | •           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.         | 0<br>- 1                                  | 1 e<br>0 1        | 0 1 0             | 00                | 1 1 1                 | 1 1 1                                   | • •    |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | * 1.<br>2  | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 0 0<br>0 1<br>0 0 | 00                | 100               | 000                   | 010<br>000<br>000                       | •<br>• | ۰.          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3          | 5                                         | 01<br>00          | 00                | 100               | 000                   | 300<br>301                              |        |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4          | 7<br>8<br>9                               | 0 1<br>0 0<br>0 1 | 010               |                   |                       | 300<br>110<br>300                       | . •    |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5          | 10<br>11                                  | 0 1               | 010               | 0 1 0<br>1 0 0    | 11                    | 1 1 0                                   |        | ar<br>An th |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6<br>7     | 12<br>13<br>14                            | 0 0<br>0 1<br>0 0 | 001               | 1.00              | 1 1 0<br>0 0 0<br>1 0 | 000                                     | ۰.     |             |

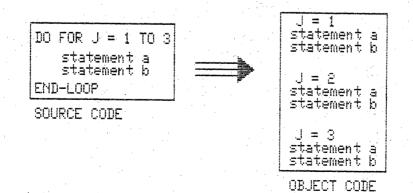

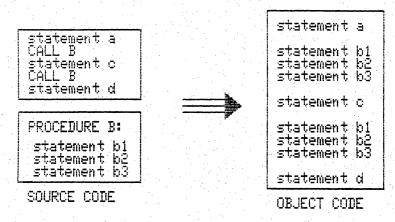

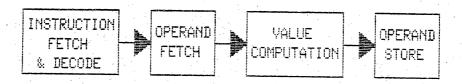

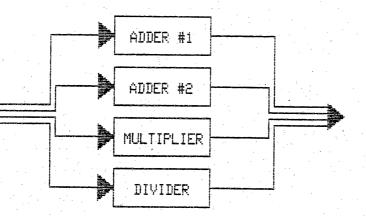

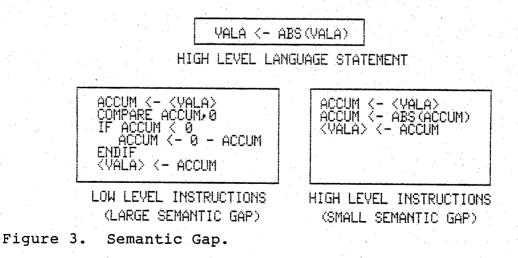

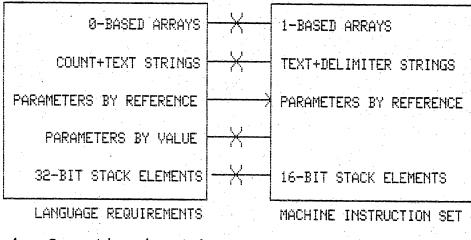

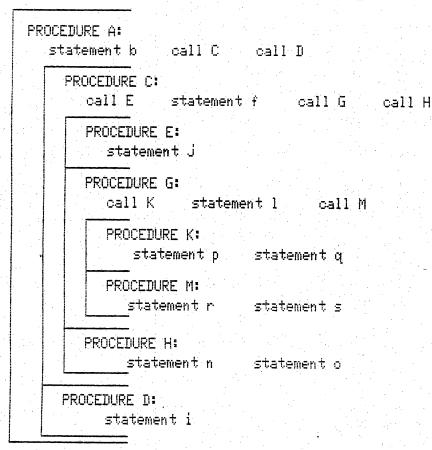

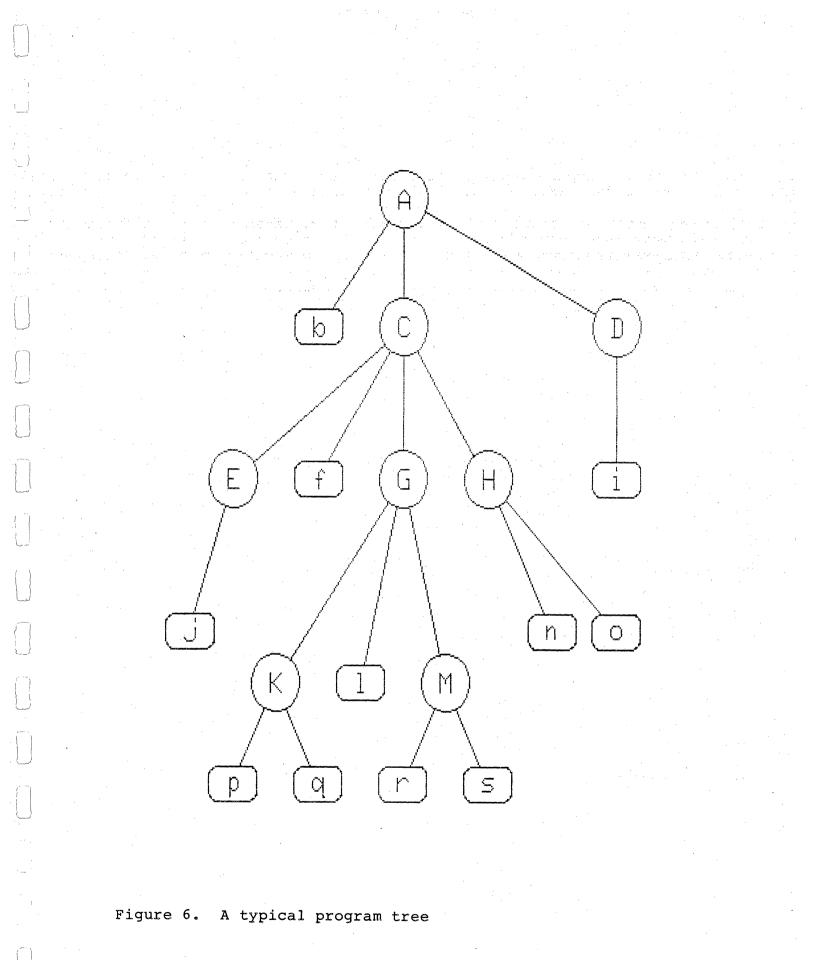

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8          | 15<br>16<br>17                            | 0 ·<br>0 ·        | 00                |                   |                       | 0 0 0                                   |        |             |