# CoRAM: An In-Fabric Memory Architecture for FPGA-Based Computing

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Eric S. Chung

B.S., Electrical Engineering and Computer Science University of California, Berkeley

Carnegie Mellon University Pittsburgh, PA

August, 2011

### **Abstract**

Field Programmable Gate Arrays (FPGA) have been used in many applications to achieve orders-of-magnitude improvement in absolute performance and energy efficiency relative to conventional microprocessors. Despite their newfound potency in both processing performance and energy efficiency, FPGAs have not gained widespread acceptance as mainstream computing devices. A fundamental obstacle to FPGA-based computing can be traced to the FPGA's lack of a common, scalable memory abstraction. When developing for FPGAs, application writers are often responsible for crafting the application-specific infrastructure logic that transports the data to and from the processing kernels, which are the ultimate producers and consumers within the fabric. Very often, this infrastructure logic not only increases design time and effort but will inflexibly lock a design to a particular FPGA product line, hindering scalability and portability. To create a common, scalable memory abstraction, this thesis proposes a new FPGA memory architecture called Connected RAM (CoRAM) to serve as a portable bridge between the distributed computation kernels and the edge memory interfaces. In addition to improving performance and efficiency, the CoRAM architecture provides a virtualized memory environment as seen by the hardware kernels to simplify application development and to improve an application's scalability and portability.

# **Acknowledgements**

I owe all of my success to my academic advisor, Professor James Hoe, who taught me how to think, speak, and write. It has been a tremendous privilege to work with James, who generously provided the resources and the comfortable environment that enabled me to pursue my ideas to fruition. I am sincerely grateful for his consistent encouragement, insight, and support throughout all these years.

I also thank Professor Ken Mai for his constant source of feedback throughout my time at CMU and for inviting me into his office when I had yet-another-circuit-question. I thank Professor Babak Falsafi for his intellectual contributions to my research projects, his genuine support for those all around him, and his encouragement and advice even all the way from Switzerland. I also thank my external committee members Professor Guy Blelloch, Professor Joel Emer, and Professor John Wawrzynek for serving on my defense. Their helpful comments and constructive criticisms significantly enhanced the quality of this thesis. I also wish to thank various members of the RAMP community for the friendships and the interactions that I have benefited from over so many years: Professor Derek Chiou, Hari Angepat, Nikhil Patil, Michael Pellauer, Professor Mark Oskin, and Andrew Putnam, and Professor Martha Mercaldi-Kim. I would also like to thank my mentors at Microsoft Research, Chuck Thacker and John Davis.

I would like to acknowledge the National Science Foundation (CCF-1012851), C2S2, CSSI, Sun Microsystems, Microsoft Research, and John and Claire Bertucci for providing the generous funding that supported my work at CMU. I would like to thank Bluespec and Xilinx for their tool donations.

There are many fellow graduate students and friends whom I wish to acknowledge. Jared Smolens, Brian Gold, and Jangwoo Kim were valuable mentors to me when I joined the TRUSS

project. Thanks to Jared for being a great friend, for his feedback, for maintaining our cluster, and for his ability to proofread anything I could throw at him. Brian always gave valuable opinions and was never too busy to answer my questions; thanks also to Brian and his wife Robin for making me feel welcome when I first arrived to CMU. Jangwoo was always supportive and providing helpful late-night discussions and advice on demand. Nikos Hardavellas was a sounding board for many ideas in the wee hours of the night. I hope Nikos will forgive me for the events of ISCA'05. Michael Papamichael provided the network-on-chip generator that helped to make this thesis possible. Thanks to Michael for being a constant source of feedback, for introducing me to the best Pad-See-Ew in all of existence, and for accompanying me on our adventure to New York's finest Brazilian BBQ. Peter Milder is a great friend, collaborator, and always found time to stop by and chat. Peter Klemperer was an entertaining officemate and friend who kept me up-to-date with his endless stories and projects. Yoongu Kim was my mutual commiserator and kept me company during the late work hours. I am grateful to Tom Wenisch, who frequently brought me out to half-priced margaritas at Mad Mex and gave me good advice on many subjects. I am also grateful to Mike Ferdman for his feedback on many of my research projects; thanks for Mike and Alisa Ferdman for also inviting me to their parties. Thanks to Gabriel Weisz, who endlessly tolerated my design bugs and also shared his homebrew with us. Thanks goes out to Eriko Nurvitadhi, who tolerated me as his roommate and officemate for nearly 7 years. In addition, I also greatly enjoyed the company and interactions with many other members of CMU and CALCM: Roland Wunderlich, Stephen Somogyi, Evaggelis Vlachos, Ippokratis Pandis, Vasileios Liaskovitis, Kai Yu, Wei Yu, Jennifer Black, Qian Yu, Professor Onur Mutlu, Chris Craik, Chris Fallin, Theodoros Strigkos, Marek Telgarsky, Bob Koutsoyannis, Kristen Dorsey, Ryan Johnson, and Brett Meyer.

I'd like to thank Elaine Lawrence, Reenie Kirby, Matt Koeske, and all the other assistants in our department for handling all the administrative duties that made things run smoothly for all the students. Susan Farrington always made me feel welcome and appreciated at CMU. The Isomac and Expobar machines deserve a special thanks for distilling the endless amounts of caffeine that transformed into this thesis.

I would like to thank Edward Lin and Fabian Manan who were great friends who kept my life interesting beyond the lab. Thank you to old friends who kept close from afar: Ben Liu, Patrick Charoenpong, Brandon Ooi, Mike Liao, Chethana Kulkarni, Kazim Zaidi, and Menzies Chen.

I am grateful to our cats, Cho Cho and Mi Mi, who kept us company all these years with an unlimited supply of entertainment, exasperation, and cat hair.

I cannot thank my parents enough for the sacrifices that they have made so that I could be here today. My family members, Alan, Lily, Melody, and Katie have been a pillar of support throughout my life and time at CMU.

Finally, I express my gratitude to Kari Cheng. As the significant other of an 'eternal' graduate student, Kari tolerated my habits, my unusual hours, and my times of absence with love, grace, and understanding. This journey would not have been complete without her.

# **Contents**

| Chapter | r 1: Introduction                                     | 2  |

|---------|-------------------------------------------------------|----|

| 1.1     | FPGAs for Computing                                   | 3  |

| 1.2     | Limitations of Conventional FPGAs                     | 3  |

| 1.3     | FPGAs Lack A Standard Memory Architecture             | 5  |

| 1.4     | The Connected RAM Memory Architecture                 | 6  |

| 1.5     | Thesis Contributions                                  | 7  |

| 1.6     | Thesis Outline                                        | 8  |

| Chapter | r 2: Background                                       | 9  |

| 2.1     | FPGA Anatomy                                          | 9  |

| 2.2     | Why Compute With FPGAs?                               | 12 |

| 2.3     | FPGA-Based Computing                                  | 14 |

|         | 2.3.1 The Convey HC-1                                 | 15 |

|         | 2.3.2 Nallatech Accelerator Module                    | 16 |

|         | 2.3.3 Berkeley Emulation Engine 3 (BEE3)              | 17 |

| 2.4     | The Need For A Standard Memory Architecture           | 17 |

| Chapter | r 3: CoRAM Architecture                               | 19 |

| 3.1     | CoRAM System Organization and Assumptions             | 19 |

| 3.2     | The CoRAM Program Model                               | 21 |

|         | 3.2.1 Software Control Threads                        | 21 |

|         | 3.2.2 How Does CoRAM Solve The Portability Challenge? | 25 |

|         | 3.2.3 CoRAM Microarchitecture                         | 25 |

| 3.3    | CoRAM versus Alternative Approaches           | 27 |

|--------|-----------------------------------------------|----|

| 3.4    | Communication and Synchronization             | 31 |

| 3.5    | Other Issues                                  | 32 |

| 3.6    | Summary                                       | 34 |

| Chapte | r 4: Cor-C Architecture and Compiler          | 35 |

| 4.1    | CoR-C Overview                                | 36 |

|        | 4.1.1 Control Threads                         | 36 |

|        | 4.1.2 Object Instantiation and Identification | 38 |

|        | 4.1.3 Memory Control Actions                  | 40 |

| 4.2    | Disallowed Behaviors                          | 44 |

| 4.3    | Simple Example: Vector Addition               | 45 |

| 4.4    | The CoRAM Control Compiler (CORCC)            | 48 |

| 4.5    | Summary                                       | 52 |

| Chapte | r 5: Cor-C Examples                           | 53 |

| 5.1    | Matrix-Matrix Multiplication                  | 53 |

|        | 5.1.1 Background                              | 54 |

|        | 5.1.2 Related Work                            | 56 |

|        | 5.1.3 Parallelization on the FPGA             | 57 |

|        | 5.1.4 Manual Implementation                   | 59 |

|        | 5.1.5 Cor-C Implementation                    | 60 |

|        | 5.1.6 Discussion                              | 63 |

| 5.2    | Black-Scholes                                 | 64 |

|        | 5.2.1 Background                              | 64 |

|        | 5.2.2 Parallelization on the FPGA             | 65 |

|        | 5.2.3 Memory Streaming                        | 66 |

|        | 5.2.4 Discussion                              | 70 |

| 5.3    | Sparse Matrix-Vector Multiplication           | 72 |

|        | 5.3.1 Background                              | 72 |

|        | 5.3.2. Related Work                           | 73 |

|        | 5.3.3    | Parallelization on the FPGA                         | 74         |

|--------|----------|-----------------------------------------------------|------------|

|        | 5.3.4    | Discussion                                          | 78         |

| 5.4    | Summa    | ary                                                 | 78         |

| Chapte | r 6: Col | RAM Memory System                                   | <b>7</b> 9 |

| 6.1    | Devisir  | ng a Memory System for CoRAM                        | 79         |

| 6.2    | CoRAN    | M Memory System: Hard or Soft?                      | 82         |

| 6.3    | Unders   | standing the Cost of Soft CoRAM                     | 83         |

| 6.4    | Implen   | nenting A Cluster-Style Microarchitecture for CoRAM | 87         |

|        | 6.4.1    | Design Overview                                     | 89         |

|        | 6.4.2    | Clients and Interfaces                              | 90         |

|        | 6.4.3    | Message Sequencing and Out-of-Order Delivery        | 92         |

|        | 6.4.4    | Memory-to-CoRAM Datapath                            | 94         |

|        | 6.4.5    | Cluster Summary                                     | 100        |

| 6.5    | Networ   | rk-on-Chip                                          | 101        |

| 6.6    | Memor    | ry Controllers and Caches                           | 104        |

| 6.7    | Networ   | rk-to-DRAM-Cache Interface                          | 105        |

| 6.8    | Summa    | ary                                                 | 106        |

| Chapte | r 7: Pro | ototype                                             | 108        |

| 7.1    | Cluster  | Design                                              | 109        |

| 7.2    | CONE     | CT Network-on-Chip Generator                        | 110        |

| 7.3    | Edge M   | Memory Cache Controllers                            | 111        |

| 7.4    | Corflov  | W                                                   | 111        |

|        | 7.4.1    | Command Line Parameters and Options                 | 112        |

| 7.5    | Xilinx   | ML605 Board                                         | 115        |

|        | 7.5.1    | Tool Release and Future Plans                       | 116        |

| Chapte | r 8: Eva | aluation                                            | 117        |

| 8.1    | Experi   | mental Setup                                        | 118        |

| 82     | Microb   | anchmark Characterization                           | 110        |

|         | 8.2.1     | Latency Characterization                             | 120 |

|---------|-----------|------------------------------------------------------|-----|

|         | 8.2.2     | Bandwidth Characterization                           | 122 |

|         | 8.2.3     | Summary                                              | 123 |

| 8.3     | Synthes   | sis Characterization                                 | 124 |

|         | 8.3.1     | Comparing Area and Power Between Hard vs. Soft CoRAM | 126 |

| 8.4     | Applica   | ation Evaluation                                     | 128 |

|         | 8.4.1     | Matrix-Matrix Multiplication                         | 129 |

|         | 8.4.2     | Black-Scholes                                        | 132 |

|         | 8.4.3     | Sparse Matrix-Vector Multiplication                  | 135 |

| 8.5     | Summa     | ry                                                   | 140 |

| Chapter | 9: Rel    | ated Work                                            | 143 |

| 9.1     | Special   | ized Reconfigurable Devices                          | 143 |

| 9.2     | Reconfi   | gurable Memory Architectures                         | 143 |

| 9.3     | High Le   | evel Synthesis                                       | 144 |

| 9.4     | Archite   | ctures and Program Models                            | 145 |

| Chapter | · 10: Cor | nclusions                                            | 146 |

| 10.1    | Future '  | Work                                                 | 147 |

| Chapter | A: Inte   | erfaces and Libraries                                | 149 |

| A.1     | Bluespe   | ec                                                   | 149 |

| A.2     | Cor-C I   | nclude Header                                        | 150 |

| Chapter | ·B: Cac   | che Memory Personality                               | 152 |

| B.1     | Bluespe   | ec                                                   | 152 |

| B.2     | Control   | Thread Program                                       | 155 |

| Chapter | · C: FIF  | O Memory Personality                                 | 157 |

| C.1     | Bluespe   | ec                                                   | 157 |

| C.2     | Control   | Thread Program                                       | 158 |

| Chapter | D: Matrix-Matrix Multiplication        | 160 |

|---------|----------------------------------------|-----|

| D.1     | Bluespec                               | 160 |

| D.2     | Control thread program                 | 164 |

| Chapter | E: Sparse Matrix-Vector Multiplication | 166 |

| E.1     | Bluespec                               | 166 |

| E.2     | Control thread program                 | 168 |

# **List of Tables**

| Table 1:  | Comparison Between FPGAs, GPGPUs, CPUs, and Custom Logic                     | 14  |

|-----------|------------------------------------------------------------------------------|-----|

| Table 2:  | Cor-C Data Types                                                             | 36  |

| Table 3:  | Cor-C Accessor Control Actions (Static)                                      | 37  |

| Table 4:  | Memory Control Actions (Dynamic)                                             | 41  |

| Table 5:  | Channel Control Actions (Dynamic)                                            | 41  |

| Table 6:  | Single-Precision PE Characteristics                                          | 59  |

| Table 7:  | Black-Scholes Processing Characteristics                                     | 66  |

| Table 8:  | Single-Precision Sparse Matrix-Vector Multiplication Kernel Characteristics. | 74  |

| Table 9:  | Summary of Key Relations in Cluster-Style Microarchitecture                  | 88  |

| Table 10: | Estimated MUX Costs Across Projected FPGA Configurations                     | 88  |

| Table 11: | Transaction Interface                                                        | 92  |

| Table 12: | Summary of Key Structures in a Single Cluster                                | 100 |

| Table 13: | Parameters of Cluster-Memory Interconnection Network (Large)                 | 102 |

| Table 14: | Customizable Parameters in a Single Cluster Implemented in Bluespec          | 109 |

| Table 15: | Specification File in Corflow                                                | 114 |

| Table 16: | Corflow Design Statistics                                                    | 116 |

| Table 17: | Configuration Used in Single Cluster Characterization                        | 121 |

| Table 18: | Timeline of Single Unloaded Access to Memory                                 | 122 |

| Table 19: | Area and Power Characteristics of Single Cluster and Mesh Router             | 125 |

| Table 20: | Control Thread Synthesis Results                                             | 126 |

| Table 21: | FPGA System Parameters with CoRAM Support                                    | 127 |

| Table 22: | Mapping MMM and SpMV to Various FPGA Configurations                          | 128 |

| Table 23: | Matrices Used in Sparse Matrix-Vector Multiplication Experiments | 136 |

|-----------|------------------------------------------------------------------|-----|

| Table 24: | Summary of Area-Normalized Performances Across Workloads         | 140 |

# **List of Figures**

| Figure 1:  | Application Writer's View of a Conventional FPGA                 | 4  |

|------------|------------------------------------------------------------------|----|

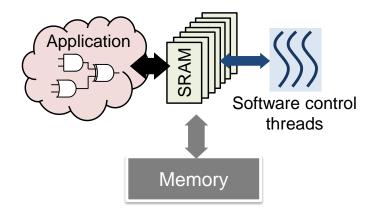

| Figure 2:  | User's View of an FPGA with CoRAM Support                        | 6  |

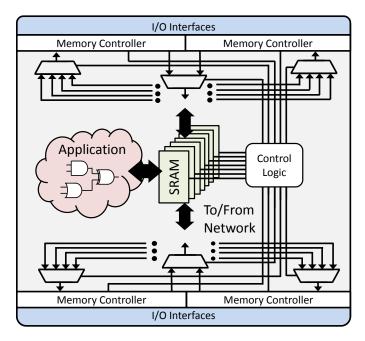

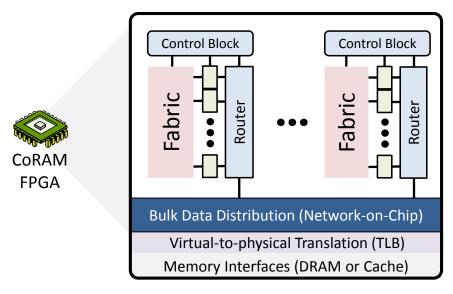

| Figure 3:  | CoRAM: Physical Implementation                                   | 7  |

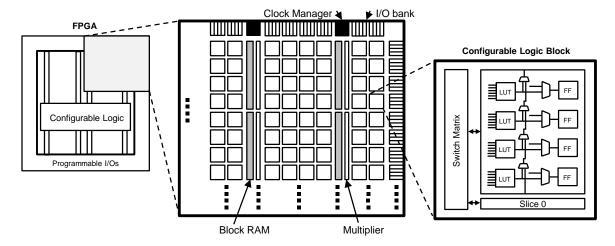

| Figure 4:  | Conventional FPGA Fabric with Configurable Logic Blocks          | 10 |

| Figure 5:  | Conventional Block RAM Interface                                 | 10 |

| Figure 6:  | Xilinx FPGA Technology Trends                                    | 12 |

| Figure 7:  | ITRS 2009 Scaling Projections                                    | 13 |

| Figure 8:  | The Convey HC-1 Architecture                                     | 15 |

| Figure 9:  | The Nallatech Xeon Accelerator Module                            | 16 |

| Figure 10: | The BEE3 Platform                                                | 17 |

| Figure 11: | Assumed System Context                                           | 20 |

| Figure 12: | CoRAM Memory Architecture                                        | 20 |

| Figure 13: | Example Usage of CoRAM                                           | 23 |

| Figure 14: | Memory Control Action.                                           | 24 |

| Figure 15: | Beneath the CoRAM Programming Abstraction                        | 26 |

| Figure 16: | CoRAM as a Software-Managed Memory Hierarchy.                    | 34 |

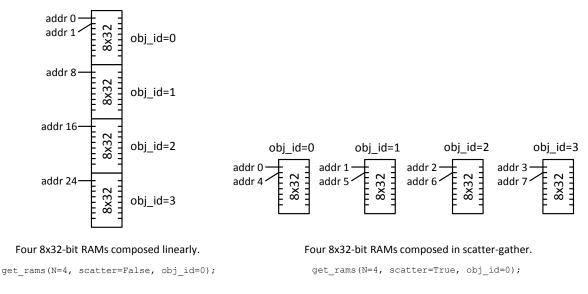

| Figure 17: | Linear and Scatter-Gather RAM Compositions                       | 40 |

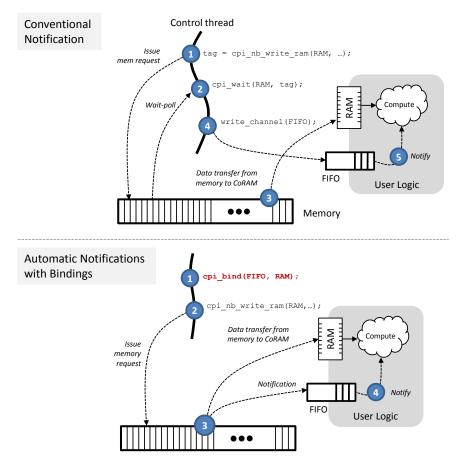

| Figure 18: | Supporting Automatic Notification with Channel-to-CoRAM Bindings | 42 |

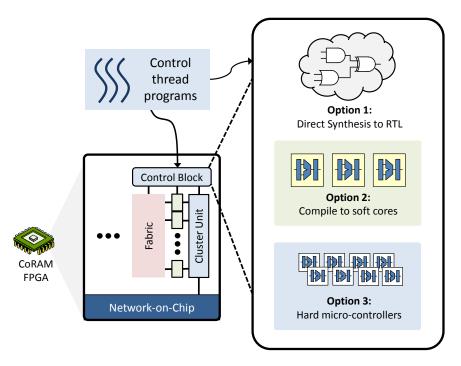

| Figure 19: | Options for Synthesizing Control Threads                         | 48 |

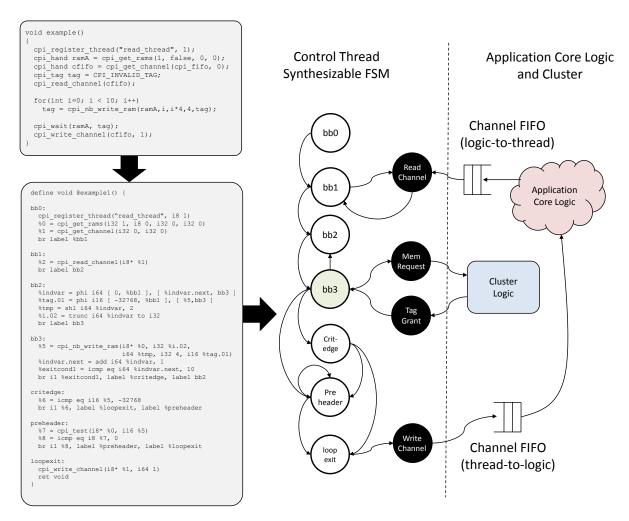

| Figure 20: | CORCC Example                                                    | 49 |

| Figure 21: | Matrix-Matrix Multiplication Processing Element                  | 56 |

| Figure 22: | Work Distribution in Matrix-Matrix Multiplication.               | 57 |

| Figure 23: | Computation Phase of Matrix-Matrix Multiplication                 | 58  |

|------------|-------------------------------------------------------------------|-----|

| Figure 24: | Matrix-Matrix Multiplication with Double Buffering.               | 60  |

| Figure 25: | Matrix-Matrix Multiplication Control Thread (Non-double-buffered) | 60  |

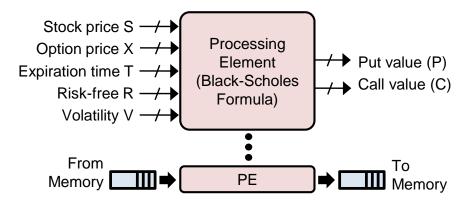

| Figure 26: | Black-Scholes Processing Element                                  | 66  |

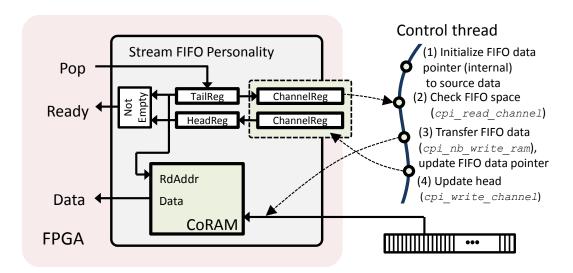

| Figure 27: | Stream FIFO Memory Personality.                                   | 67  |

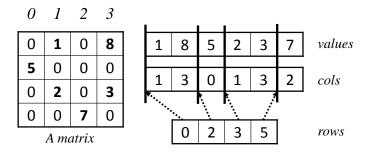

| Figure 28: | Example of Compressed Sparse Row Format in SpMV                   | 72  |

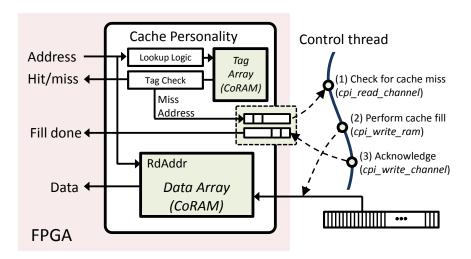

| Figure 29: | Cache Memory Personality                                          | 76  |

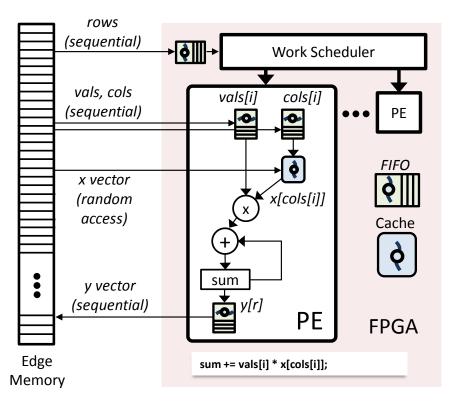

| Figure 30: | Implementation of SpMV with CoRAM                                 | 77  |

| Figure 31: | Beneath the CoRAM Architecture                                    | 80  |

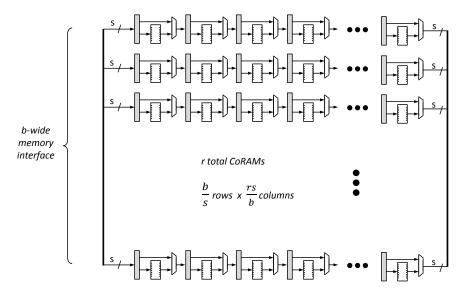

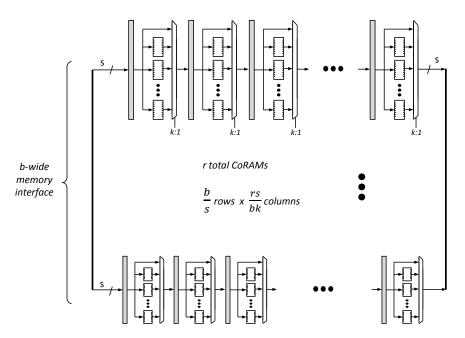

| Figure 32: | Shift Register Network for CoRAM                                  | 84  |

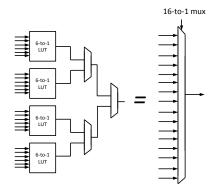

| Figure 33: | Efficient 16-to-1 multiplexer using 6-input LUTs                  | 84  |

| Figure 34: | Shift Register Network (Combined) for CoRAM                       | 85  |

| Figure 35: | Multiple Memory Interfaces                                        | 86  |

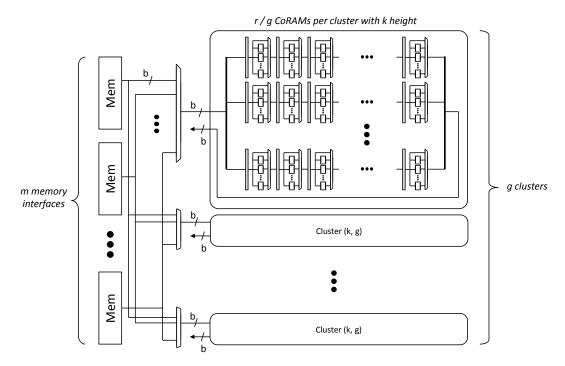

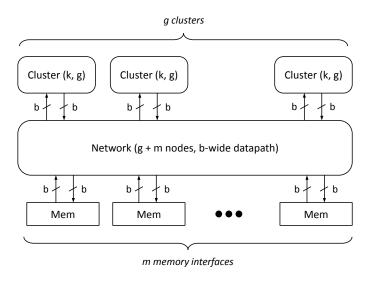

| Figure 36: | Cluster-Style Microarchitecture                                   | 87  |

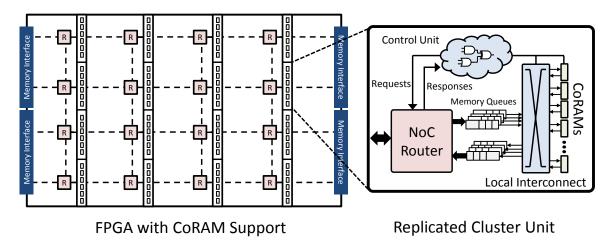

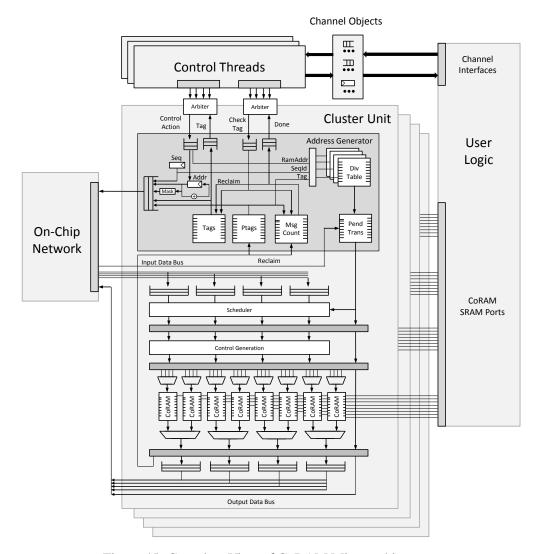

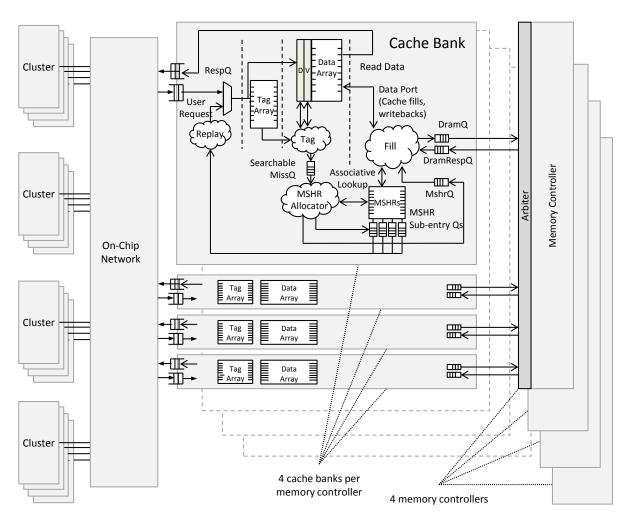

| Figure 37: | Cluster-Style Microarchitecture for CoRAM                         | 89  |

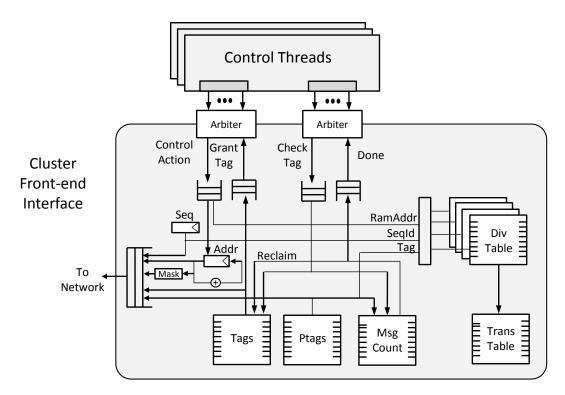

| Figure 38: | Cluster Front-End Interface                                       | 90  |

| Figure 39: | Mapping Functions to Support Arbitrary CoRAM Aspect Ratios        | 94  |

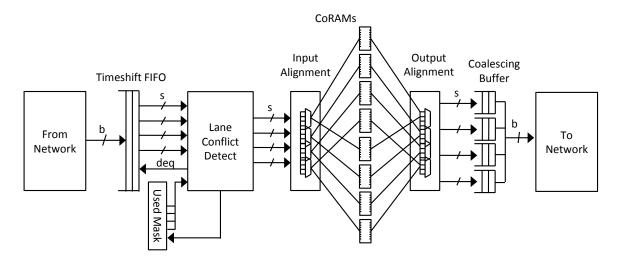

| Figure 40: | Memory-to-CoRAM Datapath                                          | 95  |

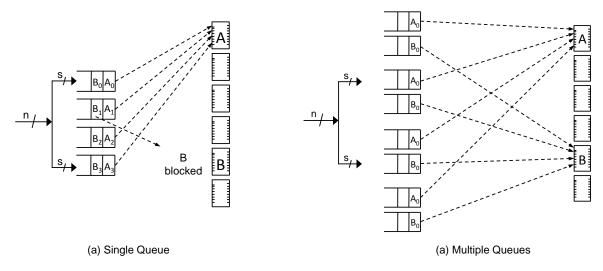

| Figure 41: | Single and Multi Memory-to-CoRAM Queues                           | 96  |

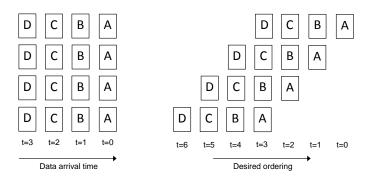

| Figure 42: | Time-shifted Schedule                                             | 96  |

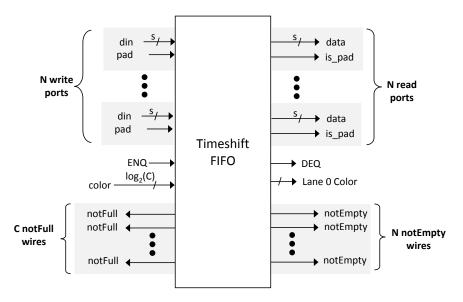

| Figure 43: | Front and Back Interfaces of Timeshift FIFO                       | 97  |

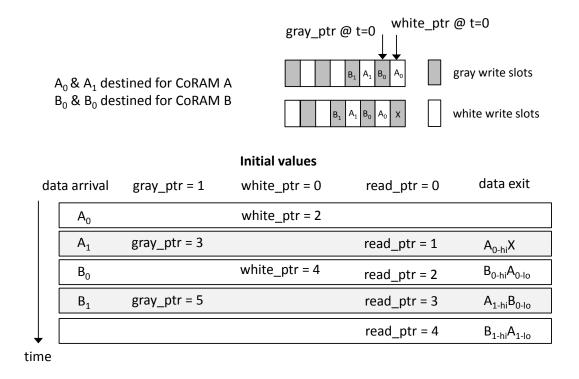

| Figure 44: | Example Timeline of Timeshift FIFO                                | 98  |

| Figure 45: | Complete View of CoRAM Microarchitecture                          | 99  |

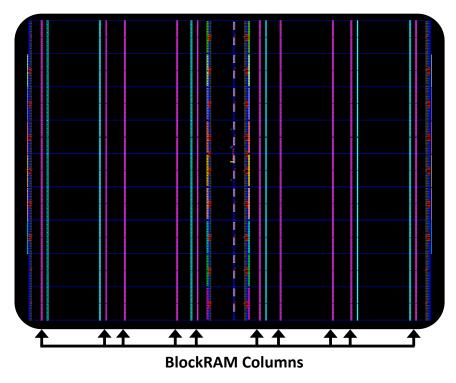

| Figure 46: | Virtex-6 LX760 Layout Schematic                                   | 103 |

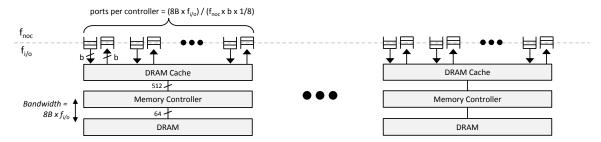

| Figure 47: | NoC-to-DRAM Interface                                             | 106 |

| Figure 48: | Memory Subsystem                                                  | 107 |

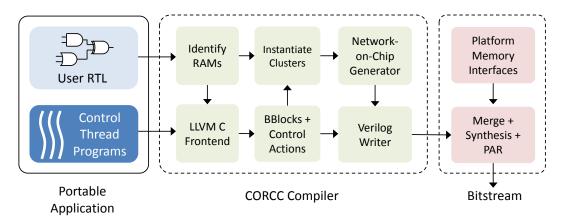

| Figure 49: | Corflow Method of Compilation                                     | 112 |

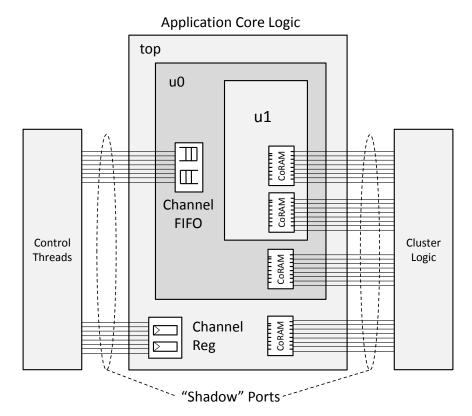

| Figure 50: | Creating Shadow Ports                                             | 113 |

| Figure 51: | ML605 Prototype                                                   | 115 |

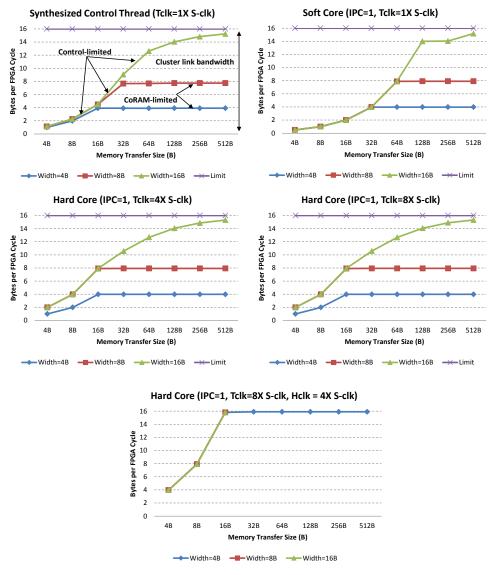

| Figure 52: | Single Cluster Throughput Characteristics                         | 120 |

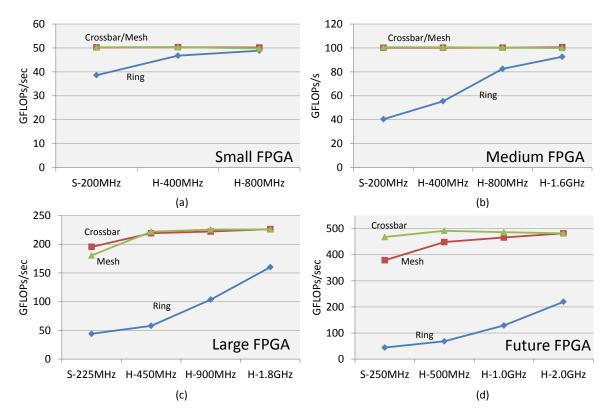

| Figure 53: | MMM Performance Trends                                                | 129 |

|------------|-----------------------------------------------------------------------|-----|

| Figure 54: | GEMM Area and Efficiency Trends                                       | 130 |

| Figure 55: | Black-Scholes Performance Across Network Topologies (small FPGA)      | 132 |

| Figure 56: | Black-Scholes Bandwidth Usage Across Network Topologies (small FPGA). | 133 |

| Figure 57: | Black-Scholes Performance Trends                                      | 134 |

| Figure 58: | Black-Scholes Area and Efficiency Trends                              | 135 |

| Figure 59: | SpMV Performance Trends                                               | 137 |

| Figure 60: | SpMV Per-Input Performance Trends                                     | 138 |

| Figure 61: | SpMV Area and Efficiency Trends                                       | 139 |

| Figure 62: | Detailed Comparison Between Good and Bad Inputs on SpMV               | 142 |

## **Chapter 1**

### Introduction

And now for something completely different.

Monty Python

Over the past several decades, the defining characteristic of general-purpose processors has been their programmability and flexibility. With steady improvements in VLSI technology, general-purpose processors have attained tremendous levels of success and adoption. In recent years, the deviation from classical scaling law [37] has begun to threaten the sustained scalability of future multicores built solely out of general-purpose cores [23]. Although transistor dimensions continue to shrink with each major technology node, transistor threshold and supply voltages have not been scaling as commensurately due to leakage effects. The inability to scale the supply voltage has now constrained us to an era where power—not area—is becoming the ultimate limiting resource. With the recent emphasis on power efficiency coupled with the ever-increasing appetite for high computational throughput, designers must think beyond classical von Neumann architectures that fundamentally sacrifice efficiency for their generality.

In the quest for energy-efficient computing, Field Programmable Gate Arrays (FPGAs) have emerged as a class of general-purpose accelerators with high potential to address the demand for high performance and efficiency. FPGAs comprise a sea of programmable logic gates that can be reconfigured on-demand to accelerate a particular problem or task. Despite their proven advantages, today's commercial FPGAs are not built in mind for computing and have mostly eluded mainstream adoption in general-purpose computing. A fundamental limitation of the FPGA is its lack of a stan-

dard memory architecture. Beyond having to developing the core logic, FPGA application writers are burdened by a low-level fabric abstraction that exposes complex details specific to particular devices and platforms. Applications often lack portability, and substantial effort must be invested to develop and/or optimize the cloud of infrastructure that surrounds the core logic of the application.

To address these challenges, the contribution of this thesis is a major reconception of the architectural paradigm of FPGA-based computing. The thesis presents a top-to-bottom exploration of a new, all-purpose memory architecture called Connected RAM (CoRAM), which simplifies difficult aspects of FPGA programming and memory management while enhancing the programmability and portability of applications.

### 1.1 FPGAs for Computing

The merits of FPGA-based reconfigurable computing have been known since the early 1990s [35]. FPGAs consist of up to millions of tiny, programmable lookup tables that can be configured "in the field" to implement arbitrary logic functions. Unlike the sequential-style programming languages of general-purpose processors, FPGA "programs" are typically captured with hardware description languages that expose a highly concurrent abstraction to the user. FPGAs have been demonstrated in many cases to accelerate a wide variety of applications ranging from financial analytics, bioinformatics, physics, and databases [98, 118, 87, 53]. FPGAs typically achieve their feats through massive, fine-grained parallelism and the pipelining of arbitrary dataflows.

### 1.2 Limitations of Conventional FPGAs

While accumulated VLSI advances have steadily improved the FPGA fabric's processing capability, FPGAs have yet to gain widespread acceptance as mainstream computing devices. A commonly cited obstacle is the difficulty in programming FPGAs using low-level hardware description languages and development flows. A further problem lies in the fact that FPGAs today are not architected for computing purposes but rather to emulate or replace ASICs.

While the former concern is being gradually addressed by advances in high-level synthesis [45, 17], a more fundamental problem lies in the FPGA's lack of a stable and standard "architecture" for

Figure 1: Application Writer's View of a Conventional FPGA.

application writers. Unlike their general-purpose counterparts, conventional FPGAs expose nothing to the user but a "sea" of logic and a collection of external I/O pins. A general-purpose processor by contrast exports its computational and memory resources through a generic and structured interface (i.e., Instruction Set Architecture) that abstracts away the machine's underlying details.

When developing for the FPGA, a designer often has to create from bare fabric not only the target application kernel itself but also the application-specific infrastructure logic, which requires detailed knowledge of the specific device and platform being utilized. This infrastructure often includes user-developed mechanisms to support and optimize the transfer of data to and from external DRAM interfaces and to I/O devices (see Figure 1). Very often, creating or using this infrastructure logic not only increases design time and effort but will frequently lock a design to a particular FPGA platform or device, hindering scalability and portability. Further, the support mechanisms which users are directly responsible for will be increasingly difficult to manage in the future as: (1) the number of on-die SRAMs and off-chip DRAM interfaces increase in number and become more distributed across the fabric, and (2) long-distance interconnect delays become more difficult to tolerate in larger fabric designs, requiring more spatial awareness by the user to distribute memory data effectively.

### 1.3 FPGAs Lack A Standard Memory Architecture

The root of the aforementioned challenges can be traced to the fact that current FPGAs lack essential abstractions and built-in mechanisms that one comes to expect in a general purpose computer—i.e., an Instruction Set Architecture (ISA) that defines a standard agreement between hardware and software. From a computing perspective, a standard and stable architectural definition is a critical ingredient for programmability and for application portability.

A crucial starting point for addressing this challenge is to rethink how the notion of "memory" should be presented and architected within an FPGA. In many cases, the lack of application portability stems from unenforced separation between the application kernel itself and the mechanisms needed to obtain its data from the environment (i.e., main memory and I/O). To specifically address the challenges related to memory on FPGAs, the central goal of this thesis is to create a shared, scalable, and portable memory architecture suitable for future FPGA-based computing devices. Such a memory architecture would be used in a way that is analogous to how general purpose programs universally access main memory through standard "loads" and "stores" as defined by an ISA—without any knowledge of hierarchy details such as caches, memory controllers, etc. At the same time, the FPGA memory architecture definition cannot simply adopt what exists for general purpose processors and instead should reflect the spatially distributed nature of today's FPGAs—consisting of up to millions of interconnected LUTs and thousands of embedded SRAMs [116].

Working under the above premises, the guiding principles for the desired FPGA memory architecture are:

- The architecture should present to the user a common, virtualized appearance of the FPGA

fabric, which encompasses reconfigurable logic, its external memory interfaces, and the multitude of SRAMs—while freeing designers from details irrelevant to the application itself.

- The architecture should provide a standard, easy-to-use mechanism for controlling the transport of data between memory interfaces and the SRAMs used by the application throughout the course of computation.

- Applications for the architecture should port effortlessly to newer devices and platforms without modification.

Figure 2: User's View of an FPGA with CoRAM Support.

• The architecture should be amenable to scalable implementations on the FPGA without affecting the architectural view presented to existing applications.

### 1.4 The Connected RAM Memory Architecture

To satisfy the above goals, this thesis proposes the Connected RAM (CoRAM) memory architecture for future FPGAs designed for general-purpose computing. The CoRAM architecture allows the application writer to focus on creating efficient, high-performance kernels within a virtualized FPGA environment while relying on a standard set of abstracted and distributed memory mechanisms to sustain the kernel's data consumption and production. As shown in Figure 2, an FPGA with CoRAM support presents a highly simplified view of the fabric to the user, consisting of programmable logic, on-die SRAMs, and a standard software abstraction for mediating accesses to main memory.

To facilitate portability, application logic is never permitted to directly access the edge memory interfaces nor the I/O pins that are typical in modern FPGAs. A unique characteristic of the CoRAM architecture is that the SRAMs themselves are used as portals into global memory and are programmed using a stylized, high-level language over the course of a computation. The use of a portable language to specify the memory requirements of a given application effectively "virtualizes" a kernel and would make it possible to easily relocate a kernel within a fabric or to port an application between different FPGA families with a common CoRAM architecture. The CoRAM abstraction itself is also naturally distributed to suit the nature of FPGA-like fabrics and can be used

Figure 3: CoRAM: Physical Implementation.

to form convenient memory structures with higher-level semantics without the loss of portability or efficiency.

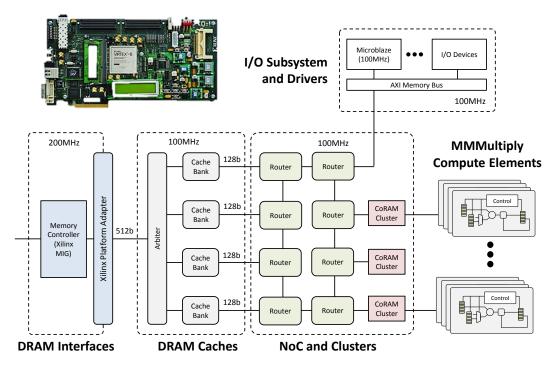

Beneath the CoRAM abstraction lies a high-performance microarchitecture designed to scale up to hundreds to thousands of "connected" CoRAMs. Figure 3 illustrates an island-style microarchitecture devised in this thesis that distributes control threads and core logic components across replicated clusters of aggregated CoRAMs and control blocks. In between the clusters, a high-performance network-on-chip provides global connectivity between the end-points and the off-chip memory interfaces. An important property of the microarchitecture shown in Figure 3 is the speedup provided by hardening of the network-on-chip and the clustering logic. The over-provisioning of bandwidth and latency of general-purpose mechanisms has the notable benefit of allowing applications to achieve near-ideal performance potential and efficiency with modest overheads in die area and power, which will be demonstrated in Chapter 8.

### 1.5 Thesis Contributions

The scope of this thesis encompasses two major research thrusts: (1) defining a proper memory abstraction both useful to a wide range of FPGA applications, and (2) the investigation of the underlying hard and soft mechanisms needed to support the abstraction effectively. The contributions of this thesis are:

- Identification and rationale for essential abstractions in the CoRAM architecture.

- The demonstrated effectiveness of CoRAM in comparison to conventional approaches.

- An exploration of the microarchitectural design space for CoRAM on conventional and future FPGAs.

- Prototype RTL designs that demonstrate the feasibility of CoRAM.

- A study of the performance and efficiency gap between CoRAM and conventional development approaches.

- An investigation on determining which mechanisms are needed in future FPGAs to support the CoRAM architecture effectively.

### 1.6 Thesis Outline

The remainder of this thesis is organized as follows. Chapter 2 gives background on FPGAs and their applications in computing. Chapter 3 introduces the CoRAM architectural paradigm. Chapter 4 describes the Cor-C Architecture Specification, which is a devised instance of the CoRAM paradigm. Chapter 5 describes several case studies using Cor-C. Chapter 6 gives a detailed treatment of the CoRAM microarchitecture. Chapter 7 describes the prototype implementation of CoRAM. Chapter 8 gives an evaluation of the CoRAM microarchitecture. Chapter 9 discusses related work. Chapter 10 offers conclusions and directions for future work.

### Chapter 2

# **Background**

Traditionally, FPGAs have been the bastard step-brother of ASICs.

André Dehon, FPGA 2004

This chapter presents background material on FPGAs and their technological trends over the past decade. Section 2.1 covers the basic anatomy of the FPGA, beginning from fabric architecture down to the embedded memories in today's commercial devices. Section 2.2 explains the merits of FPGAs for computing. Section 2.3 discusses state-of-the-art FPGA-based computing systems. Section 2.4 concludes with implications and guiding design principles for the CoRAM memory architecture.

### 2.1 FPGA Anatomy

Field Programmable Gate Arrays (FPGA) are silicon devices that allow "in-the-field" reconfiguration of programmable logic after manufacture. Modern FPGAs consist of up to millions of small, programmable lookup tables (LUTs) and interconnect wires that can be configured at the bit-and wire-level to implement arbitrary logic functions [74]. Figure 4 illustrates the basic anatomy of FPGA "soft fabric", which comprises a sea of regularly tiled configurable logic blocks (CLBs) surrounded by programmable routing [112]. Typically, each CLB contains one or more lookup tables (LUTs), which are small n-deep SRAMs that can be "configured" with specific values to implement a desired  $2^n$ -to-1 truth table. CLBs additionally include hardwired elements such as flip-flops

Figure 4: Conventional FPGA Fabric with Configurable Logic Blocks [114].

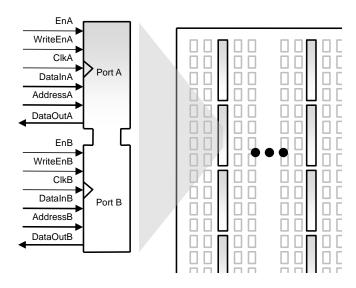

Figure 5: Conventional Block RAM Interface.

to form sequential logic and buffering. In between the CLBs shown in Figure 4, a sea of programmable interconnect allows neighboring logic to communicate and thus form the composition of multiple gates. The architecture of soft logic is typically characterized by a bevy of parameters, including the granularity of the CLB, the LUT size, the input and output connectivity to the CLB, the switch block flexibility, the number of routing tracks per channel, etc. [26]<sup>1</sup>.

Reconfigurable logic alone typically does not suffice for many FPGA-based applications. Modern commercial FPGAs usually embed up to several megabytes of on-chip memory in the form of

<sup>&</sup>lt;sup>1</sup>Soft logic architecture will not be a major focus of this work. The Xilinx Virtex-6 FPGA architecture will largely serve as a baseline fabric for this thesis.

many small embedded SRAMs distributed throughout the reconfigurable fabric (e.g., Xilinx uses 18Kbit SRAMs called BlockRAMs or BRAMs [115]). These embedded memories provide a basic wire-level SRAM interface for reading and writing by gate-level reconfigurable logic (see Figure 5) and can typically operate up to 500MHz [115]. Unlike conventional SRAMs, the memories can be efficiently configured with varying aspect ratios (e.g., 16384x1 or 4096x32) or combined to emulate larger blocks of memory. The architecture of the FPGA itself usually includes hard mechanisms that avoid the use of LUT resources up to a certain composition size of multiple SRAMs [122].

The large number of distributed SRAMs plays an essential role in providing FPGA-based applications with tremendous on-chip memory bandwidth (up to terabytes per second) in order to sustain the high rate of consumption that fabric-based applications require. SRAMs are typically populated prior to configuration of the FPGA by embedding the required data within the FPGA bitstream itself. Another alternative, although costly in terms of SRAM port and LUT usage, is to dynamically populate the SRAMs with data from off-chip interfaces during the runtime of an application.

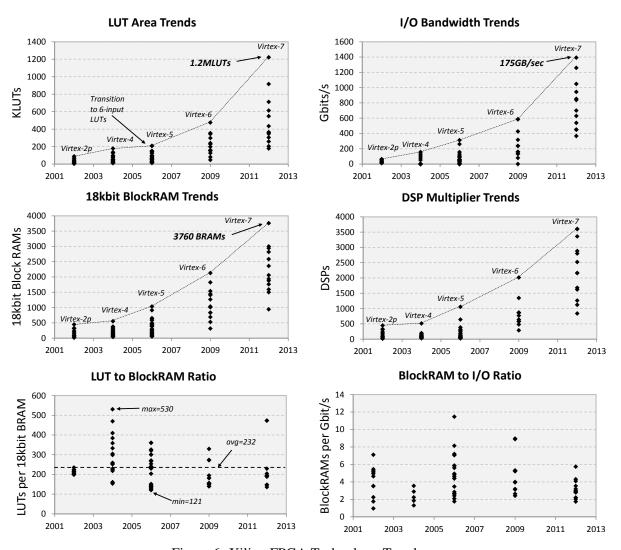

FPGA Technological Trends. The technological trends of FPGAs have closely mirrored the trajectory of Moore's Law since their inception. Figure 6 plots the characteristics of all Xilinx FPGA devices since 2002. As shown, FPGAs have continued to double in LUT area density every 18 to 24 months—progressing from tens of thousands of LUTs up to millions on a single device<sup>2</sup>. To visualize this level of scale, one million LUTs would be sufficient to synthesize over 800 minimally-configured soft microblaze processors in a single device [3]. The scaling of fabric is also accompanied by a commensurate increase in the number of SRAMs and multipliers as can be seen in Figure 6. The largest FPGAs today provide enough on-chip memory (tens of megabytes) to rival the capacity that of the last-level caches in today's state-of-the-art multicores. The scaling of FPGA fabric has also been accompanied by an unprecedented increase in external I/O bandwidth. Xilinx, for example, now manufactures FPGAs with high-speed transceivers up to 20Gbps per pin [116]. From a memory bandwidth perspective, high-end FPGAs would be able to provide up to 175GB/sec of off-chip memory bandwidth by the year 2012.

<sup>&</sup>lt;sup>2</sup>Note that the slight anomaly in the LUT area increase from 2004 to 2007 occurred when Xilinx transitioned from a 4-input LUT architecture to a larger 6-input LUT.

Figure 6: Xilinx FPGA Technology Trends.

### 2.2 Why Compute With FPGAs?

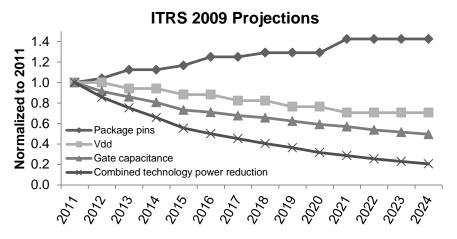

Since 2005, processor designers have shifted their focus towards increasing core counts to achieve performance commensurate with Moore's Law. Moore's Law, which has been a fundamental driver for technological innovations in the industry, projects that the number of components in a single device will double every 18 to 24 months. The recent departure from classical scaling laws [37] has placed Moore's Law in jeopardy, and thus the expected scalability of future multicore systems. Figure 7 shows the long-term expected trends in pin count, Vdd, and gate capacitance according to the ITRS 2009 roadmap [57]. Although transistor densities are projected to double with each major technology node, supply voltages are only expected to decrease by a very small amount

Figure 7: ITRS 2009 Scaling Projections (High-performance MPUs and ASICs [57]).

due to leakage concerns. With the inability to reduce the threshold voltage, supply voltages must also be held high enough to maintain sufficient overdrive. Assuming that clock frequencies do not increase substantially, the reduction in power per transistor is expected to drop only by a factor of 5X over the next fifteen years (in contrast to the doubling of transistor density with each additional technology node).

Unconventional Architectures. The use of "unconventional" computing architectures such as FP-GAs, GPGPUs, or even ASICs today offers a promising path in the quest for energy-efficient computing. For computing applications, the customizable and fine-grained nature of FPGAs enables them to achieve significant improvements in absolute performance and energy efficiency relative to conventional microprocessors (e.g., [43, 23, 21, 96, 63]). For example, FPGAs have been recently used to accelerate a wide range of non-traditional applications, ranging from quantitative finance [98], databases [53], bioinformatics [118], speech recognition [71], etc.

In a recent study from [23], Table 1 gives a comparison of physically-measured performance and energy efficiency between state-of-the-art multicores, GPUs, FPGAs, and Custom Logic for single-precision Black-Scholes, Matrix Multiplication and Fast Fourier Transform. As shown, the FPGA architecture offers competitive performance and energy efficiency gains over other computing devices, even relative to GPGPUs with dedicated floating point units. The recent spate of evidence supporting FPGAs, GPGPUs, and ASICs suggests that future multicore devices will transition into becoming heterogeneous, where general-purpose cores will be combined with specialized

Table 1: Comparison Between FPGAs, GPGPUs, CPUs, and Custom Logic.

|                                 |                    | GFLOP/s    | $(GFLOP/s)/mm^2$ (40nm)      | GFLOP/J (40nm) |

|---------------------------------|--------------------|------------|------------------------------|----------------|

|                                 | Intel Core i7-960  | 96         | 0.50                         | 1.14           |

|                                 | Nvidia GTX285      | 425        | 2.40                         | 6.78           |

| M-4-i                           | Nvidia GTX480      | 541        | 1.28                         | 3.52           |

| Matrix-matrix multiplication    | ATI R5870          | 1491       | 5.95                         | 9.87           |

|                                 | Virtex-6 LX760     | 204        | 0.53                         | 3.62           |

|                                 | 65nm standard cell | 694        | 19.28                        | 50.73          |

|                                 | Intel Core i7-960  | 67         | 0.35                         | 0.71           |

|                                 | Nvidia GTX285      | 250        | 1.41                         | 4.2            |

| E+ E (N. 1024)                  | Nvidia GTX480      | 453        | 1.08                         | 4.3            |

| Fast Fourier Transform (N=1024) | ATI R5870          | -          | -                            | -              |

|                                 | Virtex-6 LX760     | 380        | 0.99                         | 6.5            |

|                                 | 65nm standard cell | 952        | 239                          | 90             |

|                                 |                    | MOptions/s | (MOptions/s)/mm <sup>2</sup> | MOptions/J     |

|                                 | Intel Core i7-960  | 487        | 2.52                         | 4.88           |

|                                 | Nvidia GTX285      | 10756      | 60.72                        | 189            |

| DI LCLI                         | Nvidia GTX480      | -          | -                            | -              |

| Black-Scholes                   | ATI R5870          | -          | -                            | -              |

|                                 | Virtex-6 LX760     | 7800       | 20.26                        | 138            |

|                                 | 65nm standard cell | 25532      | 1719                         | 642.5          |

hardware suited for specific tasks [23, 101]. Recent commercial products that tightly couple GPUs and FPGAs with high-performance processors appear to support this trend [13, 55].

### 2.3 FPGA-Based Computing

The impressive raw capabilities of FPGAs have led to numerous projects and commercial efforts to develop computing platforms that incorporate FPGAs. Historically, FPGA-based reconfigurable computing systems existed either as a stand-alone board (e.g., [20]) or as a peripheral card on a computer system's low-performance I/O bus (e.g, [110]). To address bandwidth and latency concerns, newer commercial systems have begun to place FPGAs on the primary memory bus of multiprocessor systems. In particular, Cray [29] and SGI [90] first marketed computing systems that allowed a mixed population of FPGA-based processing modules and standard microprocessors on the shared-memory interconnect. Today, FPGA-based processing modules that plug into standard sockets of multiprocessor PCs or servers are widely available from SRC [85], DRC [40], XtremeData [117], and Nallatech [80, 72]. Many of the recent systems that integrate FPGAs onto the memory bus employ soft memory controllers that are implemented directly within the reconfigurable soft logic (e.g., BEE3 [32], Xilinx MIG [111]). Many of these soft implementations operate much slower

Figure 8: The Convey HC-1 Architecture (from www.convey.com).

than comparable hardwired implementations [28] (for example, the Virtex-6 LX240T FPGA on an ML605 platform [110] can only operate the lowest-rated DDR3 memory DIMM at 400MHz compared to the nominal clock speeds of 800MHz and above achieved by standard processors). For this reason, FPGA companies have begun integrating hardwired memory controllers that can operate at high speeds in future announced products [9, 116].

In the next subsections, we describe several existing systems that represent the state-of-the-art in FPGA-based computing. The CoRAM architecture proposed in this thesis assumes and builds upon external memory subsystems that closely resembles the commercial designs presented below.

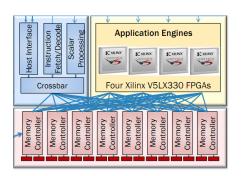

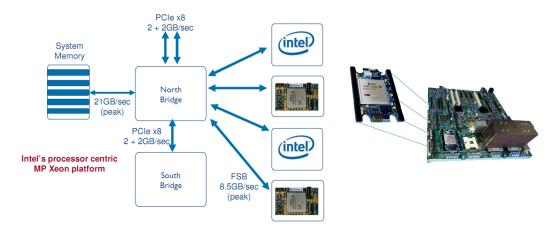

### 2.3.1 The Convey HC-1

The state-of-the-art in FPGA-based computing is best exemplified by the recent Convey HC-1 Computer [27], which marries several large FPGAs to a high-bandwidth memory subsystem. Figure 8 illustrates the system-level architecture of the HC-1, which couples four large Virtex-5 LX330 FPGAs to the front-side bus of an Intel-based processor system. A unique feature of the HC-1 is that each memory controller guarantees full coherency with the caches of the host processor<sup>3</sup>. This feature simplifies many aspects of application development, including eliminating the need to manually transfer data between the host processor and the FPGA. The Convey memory controllers further simplify this task by implementing translation lookaside tables (TLBs) that allow the FPGAs to access the same virtual memory address space shared by the host processor.

From the perspective of fabric, each individual FPGA sustains a peak 20GB/sec of memory bandwidth as long as the traffic is distributed evenly across eight independent off-chip memory

<sup>&</sup>lt;sup>3</sup>The memory controllers of the Convey are also implemented using smaller nearby FPGAs, although they cannot be re-configured by the user.

Figure 9: The Nallatech Xeon Accelerator Module (from www.nallatech.com).

controllers (for a combined total of 80GB/sec across four FPGAs). From the fabric's point of view, the HC-1 exposes 16 64b-wide load-store interfaces to partitioned addresses spaces within each FPGA. Each interface operates at a clock speed of 156 MHz, enabling 1.25GB/s of bandwidth per port. To achieve the maximum throughput of 20GB/sec per FPGA, applications must distribute their accesses sequentially and uniformly across the 16 load-store interfaces.

#### 2.3.2 Nallatech Accelerator Module

The Nallatech Xeon Accelerator Module developed by Intel and Xilinx is another example of a hybrid CPU-FPGA platform that allows mixing and matching of processors and FPGAs in a multi-socket backplane (see Figure 9). The Nallatech in-socket accelerator module allows adding a Virtex-5 LX330 FPGA onto the front-side-bus (FSB) of a conventional Intel-based multiprocessor system. A unique feature of the Nallatech is the ability to stack multiple FPGAs in a single processor socket with a lower footprint. The Nallatech also allows attachment of external SRAMs to individual FPGAs to extend the on-die memory capacity. In a Nallatech system, FPGAs are treated as slave devices that receive their tasks and computation state through the host Intel processor. From the perspective of fabric, each stand-alone adapter hosting one or more FPGAs can sustain a peak 8GB/sec of bandwidth to memory, which is limited by the 64-bit 1066MHz FSB interface. A round-trip read access to memory is approximately 700ns [72].

Figure 10: The BEE3 Platform (from [32]).

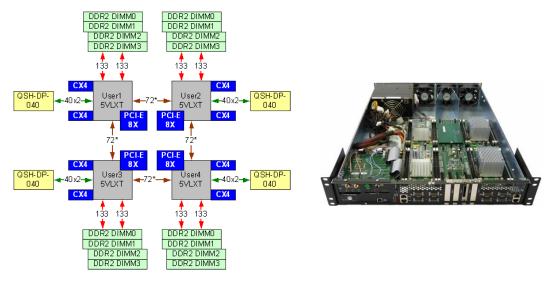

#### 2.3.3 Berkeley Emulation Engine 3 (BEE3)

The Berkeley Emulation Engine (BEE3) [32] exemplifies another class of FPGA-based computing platforms, which comprise multiple Virtex-5 LX155T FPGAs (or footprint-compatible parts) connected using high-speed links in a stand-alone board. In the BEE3, four FPGAs are arranged in a ring topology with high-speed links (8.0GB/s) between them. Host-to-FPGA or FPGA-to-FPGA communication is facilitated through multiple PCI-E 8X links.

A feature unique to the BEE3 is the distributed DRAMs local to each FPGA. From the perspective of fabric, each individual FPGA holds up to four private DDR2 DIMMs managed by two dual-channel memory controllers. Each DDR2 memory controller operates at 500MT/s, amounting to a total of 16GB/sec of off-chip memory bandwidth per FPGA [32].

### 2.4 The Need For A Standard Memory Architecture

Despite the impressive raw capabilities of general-purpose systems, the bifurcation of multiple platforms and devices creates a serious challenge for application writers. From the application writer's perspective, an application written in mind for one platform easily becomes obsolete once the system becomes out of fashion or if a platform change is desired. Applications are frequently either discarded or re-ported to newer systems but at the cost of substantial development effort and time. If we closely examine the systems above, a root problem can be traced to the fact that

applications perceive and access memory very differently across multiple platforms. The Convey HC-1 exposes a coherent global memory system through 16 local interfaces per FPGA; the BEE3 distributes its memory across multiple devices, with each device hosting two memory controllers; the Nallatech relies on the host processor to deliver the application state and memory.

In devising a standard memory architecture for FPGA-based computing, the objective of CoRAM is to abstract away the details of lower-level memory management and to enable portability and scalability of applications. To achieve portability and scalability, we devise several guiding design principle for CoRAM:

- An application should not be aware or coded to a specific protocol of a given low-level memory interface specific to a platform.

- An application should not be aware of the number of memory controllers or memory ports specific to a platform.

- Applications using a general-purpose abstraction should scale with ease and without modification to the core logic.

As will be introduced in Chapter 3, the CoRAM paradigm is designed to hide the underlying interface details by utilizing the embedded memories common in any FPGA as a logical portal into external memory (called the embedded CoRAM). Chapter 6 will later describe a style of microarchitecture for CoRAM devised in mind to support scaling up to thousands of CoRAMs per FPGA.

### **Chapter 3**

### **CoRAM Architecture**

Why would you want more than one machine language?

John von Neumann

This chapter motivates and introduces the Connected RAM (CoRAM) architecture, which embodies a paradigm for how users perceive and manage the computational and memory resources of an FPGA-based computing device. Much like how conventional general-purpose ISAs abstract away the lower-level details of memory hierarchy through standard loads and stores, the CoRAM architecture provides a highly distributed programming interface for managing the on- and off-chip memory resources of an FPGA. This chapter begins first by describing how CoRAM-based FPGAs "fit" into the computational stack of conventional systems. Following a discussion of key assumptions, the architectural ideas behind CoRAM are explained and justified.

### 3.1 CoRAM System Organization and Assumptions

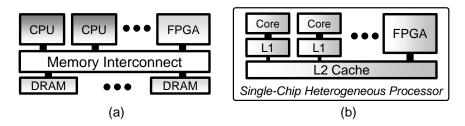

The CoRAM architecture assumes the co-existence of FPGA-based computing devices along-side general-purpose processors in the context of a shared memory multiprocessor system (see Figure 11). The CoRAM architecture assumes that reconfigurable logic resources will exist either as discrete FPGA devices on a multiprocessor memory interconnect or integrated as fabric into a single-chip heterogeneous multicore. In this context, the FPGA-based components operate as peer computing devices that can independently fetch from and store to main memory.

Figure 11: Assumed System Context.

Figure 12: CoRAM Memory Architecture.

Regardless of the configuration, it is assumed that memory interfaces for loading from and storing to a global linear address space will exist at the boundaries of the reconfigurable logic (referred as edge memory in this thesis). These implementation-specific edge memory interfaces could be realized as dedicated memory/bus controllers or even coherent cache interfaces to a shared on-die memory hierarchy. Like commercial systems available today (e.g., Convey Computer [27]), reconfigurable logic devices can directly access the same virtual address space of general purpose processors (e.g., by introducing MMUs at the boundaries of fabric). The combined integration of virtual memory and direct access to the memory bus allows applications to be efficiently and easily partitioned across general-purpose processors and FPGAs, while leveraging the unique strengths of each respective device. A nearby processor is useful for handling tasks not well-suited to FPGAs—e.g., providing the OS environment, executing irregular sequential tasks (e.g., system calls), and initializing the memory contents of an application prior to its execution on the FPGA.

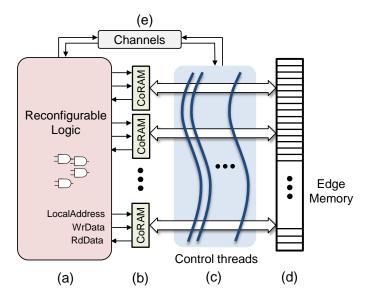

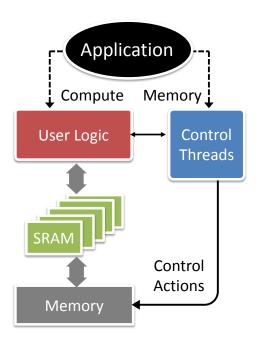

### 3.2 The CoRAM Program Model

The CoRAM programming model fundamentally embodies three independent ideas: (1) enforced separation of concerns between computation and memory management, (2) the use of embedded SRAMs as standard interfaces for accessing on- and off-chip memory, and (3) the use of software control threads as a portable memory management interface. Figure 12 offers a conceptual view of how applications are decomposed when mapped into reconfigurable logic with CoRAM support. The core logic component shown in Figure 12a is a collection of LUT and sequential resources (e.g., flip-flops) used to host the state and logic of the algorithmic kernels of a user application. It is important to note that the CoRAM programming model preserves the hardware-centric view for developing core logic and places no fundamental restriction on the description language used. For portability reasons, the only requirement is that core logic is never permitted to directly interface with off-chip I/O pins, access memory interfaces, or be aware of platform-specific details.

An application hosted in this environment is only allowed to interact with external memory and I/O devices through a collection of specialized, distributed embedded SRAMs called CoRAMs, as diagrammed in Figure 12b. Much like current FPGA memory architectures, the embedded CoRAMs serve the same role that of conventional FPGA SRAMs [81]—(1) they provide the application with many independent banks of on-chip storage, (2) they present a simple wire-level SRAM interface to the core logic with deterministic access times, (3) they are spatially distributed, and (4) they provide high aggregate on-chip bandwidth on the order of terabytes per second. Like traditional FPGA-based embedded SRAMs, CoRAMs can be further composed together and configured with flexible aspect ratios (e.g., 16384x1, 4096x32). CoRAMs, however, deviate drastically from conventional SRAMs in the sense that the data contents of individual CoRAMs are actively managed by finite state machines called "control threads" as shown in Figure 12c.

#### 3.2.1 Software Control Threads

The heart of the CoRAM memory architecture is the **software control thread**. Software control threads form a fabric-distributed collection of logical, asynchronous finite state machines for managing and mediating the data transfers between embedded CoRAMs instantiated by an application and the edge memory interfaces. At a high level, control threads can be viewed as an abstract,

general-purpose mechanism for prefetching an application's required data from the edge memory interface to the fabric-distributed CoRAMs. At the lowest level, control thread programs describe an ordered sequence of memory commands directed by control flow. Under the CoRAM architecture, the application writer relies solely on software control threads to access external main memory and I/O over the course of computation. Each CoRAM is managed by at most a single control thread, although a single control thread could manage multiple CoRAMs.

Control threads and the core logic of an application are peer entities that interact over low-latency, bidirectional channels (see Figure 12e). In the CoRAM architecture, channels are built out of FIFOs and registers that allow control threads and core logic to exchange information when necessary. A control thread maintains local state to facilitate its sequencing activities and issues transfer commands to the edge memory interface on behalf of the application; upon completion, the control thread informs the core logic by channels when data within the CoRAMs are ready to be accessed through their locally-addressed SRAM interfaces.

Control Actions. To utilize memory, an FPGA application instantiates one or more embedded CoRAMs to be used as a logical "portal" into external memory. To "program" the embedded CoRAMs, an associated software control thread invokes a predefined collection of memory and communication primitives called **control actions**. Control actions constitute a memory management interface that allows control threads to mediate accesses between main memory and the CoRAMs embedded throughout the fabric. At the most basic level, a control thread describes a sequence of control actions executed over the course of a program. In general, a control thread issues control actions along a dynamic sequence that can include cycles and conditional paths.

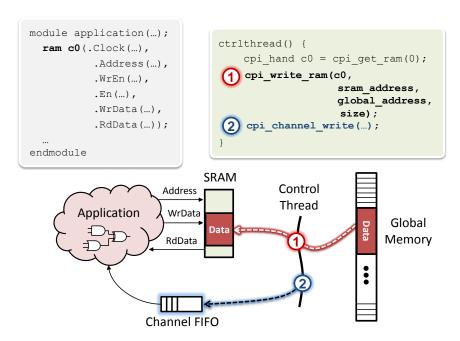

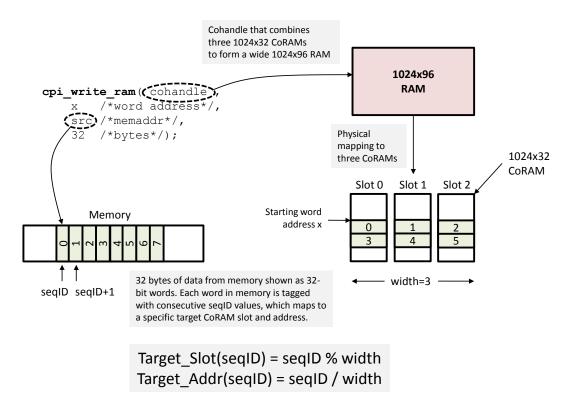

**Example.** To illustrate how control threads and control actions operate, Figure 13 shows how a user would (1) instantiate an embedded CoRAM as a Verilog black-box module within their application, and (2) program a corresponding control thread to read a single data word from edge memory into the CoRAM. The control thread program shown in Figure 13 (right) first acquires a special object called the co-handle and passes it into a *cpi\_write\_ram*<sup>1</sup> control action, which performs a 4-byte memory transfer from the edge memory address space to the CoRAM embedded blocks referred to by the co-handle. To inform the application when the data is ready to be accessed for

<sup>&</sup>lt;sup>1</sup>cpi = CoRAM Programming Interface.

Figure 13: Example Usage of CoRAM.

computation, the control thread issues a token over a bidirectional channel to the core logic using the *cpi\_channel\_write* control action.

**Discussion.** As illustrated in the above example, a control thread is simply a high-level description of an application's memory access pattern. The control thread description deliberately presents a simple abstraction to the user but is flexible enough to be re-targeted to different hardware implementations. The example also shows that a complete "application" written for the CoRAM program model is defined as both the core logic component written in an HDL of choice along with the requisite control thread programs written in software. Fundamentally, CoRAM requires inter-operation with existing hardware description languages such as Verilog, which serve the complementary role of describing the computational or processing logic components of an application (for example, the design of a highly tuned floating point functional unit). The decision to allow arbitrary hardware description languages is motivated by the need to preserve a hardware-centric view of fabric to the application writer. In today's FPGAs, a diversity of approaches exist to describe FPGA-based applications in an efficient manner—ranging from high-level synthesis languages (e.g., Bluespec, C) down to hand-tuned IP libraries (e.g., Xilinx Coregen). A fundamental goal of CoRAM is to not restrict the user to a specific style of implementation when developing core logic.

Figure 14: Memory Control Action.

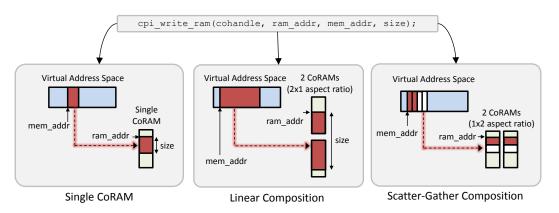

**Embedded CoRAM Composition.** The CoRAM programming model fundamentally exposes a hardware-centric view of the FPGA that allows the user to customize data partitioning and manage the port and bandwidth usage of the embedded CoRAMs. A unique feature of CoRAM is the ability to compose multiple embedded CoRAMs to form logical portals into memory with arbitrary aspect ratios. For instance, the control action shown below is contextually interpreted based on the aspect ratio of the memories referred to by the cohandle object:

Figure 14 gives illustrated examples of how the above control action would behave differently depending on the composition style and aspect ratios of the memories. A linear composition, for example, would concatenate the local addresses of multiple embedded CoRAMs to form a deeper memory, while a scatter-gather composition would create wider memories. When executing the control action, the sequential data streaming from memory would be divided into words that match the desired composition. This feature of CoRAM gives FPGA application writers the ability to customize the interfaces of memories to their application's needs; meanwhile, the CoRAM memory management interface automatically handles the data transfer and layout of data that matches the customization.

#### 3.2.2 How Does CoRAM Solve The Portability Challenge?

The basic challenge of portability arises from the fact that today's FPGAs require an all-to-all mapping from high-level applications down to specific devices and platforms. In the worst case, a full cross-product of implementations are needed. The root of this problem stems from the fact that conventional memory subsystems of FPGAs expose very low-level interfaces connected to external memory devices such as DRAM or a processor memory bus. Users are often required to familiarize with or even devise the protocols needed to interface with a myriad of vendor-specific specifications and devices.

Rather than forcing designers or compute vendors to target their applications and libraries to specific protocols, the software control thread paradigm of CoRAM fundamentally replaces the low-level interfaces with an **intermediate machine abstraction** that both application designers and system vendors can agree upon. The intermediate machine abstraction must be flexible and easy to use while exposing sufficient intent by the user such that efficient hardware implementations can be facilitated.

The software-based control threads serve this goal by raising the level of abstraction of an application's memory access pattern in a stylized and portable manner. Yet, at the same time, the software control threads along with the embedded CoRAM instantiations are high-level, parallelized descriptions of an application that can be efficiently re-targeted to different FPGAs and platforms. As will be shown quantitatively in Chapter 8—from a performance perspective, expressing control threads in a high level language does not become a limiting factor to performance because most time is either spent waiting for memory responses or for computation to progress. Chapter 8 will also demonstrate why CoRAM is portable by automatically retargeting applications to different hardware configurations scaled across multiple technology nodes.

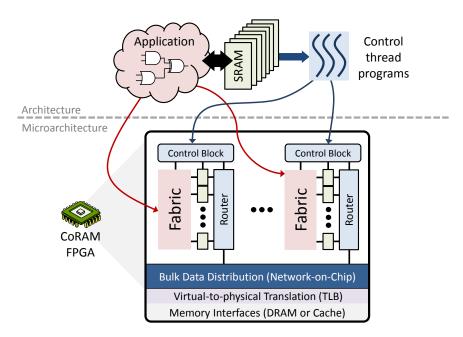

#### 3.2.3 CoRAM Microarchitecture

The dual software and HDL descriptions that constitute a CoRAM-based application must ultimately be synthesized and mapped into physical hardware. Like any "standard" architecture, a deliberate separation exists between what the application writer perceives and that of the physical mechanisms that lay beneath the abstraction. To fill in the gulf that separates a high-level con-

Figure 15: Beneath the CoRAM Programming Abstraction.

trol thread program and actual hardware, synthesis tools must translate the memory access patterns described by a control thread into hardware mechanisms of an independent device or platform.

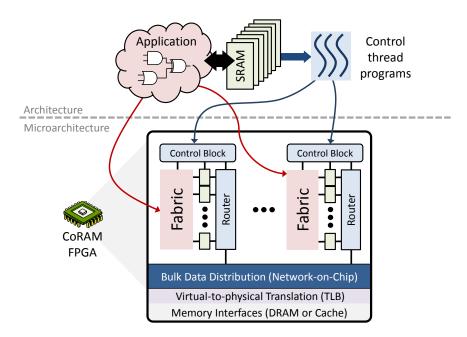

Figure 31 illustrates the physical archetype of a CoRAM-based FPGA proposed in this thesis consisting of distributed islands of reconfigurable logic and embedded CoRAMs. The control threads written by an application writer are mapped down into physical control blocks co-located to various embedded CoRAMs throughout the fabric. Control blocks are responsible for interpreting and executing the control thread programs as well as generating memory requests and handling responses through a general-purpose network-on-chip (NoC). The NoC fundamentally provides connectivity and bandwidth between the CoRAM endpoints and the edge memory interfaces embedded throughout the FPGA. At the very edge of the fabric lies the memory subsystem component. Multiple memory controllers and/or bus interfaces are present to manage the data transfers between the edge of the FPGA and external storage devices such as DRAM or SRAM. Above the memory interfaces, optional last-level caches provide a bridge into the FPGA, which can be used to filter unnecessary accesses to memory. Finally, translation lookaside tables above the caches may exist in order to facilitate accesses to a virtual memory address space compliant with other peer computing devices situated on the shared memory bus.

A recurring theme echoed throughout the remainder of this thesis will be the question of hard

**versus soft**—that is, which sub-components required in the CoRAM microarchitecture merit implementation in existing FPGAs today, and what features merit "hardening" into future FPGAs designed for computing. The microarchitecture design space of Figure 31 will be explored extensively in Chapter 6.

### 3.3 CoRAM versus Alternative Approaches

In this section, we compare and contrast the CoRAM program model to alternative memory architecture choices. The objective of this discussion is to elaborate upon the design choices of the CoRAM architecture and to evaluate it against alternative styles that could also potentially satisfy the desired goals of portability and simplified FPGA memory management.

Standardized Memory Interfaces. A hypothetical way to standardize the memory architecture of the FPGA is to restrict all interactions to off-chip memory and I/O through uniform load-store interfaces between the edges of the fabric and the off-chip interfaces. In this case, FPGA design vendors who adopt the same standard must agree upon a particular convention and protocol for accessing the memory or bus controllers of off-chip interfaces. In this setting, the application writer is still responsible for sharing and multiplexing the off-chip memory resources among the multiple clients that require access to memory. The application writer must also implement manually within soft logic the mechanisms for transferring data between the now-standardized edge memory interfaces and the on-die SRAMs.

**In-Fabric Memory Hierarchies.** A natural extension of the previous approach is to distribute the standardized load-store interfaces to within the fabric itself and to provide a dedicated memory port to any client that requires memory. A distributed load-store interface requires the underlying hardware to facilitate the movement and buffering of data between external memory and the client that issued the request. The LEAP scratchpad concept [10] is a soft-logic demonstration of this approach where load-store interfaces can be instantiated on-demand by multiple clients in an application.

Behind the distributed load-store interfaces, the LEAP scratchpad concept further employs a processor-like multi-level cache hierarchy built out of embedded SRAMs within the fabric of the FPGA (with a parameterizable backing store made up of DRAM and/or on-board SRAMs). LEAP

supports the data distribution automatically by instantiating an on-chip network along with parameterized levels of caching to reduce latency and bandwidth between the distributed clients and memory. The use of caching further virtualizes the capacity of on-die FPGA memory from the perspective of the application. To preserve portability of applications across different LEAP implementations, the control logic that manages the accesses of on- or off-chip memory must conform to a timing-insensitive request-response protocol [10]. The abstraction presented by LEAP could hypothetically be implemented in a future FPGA with dedicated cache controllers and arrays embedded within the fabric.

CoRAM versus In-Fabric Memory Hierarchy. The CoRAM architecture differs from an in-fabric memory hierarchy by deliberately exposing control of the on-die SRAMs in a way that preserves the hardware-centric view of FPGA memory. As in a conventional FPGA, the application writer still perceives many independent banks of memory, where each bank exposes a private address space and a single-cycle access latency. This hardware-centric view gives the application writer the liberty to perform custom data partitioning across multiple banks, implement composition of multiple SRAMs with flexible aspect ratios that match the application's requirements, and maintain guaranteed control over usage of SRAM port bandwidth and latency. An in-fabric memory hierarchy could hypothetically support similar optimizations through application-level hints to the memory subsystem; however, a demand-based memory hierarchy with automatic management of data between cache levels has a more restricted timing-insensitive interface and semantic that limits the ability of the user to precisely control data placement and port usage of the underlying on-chip SRAMs.

What CoRAM adds to the conventional SRAM interface is a standard way of simplifying and automating a frequent pattern found in FPGA-based computing, which is the movement of data between off-chip interfaces and their ultimate destinations, the on-die SRAMs. Unlike an in-fabric memory hierarchy, the CoRAM architecture resembles a "close-to-metal" ISA for the FPGA that encompasses low-level memory management primitives that can in turn be used to form higher-level services and semantics. For example, embedded CoRAMs and control threads can be used in conjunction with reconfigurable logic to provide the illusion of a timing-insensitive, cache-like interface. This style of layering deliberately decouples the FPGA architect or platform builder from

having to implement higher levels of abstraction such as caches or memory streams. Instead, implementations are only required to conform to a simple set of requirements laid out by the CoRAM architecture specification, as will be discussed in detail in Chapter 4. As shown later in Chapter 8, an FPGA that directly implements the minimum set of features required by CoRAM allows applications to achieve near-ideal performance potential while incurring modest overheads in implementation cost.

CoRAM Control Threads versus Wire-Level Interfaces. A unique feature to CoRAM is the software control thread, which is an orthogonal architectural feature with respect to the previously discussed memory systems. In principle, a variant of CoRAM could allow the user to combine the control thread and core logic in a monotholic RTL application without enforcing separation of compute and memory. In this case, the user would describe control logic that issues control actions over a wire-level interface in RTL. As mentioned earlier, the rationale for using software is to avoid having the designer implement address generation using low-level RTL languages. The software abstraction allows the designer to naturally describe memory accesses as an untimed sequence of commands.

In some cases, applications may exhibit a tight coupling between the application data itself and the logic used to generate requests to memory. Algorithms such as graph traversal and sparse multiplication exhibit memory accesses that are memory data dependent. As will be shown in our examples in Chapter 5, the lightweight control threads of CoRAM communicate through high-bandwidth, low-latency channels to the core logic. This capability allows data-dependent memory accesses to be supported efficiently, as will be demonstrated in the Sparse Matrix-Vector Multiplication case study of Chapter 5.

CoRAM versus Scratchpad Memories. Beyond the systems described thus far, the style of memory management in CoRAM closely resembles the concept of software-based Scratchpad Memories (SPM) [16]. SPMs are typically implemented in specialized or power-constrained settings such as embedded systems, DSPs, and GPGPUs, which expose software-level control over the on-die memories. The control threads of CoRAM fulfill a similar role by allowing explicit and controlled data movements between global memory and the remote scratchpads (i.e., CoRAMs) distributed throughout the fabric (see Figure 16).

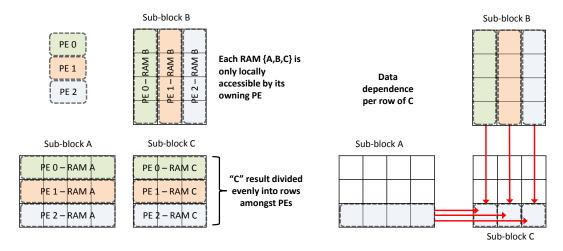

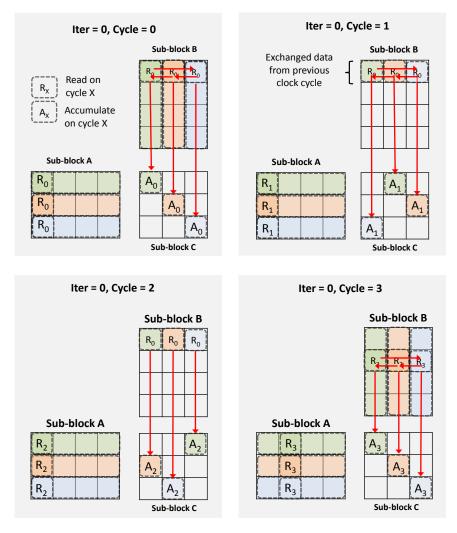

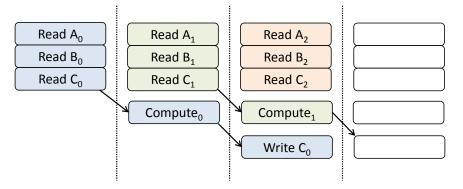

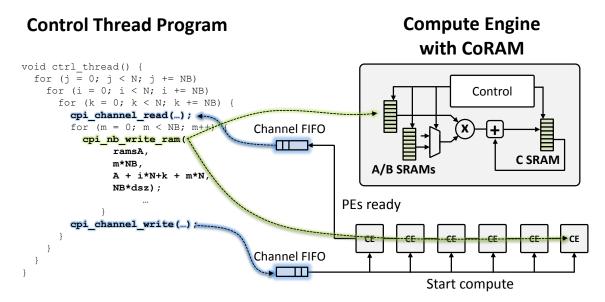

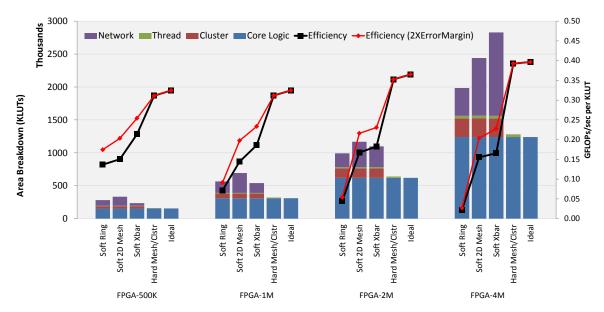

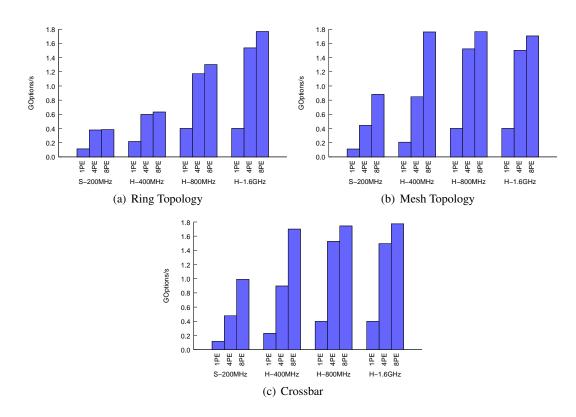

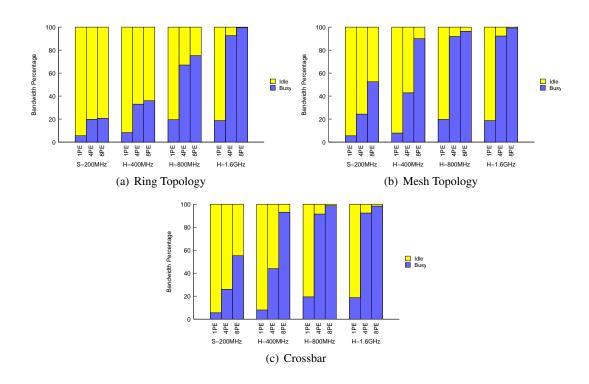

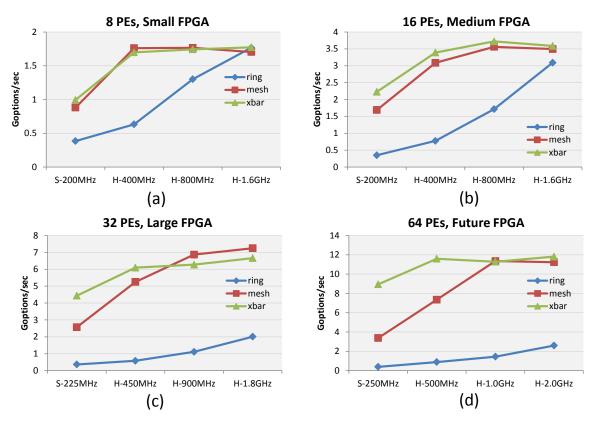

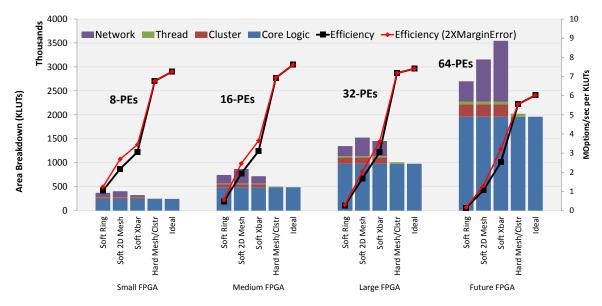

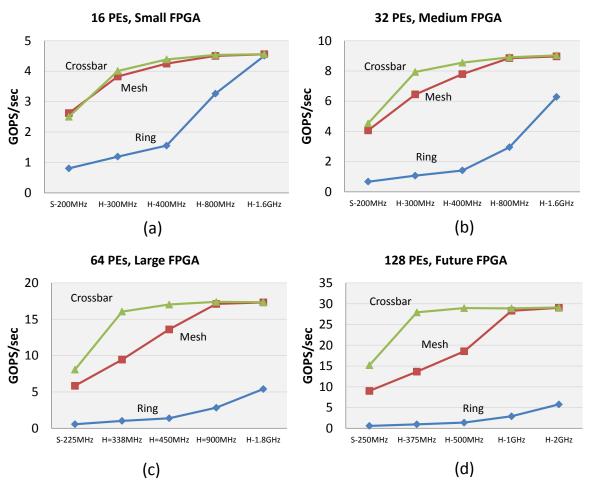

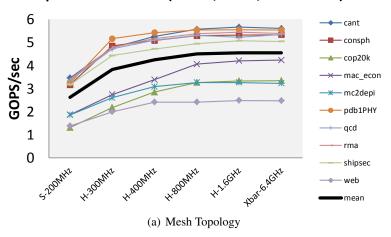

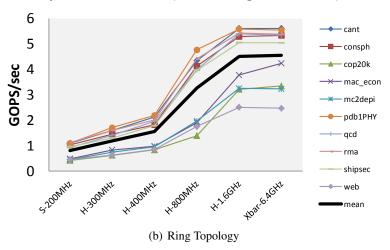

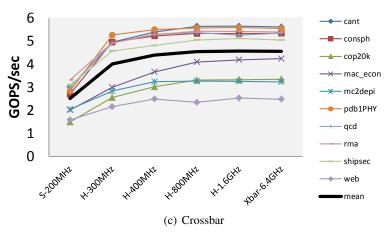

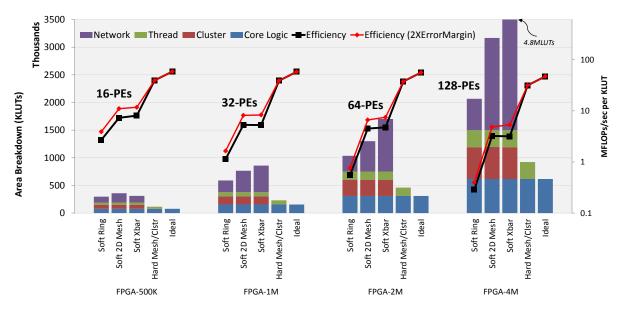

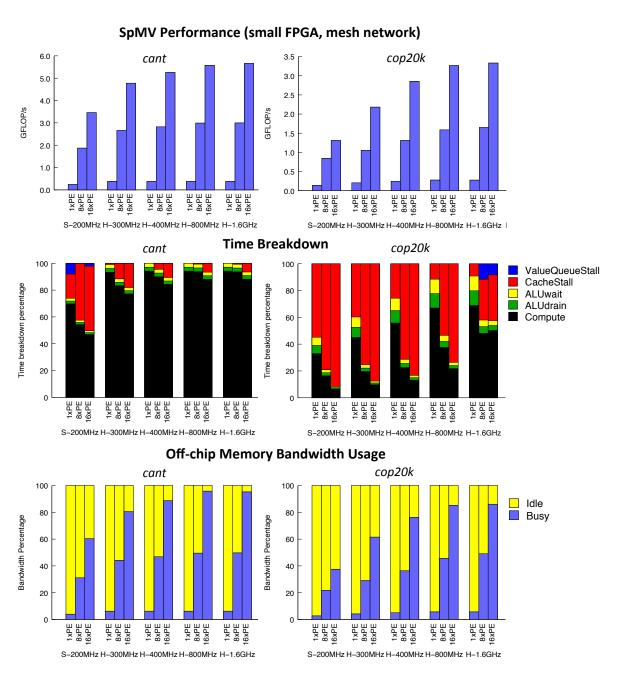

There are several differences between SPM and CoRAM. In CoRAM, the consumer and producer of the scratchpad is not a fixed-width processor but is instead a reconfigurable fabric that requires a different style of interface and semantics. CoRAM further separates the computation into asynchronous memory threads and reconfigurable core logic—whereas in a processor-based system, a single thread of control is often the case. In systems with SPM, memory must usually be managed carefully to avoid introducing bottlenecks in the computation. As will be shown in Chapter 5, the FPGA-based applications tend to avoid this bottleneck through the asynchronous execution of core logic and software control threads.