Image: Construct of the second state of the second stat

Electrical & Computer

CMU 18-447 S'09 L16-7 © 2009 J. C. Hoe

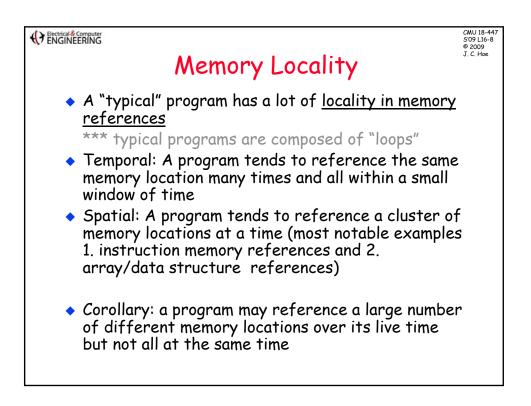

## Locality

- One's recent past is a very good predictor of his/her near future.

- Temporal Locality: If you just did something, it is very likely that you will do the same thing again soon

- since you are here today, there is a good chance you will be here again and again regularly

- inverse is also true

- Spatial Locality: If you just did something, it is very likely you will do something similar/related

- every time I find you in this room, you are probably sitting in the same seat

- you are probably sitting near the same people

CMU 18-447 S'09 L16-9 © 2009 J. C. Hoe

#### Memoization

- If something is expensive to compute, you might want to remember the answer for a while, just in case you will need the same answer again

- Memoization needs locality to work effectively

- Without locality

- storing a large number of different answers (many of which never reused)

- storing a very large number of answers and later locating an answer on demand can be more expensive than recomputing it

- With locality

- store only small number of the most frequently used answers avoids most recomputations

- the same answer gets reused many, many times!

CMU 18-447 S'09 L16-11 © 2009 J. C. Hoe

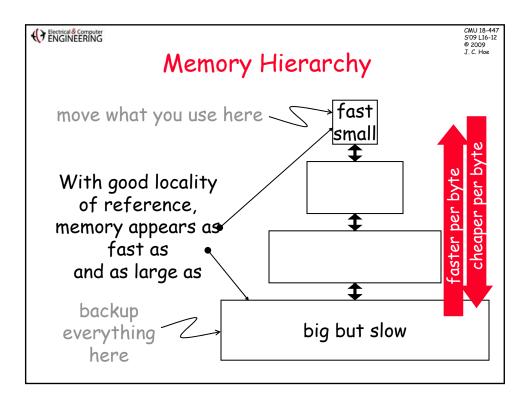

## Putting the principles to work

# Aside: Why is DRAM slow?

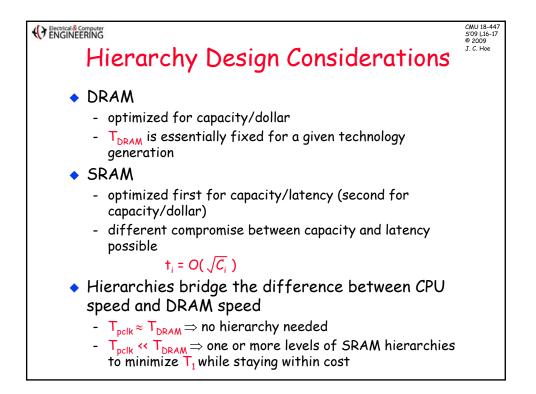

DRAM fabrication at the forefront of VLSI technology nodes, but scales with Moore's law in capacity and cost, not speed

- Between 1980 ~ 2004 DRAM

- 64K bit  $\rightarrow$  1024M bit (exponential ~55% annual)

- 250ns → 50ns (linear)

But, remember, this is a very deliberate choice. We can "engineer" faster DRAM if we needed to

- Memory capacity needs to grow linearly with CPU speed to keep a balanced system - Amdahl

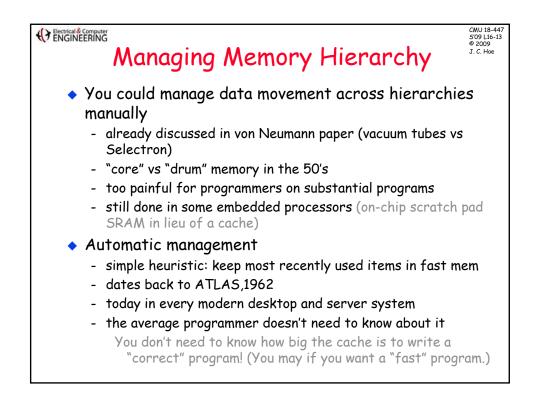

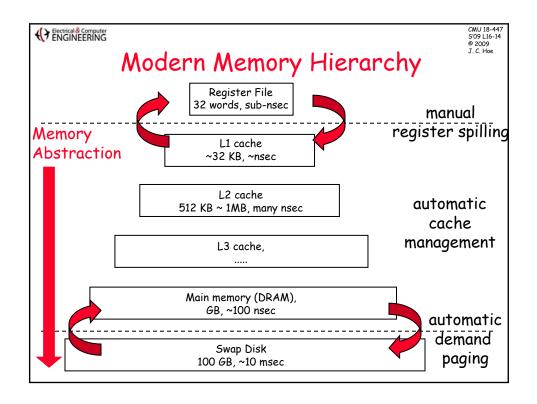

- DRAM/processor speed difference reconciled through memory hierarchies (L1, L2, L3, .....)

- L2 became common place in the 90s

- L3 becoming common place in the OOs

Electrical & Computer

CMU 18-447 S'09 L16-23 © 2009 J. C. Hoe

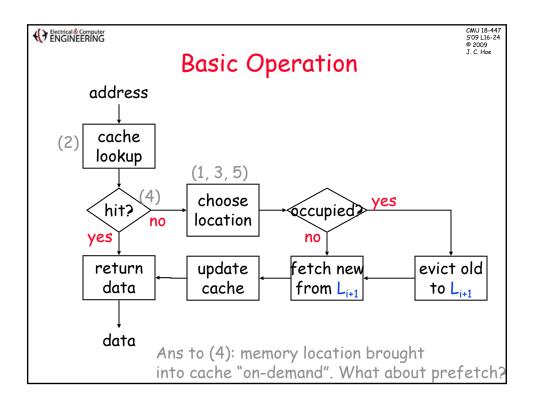

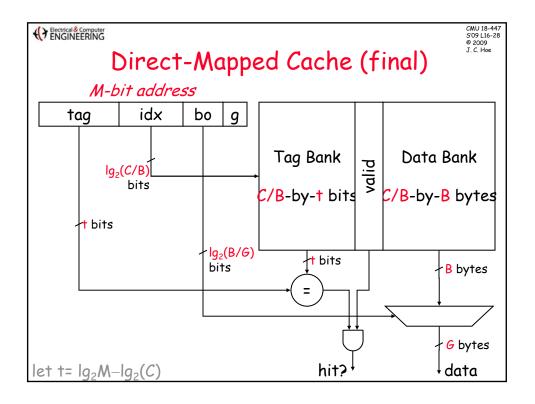

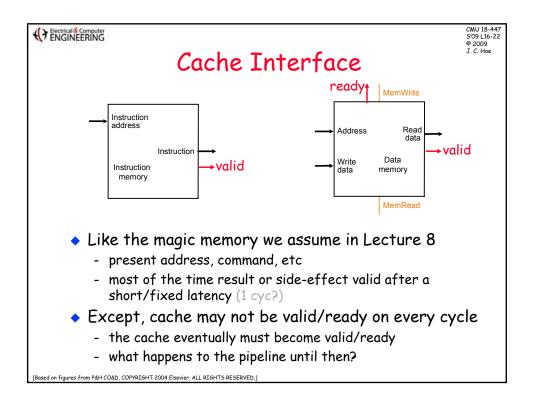

### The problem

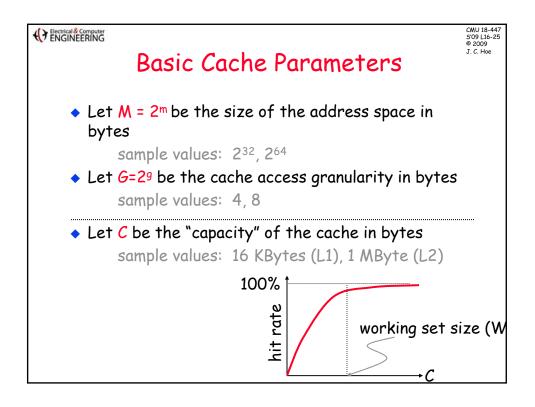

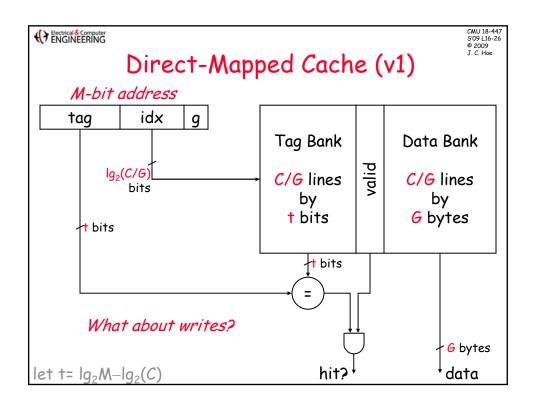

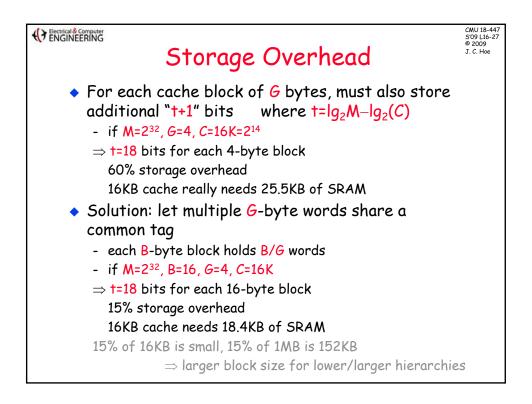

- Potentially M=2<sup>m</sup> bytes of memory, how to keep the most frequently used ones in C bytes of fast storage where C << M</li>

- Basic issues (intertwined)

- (1) where to "cache" a memory location?

- (2) how to find a cached memory location?

- (3) granularity of management: large, small, uniform?

- (4) when to bring a memory location into cache?

- (5) which cached memory location to evict to free-up space?

- Optimizations